一种高效ECT系统的制作方法

一种高效ect系统

技术领域

1.本实用新型属于etc技术领域,尤其是涉及一种高效ect系统。

背景技术:

2.ect(电容层析成像)技术是根据被测物质各相具有不同的介电常数,当各相组分分布或浓度分布发生变化时,将引起混合流体等价介电常数发生变化,从而使测量电极对间的电容值发生变化,在此基础上,利用相应的图像重建算法重建被测物场的介电分布图。ect技术已被应用于气液两相流空隙率测量及流型识别、流化床气固两相浓度分布可视化、气力输送、火焰可视化、冻土水分迁移过程的可视化等多个领域。

3.完整的ect系统由电容阵列传感器、测量系统和成像计算机组成。但现有技术中的ect的测量系统性能较差,占用逻辑资源多,执行速度慢,影响了整个ect系统的性能。

技术实现要素:

4.本实用新型要解决的问题是提供一种高效ect系统。

5.为解决上述技术问题,本实用新型采用的技术方案是:一种高效ect系统,包括测量系统,所述测量系统包括fpga模块,所述fpga模块内部设置有嵌入式处理器、dds模块和数字psd模块,该fpga模块还设置有接口,所述接口包括gpio接口、dac接口、adcs接口和从属fifo接口,所述dds模块输出端分别与dac接口和数字psd模块相连,所述数字psd模块输出端与从属fifo接口相连,该数字psd模块输入端与adcs接口输出端相连。

6.所述dac接口与dac相连,所述adcs接口与adcs相连,所述从属fifo接口与usb内的从属fifo相连,usb通过usb接口与主机相连。

7.传感器通过接口与测量系统相连。

8.所述fpga模块为spartan

‑

3/6fpga。

9.所述嵌入式处理器为microblaze。

10.所述usb为cypress ez

‑

usb。

11.由于采用上述技术方案,本实用新型spartan

‑

3/6fpga模块内部的嵌入式处理器—microblaze,只需占用很少逻辑资源,执行速度却可达到40mips以上。

12.本实用新型的优势是将嵌入式处理器与fpga模块结合起来,获得较以往更高的整体性能,因为通过各种接口与外界连接,需要较高的处理速度,通过fpga模块本身的可编程逻辑性能可实现硬件加速的效果,而系统中的通道切换等操作是典型的顺序执行方式,fpga模块本身的可编程逻辑性能是并行处理结构,因此需要由嵌入式处理器完成,因此将嵌入式处理器与fpga模块结合使用应用于ect的测量系统,可以达到提高整个系统性能的目的。

附图说明

13.下面通过参考附图并结合实例具体地描述本实用新型,本实用新型的优点和实现

方式将会更加明显,其中附图所示内容仅用于对本实用新型的解释说明,而不构成对本实用新型的任何意义上的限制,在附图中:

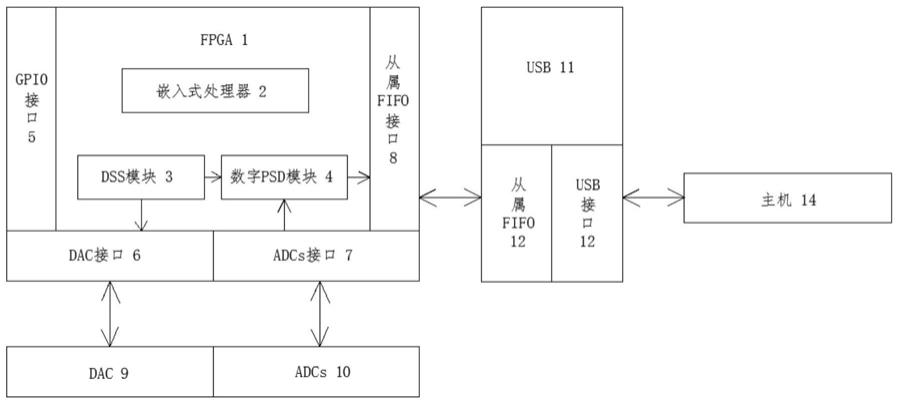

14.图1是本实用新型的结构框图

15.图中:

16.1、fpga模块

ꢀꢀꢀꢀꢀꢀꢀ

2、嵌入式处理器

ꢀꢀꢀꢀ

3、dds模块

17.4、数字psd模块

ꢀꢀꢀꢀ

5、gpio接口

ꢀꢀꢀꢀꢀꢀꢀꢀ

6、dac接口

18.7、adcs接口

ꢀꢀꢀꢀꢀꢀꢀ

8、从属fifo接口

ꢀꢀꢀꢀ

9、dac

19.10、adcs

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

11、usb

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

12、从属fifo

20.13、usb接口

ꢀꢀꢀꢀꢀꢀꢀ

14、主机

具体实施方式

21.如图1所示,本实用新型一种高效ect系统,包括测量系统,测量系统包括fpga模块1,fpga模块1内部设置有嵌入式处理器2、dds模块3和数字psd模块4,该fpga模块1还设置有接口,接口包括gpio接口5、dac接口6、adcs接口7和从属fifo接口8,dds模块3输出端分别与dac接口6和数字psd模块4相连,数字psd模块4输出端与从属fifo接口8相连,该数字psd模块4输入端与adcs接口7输出端相连,dac接口6与dac 9相连,adcs接口7与adcs 10相连,从属fifo接口8与usb11内的从属fifo 12相连,usb 11通过usb接口13与主机14相连,传感器通过接口与测量系统相连,fpga模块1为spartan

‑

3/6fpga,嵌入式处理器2为microblaze,usb 11为cypress ez

‑

usb。

22.本实用新型spartan

‑

3/6fpga模块内部的嵌入式处理器—microblaze,只需占用很少逻辑资源,执行速度却可达到40mips以上。

23.本实用新型将嵌入式处理器与fpga模块结合起来,获得较以往更高的整体性能,因为通过各种接口与外界连接,需要较高的处理速度,通过fpga模块本身的可编程逻辑性能可实现硬件加速的效果,而系统中的通道切换等操作是典型的顺序执行方式,fpga模块本身的可编程逻辑性能是并行处理结构,因此需要由嵌入式处理器完成,因此将嵌入式处理器与fpga模块结合使用应用于ect的测量系统,可以达到提高整个系统性能的目的。

24.以上对本实用新型的实施例进行了详细说明,但所述内容仅为本实用新型的较佳实施例,不能被认为用于限定本实用新型的实施范围。凡依本实用新型范围所作的均等变化与改进等,均应仍归属于本专利涵盖范围之内。

技术特征:

1.一种高效ect系统,其特征在于:包括测量系统,所述测量系统包括fpga模块,所述fpga模块内部设置有嵌入式处理器、dds模块和数字psd模块,该fpga模块还设置有接口,所述接口包括gpio接口、dac接口、adcs接口和从属fifo接口,所述dds模块输出端分别与dac接口和数字psd模块相连,所述数字psd模块输出端与从属fifo接口相连,该数字psd模块输入端与adcs接口输出端相连。2.根据权利要求1所述的高效ect系统,其特征在于:所述dac接口与dac相连,所述adcs接口与adcs相连,所述从属fifo接口与usb内的从属fifo相连,usb通过usb接口与主机相连。3.根据权利要求1所述的高效ect系统,其特征在于:传感器通过接口与测量系统相连。4.根据权利要求1所述的高效ect系统,其特征在于:所述fpga模块为spartan

‑

3/6fpga。5.根据权利要求1所述的高效ect系统,其特征在于:所述嵌入式处理器为microblaze。6.根据权利要求2所述的高效ect系统,其特征在于:所述usb为cypress ez

‑

usb。

技术总结

本实用新型提供一种高效ECT系统,属于ETC技术领域,包括测量系统,测量系统包括FPGA模块,FPGA模块内部设置有嵌入式处理器、DDS模块和数字PSD模块,该FPGA模块还设置有接口,接口包括GPIO接口、DAC接口、ADCs接口和从属FIFO接口,DDS模块输出端分别与DAC接口和数字PSD模块相连,数字PSD模块输出端与从属FIFO接口相连,该数字PSD模块输入端与ADCs接口输出端相连。因为通过各种接口与外界连接,需要较高的处理速度,通过FPGA模块本身的可编程逻辑性能可实现硬件加速的效果,而系统中的通道切换等操作是典型的顺序执行方式,因此需要由嵌入式处理器完成,将嵌入式处理器与FPGA模块结合使用应用于ECT的测量系统,可以达到提高整个系统性能的目的。统性能的目的。统性能的目的。

技术研发人员:张彦醒

受保护的技术使用者:天津有仪科技有限公司

技术研发日:2021.04.06

技术公布日:2021/11/28

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1