一种解决SRIO接口阻塞的方法与流程

一种解决srio接口阻塞的方法

技术领域

1.本发明涉及高速接口通信技术领域,具体为一种解决srio接口阻塞的方法。

背景技术:

2.在异构计算的硬件架构设计中,cpu+fpga是常用的一种硬件架构方式,在两者需要高速交换数据的场景,srio较为常见的一种通信接口。由于cpu与fpga上电时间、复位处理的差异,在使用过程中会偶发srio接口阻塞无法恢复,进而无法通信的问题。对于硬件设计上采用slave-serial、slave-selectmap模式进行配置的fpga,可以通过重新配置解决该问题;然而对于master-serial、master-selectmap、master-spi、master-bpi方式启动的fpga,由于在硬件板卡上电时fpga只会配置启动一次,则只能通过断电重启进行重配置。在某些应用场景,是不容许设备断电的,这就需要解决在不断电的情况下,让fpga重新配置一遍内部逻辑数据。本方法通过利用fpga的内部原语icap的使用,解决了在master配置模式,不断电的动态配置fpga的问题。

技术实现要素:

3.(一)解决的技术问题针对现有技术的不足,本发明提供了一种解决srio接口阻塞的方法。

4.(二)技术方案为实现上述目的,本发明提供如下技术方案:一种解决srio接口阻塞的方法,包括以下步骤:第一步:cpu通过本地总线(bus)轮询和fpga间的srio接口状态;第二步:fpga在接收到cpu发送过来的复位信号后,对内部逻辑进行复位;第三步:fpga接收到重配置指令后,通过icap发送iprog指令进行重新配置。

5.优选的,所述第一步中一旦发现srio接口出现了阻塞的情况,首先发送软复位信号至fpga,同时对自身srio接口进行复位。

6.优选的,所述第一步中一旦发现srio接口出现了阻塞的情况,首先发送软复位信号至fpga,同时对自身srio接口进行复位。

7.优选的,所述第三步中irpog发送的配置数据的warm boot start address填写需要重配置的逻辑在flash中存储的地址即可。

8.优选的,所述fpga采用master模式进行配置时,上电启动后默认从flash的0地址处读取数据。所以我们在flash的0地址处烧写的配置bit文件应包含icap2原语。

9.(三)有益效果与现有技术相比,本发明提供了一种解决srio接口阻塞的方法,具备以下有益效果:1、该解决srio接口阻塞的方法,在master配置模式的硬件设计中,设备在不断电的情况下,重新配置fpga,解决cpu与fpga之间srio接口阻塞的问题。

10.2、该解决srio接口阻塞的方法,解决srio接口阻塞的问题时,只需将icap2_top模块中的boot_addr改成0x0000_0000,当cpu监测到对端srio接口阻塞后,通知fpga产生复位信号给icap2_top模块,即可在无需断电情况下完成fpga的重新配置,进而解决接口阻塞问题。

11.3、该解决srio接口阻塞的方法,捕捉外部输入异步复位信号,对主动方式启动的fpga进行重配置,进而解决因fpga与powerpc cpu之间srio接口堵塞无法正常通信的问题。

附图说明

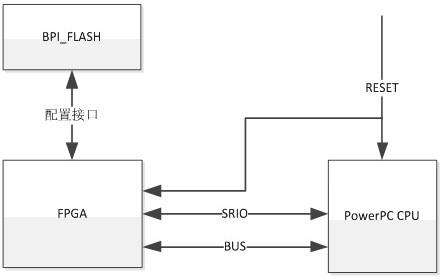

12.图1为本发明框架图;图2为本发明cap数据帧格式示意图。

具体实施方式

13.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

14.请参阅图1-2,一种解决srio接口阻塞的方法,包括以下步骤:第一步:cpu通过本地总线(bus)轮询和fpga间的srio接口状态;第二步:fpga在接收到cpu发送过来的复位信号后,对内部逻辑进行复位;第三步:fpga接收到重配置指令后,通过icap发送iprog指令进行重新配置。

15.所述第一步中一旦发现srio接口出现了阻塞的情况,首先发送软复位信号至fpga,同时对自身srio接口进行复位。

16.所述第一步中一旦发现srio接口出现了阻塞的情况,首先发送软复位信号至fpga,同时对自身srio接口进行复位。

17.所述第三步中irpog发送的配置数据的warm boot start address填写需要重配置的逻辑在flash中存储的地址即可。

18.所述fpga采用master模式进行配置时,上电启动后默认从flash的0地址处读取数据。所以我们在flash的0地址处烧写的配置bit文件应包含icap2原语。

19.在使用时,建立第一个工程为名称为led1,最终生成的bit文件为led_icap_top.bit实现功能有以下几点:1、fpga上电后,首先执行内部点灯逻辑(1秒闪烁一次)。在等待约10秒后,释放icap2_top模块的复位信号;2、icap2_top模块接收到复位释放5秒后,按固定时序将新的加载地址写入icape2核。

20.3、icape2在接收到指令后,从flash的 0x0040_0000地址处读取led2_top.bit文件并加载。

21.第二个工程名称为led2,最终生成的bit文件为led2_top.bit,实现功能为点灯逻辑,每200毫秒闪烁一次。

22.使用vivado2018.2工具将led1.bit和led2.bit生成一个icap_test.mcs文件,最

终烧写进flash中即可。注意led2_top.bit的start address地址要与icap中的保持一致。

23.实施流程给出的是icap2的重配置功能的验证方法,在xilinx xc7k325tfbg900芯片上已完成验证,确定方法切实可行。

24.尽管已经示出和描述了本发明的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本发明的原理和精神的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由所附权利要求及其等同物限定。

技术特征:

1.一种解决srio接口阻塞的方法,其特征在于:包括以下步骤:第一步:cpu通过本地总线(bus)轮询和fpga间的srio接口状态;第二步:fpga在接收到cpu发送过来的复位信号后,对内部逻辑进行复位;第三步:fpga接收到重配置指令后,通过icap发送iprog指令进行重新配置。2.根据权利要求1所述的一种解决srio接口阻塞的方法,其特征在于:所述第一步中一旦发现srio接口出现了阻塞的情况,首先发送软复位信号至fpga,同时对自身srio接口进行复位。3.根据权利要求1所述的一种解决srio接口阻塞的方法,其特征在于:所述第一步中仍不能解决接口阻塞的问题,则写入重新配置指令至fpga。4.根据权利要求1所述的一种解决srio接口阻塞的方法,其特征在于:所述第三步中irpog发送的配置数据的warm boot start address填写需要重配置的逻辑在flash中存储的地址即可。5.根据权利要求1所述的一种解决srio接口阻塞的方法,其特征在于:所述fpga采用master模式进行配置时,上电启动后默认从flash的0地址处读取数据。所以我们在flash的0地址处烧写的配置bit文件应包含icap2原语。

技术总结

本发明涉及高速接口通信技术领域,且公开了一种解决SRIO接口阻塞的方法,包括以下步骤:第一步:CPU通过本地总线(BUS)轮询和FPGA间的SRIO接口状态;第二步:FPGA在接收到CPU发送过来的复位信号后,对内部逻辑进行复位;第三步:FPGA接收到重配置指令后,通过ICAP发送IPROG指令进行重新配置,捕捉外部输入异步复位信号,对主动方式启动的FPGA进行重配置,进而解决因FPGA与PowerPC CPU之间SRIO接口堵塞无法正常通信的问题;在Master配置模式的硬件设计中,设备在不断电的情况下,重新配置FPGA,解决CPU与FPGA之间SRIO接口阻塞的问题。解决CPU与FPGA之间SRIO接口阻塞的问题。解决CPU与FPGA之间SRIO接口阻塞的问题。

技术研发人员:周剑峰 李云飞 程惠 赵丽娟

受保护的技术使用者:山西银河电子设备厂

技术研发日:2022.03.01

技术公布日:2022/4/26

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1