存储装置及其操作方法与流程

存储装置及其操作方法

1.相关申请的交叉引用

2.本技术要求于2020年10月13日提交的申请号为10-2020-0132229的韩国专利申请的优先权,该韩国专利申请通过引用整体并入本文。

技术领域

3.本公开涉及一种电子装置,并且更特别地,涉及一种存储装置及其操作方法。

背景技术:

4.存储装置是在诸如计算机或智能电话的主机装置的控制下存储数据的装置。存储装置可以包括存储数据的存储器装置和控制存储器装置的存储器控制器。存储器装置可以分类为易失性存储器装置和非易失性存储器装置。

5.易失性存储器装置可以是仅在供应电力时存储数据并在切断电力供应时丢失所存储的数据的装置。易失性存储器装置可以包括静态随机存取存储器(sram)、动态随机存取存储器(dram)等。

6.非易失性存储器装置是即使切断电力也不丢失数据的装置。非易失性存储器装置包括只读存储器(rom)、可编程rom(prom)、电可编程rom(eprom)、电可擦除可编程rom(eeprom)、闪速存储器等。

技术实现要素:

7.本公开的实施例提供一种使用具有有限容量的易失性存储器装置来管理映射数据的存储装置及其操作方法。

8.根据本公开的实施例,一种存储装置可以包括:非易失性存储器装置,被配置成存储包括映射数据的多个映射组块,该映射数据具有由主机提供的逻辑地址以及指示与该逻辑地址相对应的数据被存储的位置的物理地址;易失性存储器装置,包括映射组块缓冲器和映射组块状态表,该映射组块缓冲器临时存储多个映射组块中的一些,并且映射组块状态表存储映射组块状态信息,该映射组块状态信息指示非易失性存储器装置中存储的多个映射组块中的每一个是否被临时存储在映射组块缓冲器中;以及存储器控制器,被配置成控制非易失性存储器装置和易失性存储器装置,以响应于从主机输入的写入请求,将非易失性存储器装置中存储的多个映射组块之中包括请求写入的逻辑地址的映射组块加载到映射组块缓冲器中,并且存储指示包括请求写入的逻辑地址的映射组块被加载到映射组块缓冲器中的映射组块状态信息。

9.根据本公开的实施例,一种存储装置可以包括:非易失性存储器装置,被配置成存储包括映射数据的多个映射组块,该映射数据具有由主机提供的逻辑地址以及指示与该逻辑地址相对应的数据被存储的位置的物理地址;映射组块缓冲器,被配置成临时存储非易失性存储器装置中存储的多个映射组块中的一些;映射组块状态表,被配置成存储映射组块状态信息,该映射组块状态信息指示非易失性存储器装置中存储的多个映射组块中的每

一个是否被临时存储在映射组块缓冲器中;日志缓冲器,被配置成存储日志条目,该日志条目包括关于被临时存储在映射组块缓冲器中的映射组块中包括的多个映射条目之中的被更新的映射条目的信息;以及元切片缓冲器,被配置成临时存储元切片,该元切片包括非易失性存储器装置中存储的多个映射组块之中的脏状态的映射组块,其中待被存储在日志缓冲器中的日志条目的数量与待被存储在映射组块缓冲器中的映射组块的数量相同。

10.根据本公开的实施例,一种存储装置可以包括:存储介质,被配置成存储多个映射组块,每个映射组块包括多个映射条目;第一至第四存储器介质;以及控制器,被配置成:将存储介质中存储的多个映射组块之中与所请求的逻辑地址相对应的所请求的映射组块加载到第一存储器介质,选择性地改变所请求的映射组块内与所请求的逻辑地址相对应的映射条目,根据映射条目的选择性改变来在第二存储器介质中生成所请求的映射组块的第一信息,在第三存储器介质中生成被改变的映射条目的第二信息,当第三存储器介质变得充满其中所生成的第二信息时,通过参考第二信息,将存储介质中存储的多个映射组块之中的至少目标映射组块加载到第四存储器介质,通过参考第一信息将被改变的映射条目反映到目标映射组块中,并且在反映之后将目标映射组块存储回存储介质。

11.根据本技术,提供一种使用具有有限容量的易失性存储器装置来管理映射数据的存储装置及其操作方法。

附图说明

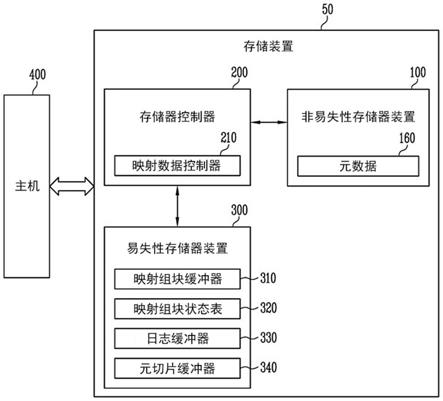

12.图1是示出根据本公开的实施例的存储装置的示图。

13.图2是示出图1的存储器装置的示图。

14.图3是示出图2的存储块中的一个的结构的示图。

15.图4是示出图1的元数据的示图。

16.图5是示出根据本公开的实施例的存储装置的写入操作的示图。

17.图6是示出根据本公开的实施例的存储装置的读取操作的示图。

18.图7是示出根据本公开的实施例的存储装置的映射更新操作的示图。

19.图8是示出根据本公开的实施例的管理存储装置的映射组块缓冲器的方法的示图。

20.图9是示出根据本公开的实施例的存储器控制器的结构的框图。

21.图10是示出根据本公开的实施例的操作存储装置的方法的流程图。

22.图11是示出根据本公开的实施例的操作存储装置的方法的流程图。

23.图12是示出图1的存储器控制器的另一实施例的示图。

24.图13是示出应用根据本公开的实施例的存储装置的存储卡系统的框图。

25.图14是示出应用根据本公开的实施例的存储装置的固态驱动器(ssd)系统的框图。

26.图15是示出应用根据本公开的实施例的存储装置的用户系统的框图。

具体实施方式

27.示出本说明书或本技术中公开的实施例的具体结构或功能描述仅用来描述根据本公开的实施例。本公开的实施例可以以各种形式实施,并且这些描述不限于本说明书或

本技术中描述的实施例。

28.图1是示出根据本公开的实施例的存储装置的示图。

29.参照图1,存储装置50可以包括非易失性存储器装置100、存储器控制器200和易失性存储器装置300。存储装置50可以是在诸如以下的主机400的控制下存储数据的装置:移动电话、智能电话、mp3播放器、膝上型计算机、台式计算机、游戏机、tv、平板pc、或车载式信息娱乐系统。可选地,存储装置50可以是在诸如服务器或数据中心的、将高容量数据存储在一个位置的主机400的控制下存储数据的装置。

30.根据作为与主机400之间的通信方法的主机接口,存储装置50可以被制造为各种类型的存储装置中的一种。例如,存储装置50可以被配置成诸如以下各种类型的存储装置中的任意一种:ssd,mmc、emmc、rs-mmc和微型mmc形式的多媒体卡,sd、迷你sd和微型sd形式的安全数字卡,通用串行总线(usb)存储装置,通用闪存(ufs)装置,个人计算机存储卡国际协会(pcmcia)卡型存储装置,外围组件互连(pci)卡型存储装置,高速pci(pci-e)卡型存储装置,紧凑型闪存(cf)卡,智能媒体卡和记忆棒。

31.存储装置50可以被制造为各种类型的封装中的任意一种。例如,存储装置50可以被制造为诸如以下的各种封装类型中的任意一种:堆叠封装(pop)、系统级封装(sip)、片上系统(soc)、多芯片封装(mcp)、板上芯片(cob)、晶圆级制造封装(wfp)和晶圆级堆叠封装(wsp)。

32.非易失性存储器装置100可以存储数据。非易失性存储器装置100可以在存储器控制器200的控制下操作。非易失性存储器装置100可以包括存储器单元阵列(未示出),该存储器单元阵列包括存储数据的多个存储器单元。

33.存储器单元中的每一个可以被配置成存储一个数据位的单层单元(slc)、存储两个数据位的多层单元(mlc)、存储三个数据位的三层单元(tlc)或能够存储四个数据位的四层单元(qlc)。

34.存储器单元阵列(未示出)可以包括多个存储块。每个存储块可以包括多个存储器单元。每个存储块可以包括多个页面。在实施例中,页面可以是将数据存储在非易失性存储器装置100中或者读取非易失性存储器装置100中存储的数据的单位。存储块可以是擦除数据的单位。

35.在实施例中,非易失性存储器装置100可以是:双倍数据速率同步动态随机存取存储器(ddr sdram)、第四代低功率双倍数据速率(lpddr4)sdram、图形双倍数据速率(gddr)sdram、低功率ddr(lpddr)、rambus动态随机存取存储器(rdram)、nand闪速存储器、垂直nand闪速存储器、nor闪速存储器、电阻式随机存取存储器(rram)、相变随机存取存储器(pram)、磁阻随机存取存储器(mram)、铁电随机存取存储器(fram)、自旋转移扭矩随机存取存储器(stt-ram)等。在本说明书中,为了便于描述,非易失性存储器装置100是nand闪速存储器。

36.非易失性存储器装置100被配置成从存储器控制器200接收命令和地址,并且访问存储器单元阵列中由地址选择的区域。非易失性存储器装置100可以对由地址选择的区域执行由命令指示的操作。例如,非易失性存储器装置100可以执行写入操作(编程操作)、读取操作和擦除操作。在编程操作期间,非易失性存储器装置100可以将数据编程到由地址选择的区域中。在读取操作期间,非易失性存储器装置100可以从由地址选择的区域中读取数

据。在擦除操作期间,非易失性存储器装置100可以擦除由地址选择的区域中存储的数据。

37.非易失性存储器装置100可以存储元数据160。元数据160可以包括映射数据,该映射数据包括在由主机400提供的逻辑地址和与该逻辑地址相对应的物理地址之间的映射信息。元数据可以包括多个映射组块(map chunk)。一个映射组块可以包括多个映射条目。一个映射条目可以包括一个逻辑地址的映射信息。

38.在实施例中,除了映射数据之外,元数据160还可以进一步包括关于存储块中包括的有效页面的信息、关于每个存储块的擦除次数的信息以及关于每个存储块的读取次数的信息。可选地,元数据160可以包括日志数据,该日志数据是关于映射条目之中的被更新的映射条目的信息。日志数据可以包括多个日志条目。一个日志条目可以包括关于一个映射条目的更新的信息。例如,日志条目可以包括关于逻辑地址的先前的物理地址和更新后的物理地址的信息。

39.在实施例中,可以以多个元切片(meta slice)为单位来更新元数据。一个元切片可以包括多个映射组块。元切片可以是存储器控制器200将更新后的映射数据存储在非易失性存储器装置100中或从非易失性存储器装置100读取映射组块的单位。

40.存储器控制器200可以控制存储装置50的全部操作。

41.当向存储装置50施加电力时,存储器控制器200可以运行固件(fw)。当非易失性存储器装置100是闪速存储器装置时,存储器控制器200可以运行诸如闪存转换层(ftl)的固件,以用于控制主机400与非易失性存储器装置100之间的通信。

42.在实施例中,存储器控制器200可以从主机400接收数据和逻辑地址(la),并且将la转换为物理地址(pa),该物理地址(pa)指示非易失性存储器装置100中包括的待存储数据的存储器单元的地址。

43.存储器控制器200可以根据主机400的请求控制非易失性存储器装置100以执行编程操作、读取操作或擦除操作。在编程操作期间,存储器控制器200可以将编程命令、pa和数据提供到非易失性存储器装置100。在读取操作期间,存储器控制器200可以将读取命令和pa提供到非易失性存储器装置100。在擦除操作期间,存储器控制器200可以将擦除命令和pa提供到非易失性存储器装置100。

44.在实施例中,存储器控制器200可以不考虑来自主机400的请求,独立地生成命令、地址和数据,并且将该命令、地址和数据传输到非易失性存储器装置100。例如,存储器控制器200可以将用于伴随损耗均衡、读取回收、垃圾收集等的执行而执行编程操作、读取操作和擦除操作的命令、地址和数据提供到非易失性存储器装置100。

45.在实施例中,存储器控制器200可以控制至少两个或更多个非易失性存储器装置100。在这种情况下,存储器控制器200可以根据交错方法来控制非易失性存储器装置100,以提高操作性能。交错方法可以是控制至少两个非易失性存储器装置100的操作以使操作彼此重叠的方法。

46.存储器控制器200可以包括映射数据控制器210。

47.在写入操作期间,映射数据控制器210可以分配与请求写入的逻辑地址相对应的物理地址。与请求写入的逻辑地址相对应的数据可以存储在非易失性存储器装置100内由所分配的物理地址指示的位置中。映射数据控制器210可以控制将包括请求写入的逻辑地址与所分配的物理地址之间的映射关系的映射数据存储在非易失性存储器装置100中的映

射更新操作。

48.在读取操作期间,映射数据控制器210可以搜索元数据160中包括的映射数据以获得与请求读取的逻辑地址相对应的物理地址。映射数据控制器210可以将与元数据160中包括的映射组块之中包括与请求读取的逻辑地址相对应的映射条目的映射组块加载到易失性存储器装置300中,并且从所加载的映射组块中获得与请求读取的逻辑地址相对应的物理地址。此后,存储器控制器200可以控制非易失性存储器装置100以执行读取所获得的物理地址中存储的数据的读取操作。

49.易失性存储器装置300可以包括映射组块缓冲器310、映射组块状态表320、日志缓冲器330和元切片缓冲器340。易失性存储器装置300可以是动态随机存取存储器(dram)或静态随机存取存储器(sram)。

50.映射组块缓冲器310可以是用于临时存储非易失性存储器装置100中存储的元数据160中包括的多个映射组块中的一些的区域。可以提前确定可以存储在映射组块缓冲器310中的映射组块的数量。映射组块缓冲器310可以提供用于存储映射组块的空间,从而存储器控制器200可以在写入操作或读取操作期间快速找到关于逻辑地址的映射数据,该逻辑地址对应于由主机请求写入或读取的数据。

51.映射组块状态表320可以包括非易失性存储器装置100中存储的多个映射组块的映射组块状态信息。映射组块状态信息可以是脏状态(已加载且脏)、干净状态(已加载且干净)和非存储状态(未加载)中的一个,其中脏状态指示映射组块中的每一个被临时存储在映射组块缓冲器310中并且包括被更新的映射条目,干净状态指示映射组块被临时存储在映射组块缓冲器310中并且不包括被更新的映射条目,非存储状态指示映射组块未被临时存储在映射组块缓冲器310中。在实施例中,映射组块状态信息可以进一步包括指示映射组块中的每一个在非易失性存储器装置100中存储的位置的物理地址。

52.日志缓冲器330可以存储日志数据。日志数据可以存储多个日志条目。每个日志条目可以包括关于被更新的映射条目的信息。例如,日志条目可以包括关于先前的物理地址和更新后的物理地址的信息,先前的物理地址是在更新与逻辑地址相对应的映射条目之前的物理地址,更新后的物理地址是在更新之后的物理地址。因为日志缓冲器330仅包括与多个映射组块的被更新的部分相对应的信息,所以存储器控制器200可以通过使用日志缓冲器330中存储的日志条目来重建最新状态的映射数据。

53.元切片缓冲器340可以是用于加载多个元切片之中包括待更新的映射组块的元切片的区域。元切片可以是存储器控制器200将更新后的映射数据存储在非易失性存储器装置100中或从非易失性存储器装置100读取映射组块的单位。

54.存储器控制器200可以将日志缓冲器330中存储的日志条目以及元切片缓冲器340中存储的被更新的映射组块一起存储在非易失性存储器装置100中。

55.主机400可以使用诸如以下的各种通信方法中的至少一种与存储装置50通信:通用串行总线(usb)、串行at附件(sata)、串列scsi(sas)、高速芯片间(hsic)、小型计算机系统接口(scsi)、外围组件互连(pci)、高速pci(pcie)、高速非易失性存储器(nvme)、通用闪存(ufs)、安全数字(sd)、多媒体卡(mmc)、嵌入式mmc(emmc)、双列直插式存储器模块(dimm)、寄存式dimm(rdimm)和低负载dimm(lrdimm)。

56.图2是示出图1的存储器装置的示图。

57.参照图2,非易失性存储器装置100可以包括存储器单元阵列110、电压生成器120、地址解码器130、输入/输出电路140和控制逻辑150。

58.存储器单元阵列110包括多个存储块blk1至blki。多个存储块blk1至blki通过行线rl连接到地址解码器130。多个存储块blk1至blki可以通过列线cl连接到输入/输出电路140。在实施例中,行线rl可以包括字线、源极选择线和漏极选择线。在实施例中,列线cl可以包括位线。

59.多个存储块blk1至blki中的每一个包括多个存储器单元。在实施例中,多个存储器单元可以是非易失性存储器单元。可以将多个存储器单元之中连接到相同字线的存储器单元定义为一个物理页面。也就是说,存储器单元阵列110可以包括多个物理页面。非易失性存储器装置100的存储器单元中的每一个可以被配置成存储一个数据位的slc、存储两个数据位的mlc、存储三个数据位的tlc或能够存储四个数据位的qlc。

60.多个存储块blk1至blki中的一些可以是存储参照图1描述的映射数据的映射数据块。多个存储块blk1至blki中的剩余存储块可以是存储由主机400请求的数据的普通块。

61.在实施例中,电压生成器120、地址解码器130和输入/输出电路140可以被统称为外围电路。外围电路在控制逻辑150的控制下驱动存储器单元阵列110。外围电路可以驱动存储器单元阵列110以执行编程操作、读取操作和擦除操作。

62.电压生成器120被配置成使用供应到非易失性存储器装置100的外部电源电压来生成多个操作电压。电压生成器120可以响应于控制逻辑150的控制而操作。

63.在实施例中,电压生成器120可以通过调节外部电源电压来生成内部电源电压。由电压生成器120生成的内部电源电压被用作非易失性存储器装置100的操作电压。

64.在实施例中,电压生成器120可以使用外部电源电压或内部电源电压来生成多个操作电压。电压生成器120可以被配置成生成非易失性存储器装置100中所需的各种电压。例如,电压生成器120可以生成多个擦除电压、多个编程电压、多个通过电压、多个选择读取电压以及多个未选择读取电压。

65.电压生成器120可以包括接收内部电源电压的多个泵浦电容器以生成具有各种电压电平的多个操作电压,并且可以响应于控制逻辑150的控制而通过选择性地启用多个泵浦电容器来生成多个操作电压。

66.可以通过地址解码器130将所生成的多个操作电压供应到存储器单元阵列110。

67.地址解码器130通过行线rl连接到存储器单元阵列110。地址解码器130被配置成响应于控制逻辑150的控制而操作。地址解码器130可以从控制逻辑150接收地址addr。地址解码器130可以对所接收的地址addr之中的块地址进行解码。地址解码器130可以根据经解码的块地址在存储块blk1至blki之中选择至少一个存储块。地址解码器130可以对所接收的地址addr之中的行地址进行解码。地址解码器130可以根据经解码的行地址在所选择的存储块的字线之中选择至少一个字线。在实施例中,地址解码器130可以对所接收的地址addr之中的列地址进行解码。地址解码器130可以根据经解码的列地址将输入/输出电路140和存储器单元阵列110彼此连接。

68.例如,地址解码器130可以包括诸如行解码器、列解码器和地址缓冲器的组件。

69.输入/输出电路140可以包括多个页面缓冲器。多个页面缓冲器可以通过位线连接到存储器单元阵列110。在编程操作期间,可以根据多个页面缓冲器中存储的数据将数据存

储在所选择的存储器单元中。

70.在读取操作期间,可以通过位线来感测所选择的存储器单元中存储的数据,并且可以将所感测的数据存储在页面缓冲器中。

71.控制逻辑150可以控制地址解码器130、电压生成器120和输入/输出电路140。控制逻辑150可以响应于从外部装置传输的命令cmd而操作。控制逻辑150可以响应于命令cmd和地址addr来生成控制信号,以控制外围电路。

72.图3是示出图2的存储块中的一个的配置的示图。

73.存储块blki是图2的存储块blk1至blki之中的一个存储块blki。

74.参照图3,彼此平行布置的多个字线可以连接在第一选择线和第二选择线之间。此处,第一选择线可以是源极选择线ssl,并且第二选择线可以是漏极选择线dsl。更具体地,存储块blki可以包括连接在位线bl1至bln与源极线sl之间的多个串st。位线bl1至bln可以分别连接到串st,并且源极线sl可以共同连接到串st。因为可以将串st配置成彼此相同,所以作为示例具体描述连接到第一位线bl1的串st。

75.串st可以包括串联连接在源极线sl与第一位线bl1之间的源极选择晶体管sst、多个存储器单元mc1至mc16、以及漏极选择晶体管dst。一个串st可以包括源极选择晶体管sst和漏极选择晶体管dst中的至少一个或多个,并且可以包括存储器单元mc1至mc16,或者比附图中所示数量更多的存储器单元。

76.源极选择晶体管sst的源极可以连接到源极线sl,并且漏极选择晶体管dst的漏极可以连接到第一位线bl1。存储器单元mc1至mc16可以串联连接在源极选择晶体管sst与漏极选择晶体管dst之间。不同串st中包括的源极选择晶体管sst的栅极可以连接到源极选择线ssl,漏极选择晶体管dst的栅极可以连接到漏极选择线dsl,并且存储器单元mc1至mc16的栅极可以连接到多个字线wl1至wl16。不同串st中包括的存储器单元之中连接到相同字线的一组存储器单元可以被称为页面pg。因此,存储块blki可以包括与字线wl1至wl16的数量相对应的数量的页面pg。

77.一个存储器单元可以存储一个数据位。这通常被称为单层单元(slc)。在这种情况下,一个物理页面pg可以存储一个逻辑页面(lpg)的数据。一个逻辑页面(lpg)数据可以包括具有与一个物理页面pg中包括的单元相同的数量的数据位。

78.一个存储器单元可以存储两个或更多个数据位。在这种情况下,一个物理页面pg可以存储两个或更多个逻辑页面(lpg)的数据。

79.图4是示出图1的元数据的示图。

80.参照图4,元数据160可以包括映射数据,该映射数据包括由主机400提供的逻辑地址和与该逻辑地址相对应的物理地址之间的映射信息。元数据可以包括多个映射组块。一个映射组块可以包括多个映射条目。一个映射条目可以包括一个逻辑地址的映射信息。

81.在图4中,非易失性存储器装置100存储10个映射组块mc1至mc10。

82.映射组块1mc1至映射组块10mc10中的每一个包括多个映射条目。在本说明书中,一个映射组块包括10个映射条目。

83.例如,映射组块1mc1可以包括映射条目1至映射条目10。映射组块2mc2可以包括映射条目11至映射条目20。在实施例中,尽管附图中未示出,但是除了映射数据之外,元数据160还可以进一步包括关于存储块中包括的有效页面的信息、关于每个存储块的擦除次数

的信息以及关于每个存储块的读取次数的信息。

84.在实施例中,元数据160可以包括作为关于映射条目之中被更新的映射条目的信息的日志数据。日志数据可以包括多个日志条目。一个日志条目可以包括关于一个映射条目的更新的信息。例如,日志条目可以包括关于在更新与逻辑地址相对应的映射条目之前的物理地址(先前的物理地址)和在更新与逻辑地址相对应的映射条目之后的物理地址(更新后的物理地址)的信息。

85.在实施例中,元数据可以被划分成多个元切片。在实施例中,元切片可以是更新元数据的单位。一个元切片可以包括多个映射组块。元切片可以是存储器控制器200将更新后的映射数据存储在非易失性存储器装置100中或从非易失性存储器装置100读取映射组块的单位。

86.图5是示出根据本公开的实施例的存储装置的写入操作的示图。

87.参照图1、图4和图5,存储器控制器200可以从主机接收写入请求。在图5的实施例中,请求写入的逻辑地址是第七逻辑地址la7。存储器控制器200可以分配与第七逻辑地址la7相对应的物理地址。为了更新与第七逻辑地址la7相对应的映射数据,存储器控制器200可以确定与第七逻辑地址la7相对应的映射条目所属的映射组块1mc1是否被加载到映射组块缓冲器310中。

88.存储器控制器200可以检查映射组块状态表320并确认映射组块1mc1处于非存储状态(未加载)(

①

检查mc1状态

→

未加载)。

89.存储器控制器200可以将非易失性存储器装置100中存储的多个映射组块mc1至mc10之中的映射组块1mc1加载到映射组块缓冲器310中(

②

加载mc1)。

90.存储器控制器200可以更新映射组块缓冲器310中加载的映射组块1mc1中包括的与第七逻辑地址la7相对应的映射条目(

③

更新映射数据)。具体地,存储器控制器200可以将更新映射条目之前的物理地址校正成更新后的物理地址。

91.存储器控制器200可以将映射组块状态表320的映射组块1mc1的状态从非存储状态(未加载)改变到脏状态(已加载且脏)(

④

改变状态)。

92.存储器控制器200可以生成包括关于被更新的映射条目的信息的日志条目(

⑤

生成日志条目)。该日志条目可以包括关于先前的物理地址和更新后的物理地址的信息,该先前的物理地址是在更新(

③

)与第七逻辑地址la7相对应的映射条目之前映射组块缓冲器310中加载的映射组块1mc1中包括的与第七逻辑地址la7相对应的映射条目中包括的物理地址,该更新后的物理地址是更新(

③

)之后的物理地址。

93.存储器控制器200可以将所生成的日志条目存储在日志缓冲器330中。

94.图6是示出根据本公开的实施例的存储装置的读取操作的示图。

95.参照图1、图4、图5和图6,存储器控制器200可以从主机接收读取请求。在图6的实施例中,请求读取的逻辑地址与映射组块2mc2中包括的映射条目相对应。

96.存储器控制器200可以检查映射组块状态表320并确认映射组块2mc2处于非存储状态(未加载)(

①

检查mc2状态

→

未加载)。

97.存储器控制器200可以将非易失性存储器装置100中存储的多个映射组块mc1至mc10之中的映射组块2mc2加载到映射组块缓冲器310中(

②

加载mc2)。

98.存储器控制器200可以将映射组块状态表320的映射组块2mc2的状态从非存储状

态(未加载)改变到干净状态(已加载且干净)(

③

改变状态)。

99.存储器控制器200可以从被临时存储在映射组块缓冲器310中的映射组块2mc2中获得与请求读取的逻辑地址相对应的物理地址(

④

从mc2获得pa)。

100.图7是示出根据本公开的实施例的存储装置的映射更新操作的示图。

101.参照图1和图7,六个映射组块被加载到映射组块缓冲器310中。具体地,映射组块1mc1、映射组块2mc2、映射组块5mc5、映射组块6mc6、映射组块7mc7和映射组块8mc8可以被加载到映射组块缓冲器310中。

102.在映射组块缓冲器310中加载的映射组块之中,映射组块1mc1、映射组块5mc5、映射组块7mc7和映射组块8mc8可以处于脏状态(已加载且脏)。

103.在映射组块缓冲器310中加载的映射组块之中,映射组块2mc2和映射组块6mc6可以处于干净状态(已加载且干净)。

104.映射组块1mc1、映射组块5mc5,映射组块7mc7和映射组块8mc8处于脏状态(已加载且脏)的实施例可以指示映射组块1mc1、映射组块5mc5,映射组块7mc7和映射组块8mc8中的每一个包括至少一个或多个被更新的映射条目。具体地,映射组块1mc1的第七逻辑地址“a”、映射组块5mc5的第五十四逻辑地址“b”、映射组块7mc7的第七十三逻辑地址“c”以及映射组块8mc8的第八十六逻辑地址“d”可以处于被更新的状态。

105.因为映射条目被更新,所以映射组块1mc1的第七逻辑地址“a”、映射组块5mc5的第五十四逻辑地址“b”、映射组块7mc7的第七十三逻辑地址“c”以及映射组块8mc8的第八十六逻辑地址“d”可以处于已存储状态。

106.当日志缓冲器330中存储的日志条目的数量达到预设数量时,可以执行映射更新操作。

107.存储器控制器200可以通过参考日志缓冲器330中存储的日志条目从非易失性存储器装置100获得映射组块缓冲器310中加载的映射组块之中处于脏状态(已加载且脏)的映射组块,并且将所获得的映射组块加载到元切片缓冲器340中(

①

加载映射组块)。存储器控制器200可以检查所加载的映射组块的映射组块状态信息(

②

检查所加载的映射组块),并且可以通过使用存储了处于已加载且脏的状态(已加载且脏)的映射组块的映射组块缓冲器310来更新元切片缓冲器340中加载的映射组块(

③

更新脏映射组块)。

108.此后,存储器控制器200可以执行将元切片缓冲器340中存储的被更新的映射组块以及日志缓冲器330中存储的日志数据存储在非易失性存储器装置100中的清除操作(

④

更新元切片)。此后,存储器控制器200可以将映射组块状态表320的被更新的映射组块的状态从脏状态(已加载且脏)改变为干净状态(已加载且干净)(

⑤

改变状态)。

109.根据本公开的实施例,存储器控制器200可以保持处于脏状态(已加载且脏)的映射组块的数量与所生成的日志的数量为1:1的状态。通过这样,即使易失性存储器装置300的容量不足,存储器控制器200也可以通过使用现有的4k映射方法和日志记录方法来实施超高容量的ssd。

110.图8是示出根据本公开的实施例的管理存储装置的映射组块缓冲器的方法的示图。

111.图8示出根据图7的实施例的在更新映射数据之后的状态。

112.参照图1、图7和图8,映射组块缓冲器310可以临时存储映射组块1mc1、映射组块

2mc2、映射组块5mc5、映射组块6mc6、映射组块7mc7和映射组块8mc8,并且它们的状态可以为干净状态(已加载且干净)。

113.根据本公开的实施例,存储器控制器200在将更新后的映射数据存储在非易失性存储器装置100中之后可以不立即从映射组块缓冲器310逐出更新后的映射数据,并且可以在映射组块缓冲器310中将更新后的映射数据保持为干净状态(已加载且干净)。在可能请求读取操作的状态下,不必移除干净状态(已加载且干净)的映射组块,并且这可以帮助提高随机读取的性能。

114.在图8中,主机可以提供读取请求。在图8中,请求读取的逻辑地址对应于映射组块3mc3中包括的映射条目。

115.存储器控制器200可以检查映射组块状态表320并确认映射组块3mc3处于非存储状态(未加载)(

①

检查mc3状态

→

未加载)。此后,存储器控制器200可以检查映射组块缓冲器310中是否存在用于加载映射组块的剩余空间。因为不存在剩余空间,所以存储器控制器200可以从映射组块缓冲器310中移除映射组块1mc1、映射组块2mc2、映射组块5mc5、映射组块6mc6、映射组块7mc7和映射组块8mc8之中的一个映射组块。此时,存储器控制器200可以移除最近最少使用的(lru)映射组块(

②

移除lru映射组块)。

116.存储器控制器200可以将非易失性存储器装置100中存储的多个映射组块mc1至mc10之中的映射组块3mc3加载到映射组块缓冲器310中(

③

加载mc3)。

117.存储器控制器200可以将映射组块状态表320的映射组块3mc3的状态从非存储状态(未加载)改变成干净状态(已加载且干净),并且相反地,存储器控制器200可以将映射组块8mc8的状态从干净状态(已加载且干净)改变成非存储状态(未加载)(

④

改变状态)。

118.存储器控制器200可以从被临时存储在映射组块缓冲器310中的映射组块3mc3中获得与请求读取的逻辑地址相对应的物理地址(

⑤

从mc3获得pa)。

119.图9是示出根据本公开的实施例的存储器控制器的结构的框图。

120.参照图1和图9,存储装置50可以包括非易失性存储器装置100、存储器控制器200和易失性存储器装置300。

121.存储器控制器200可以包括映射数据控制器210和存储器装置控制器220。映射数据控制器210可以包括映射组块缓冲器分配器211、地址转换器212和映射更新控制器213。存储器装置控制器220被配置成控制非易失性存储器装置100以将与写入请求相对应的写入数据存储在非易失性存储器装置100内由物理地址指示的位置中。

122.映射数据控制器210可以控制非易失性存储器装置100和易失性存储器装置300以更新映射组块缓冲器310中加载的映射组块中包括的映射条目,并且将包括被更新的映射条目的映射组块存储在非易失性存储器装置100中。

123.当输入写入请求时,地址转换器212可以分配用于将与请求写入的逻辑地址相对应的数据存储到非易失性存储器装置100中的物理地址。映射组块缓冲器分配器211可以从非易失性存储器装置100读取包括与请求写入的逻辑地址相对应的映射条目的映射组块,并且分配映射组块缓冲器310中的用于临时存储所读取的映射组块的空间。

124.当在映射组块缓冲器310中更新了与请求写入的逻辑地址相对应的映射条目时,映射更新控制器213生成包括关于与请求写入的逻辑地址相对应的映射条目的更新信息的日志条目。映射更新控制器213可以将所生成的日志条目存储在日志缓冲器330中。此处,日

志缓冲器330中可以存储的日志条目的数量可以与映射组块缓冲器310中可以存储的脏状态的映射组块的数量相同。此后,映射更新控制器213可以将映射组块状态表320内与请求写入的逻辑地址相对应的映射组块的状态信息改变成脏状态。

125.当预设数量的日志条目被存储在日志缓冲器330中时,映射更新控制器213可以从非易失性存储器装置100获得与日志条目相对应的映射组块并且将该映射组块存储在元切片缓冲器340中。映射更新控制器213可以使用被临时存储在映射组块缓冲器310中的映射组块来更新元切片缓冲器340中存储的映射组块,并且将被更新的映射组块以及日志条目存储在非易失性存储器装置100中。此后,映射更新控制器213可以将被更新的映射组块的状态信息改变成干净状态。

126.图10是示出根据本公开的实施例的操作存储装置的方法的流程图。

127.参照图10,在操作s1001中,存储装置可以接收写入请求。

128.在操作s1003中,可以确定包括请求写入的逻辑地址的映射组块是否被存储在易失性存储器装置中。作为确定的结果,当包括请求写入的逻辑地址的映射组块被存储在易失性存储器装置中时,该方法进行到操作s1007,否则该方法进行到操作s1005。

129.在操作s1005中,存储装置可以从非易失性存储器装置中读取包括请求写入的逻辑地址的映射组块,并且将包括请求写入的逻辑地址的映射组块存储在映射组块缓冲器中。

130.在操作s1007中,存储装置可以更新所加载的映射组块中包括的映射条目。映射条目的更新可以是将更新之前的物理地址改变为更新之后的物理地址。

131.在操作s1009中,存储装置可以将映射组块状态表中存储的该映射组块的状态改变为脏状态。

132.在操作s1011中,存储装置可以生成与被更新的映射条目相对应的日志条目。日志条目可以包括在更新与请求写入的逻辑地址相对应的映射条目之前的物理地址和在更新与请求写入的逻辑地址相对应的映射条目之后的物理地址。

133.在操作s1013中,存储装置可以确定日志缓冲器是否已满(即,日志缓冲器330中存储的日志条目的数量是否达到预设数量)。当日志缓冲器中存在剩余空间时(即,当日志缓冲器330中存储的日志条目的数量尚未达到预设数量时),因为不需要执行映射更新,所以该方法结束。当日志缓冲器已满时(即,当日志缓冲器330中存储的日志条目的数量达到预设数量时),可以执行操作s1015至s1021以执行映射更新。

134.在操作s1015中,存储装置可以再次从非易失性存储器装置读取与日志条目相对应的映射组块,并且将该映射组块加载到元切片缓冲器中。

135.在操作s1017中,存储装置可以通过使用映射组块缓冲器中包括的脏状态的映射组块来更新元切片缓冲器中存储的映射组块。

136.在操作s1019中,存储装置可以执行将日志缓冲器中存储的日志数据以及元切片缓冲器中存储的数据存储在非易失性存储器装置中的清除操作。

137.在操作s1021中,存储装置可以将映射组块状态表中存储的被更新的映射组块的状态更新为干净状态。

138.图11是示出根据本公开的实施例的操作存储装置的方法的流程图。

139.参照图11,在操作s1101中,存储装置可以从主机接收读取请求。

140.在操作s1103中,存储装置可以确定包括请求读取的逻辑地址的映射组块是否被存储在映射组块缓冲器中。作为确定的结果,当包括请求读取的逻辑地址的映射组块被存储在易失性存储器装置中包括的映射组块缓冲器中时,该方法进行到操作s1107,否则该方法进行到操作s1105。

141.在操作s1105中,存储装置可以从非易失性存储器装置中读取包括请求读取的逻辑地址的映射组块并且将该映射组块存储在映射组块缓冲器中。

142.在操作s1107中,存储装置可以将映射组块状态表中存储的该映射组块的状态改变为干净状态。

143.在操作s1109中,存储装置可以从所加载的映射组块中获得与请求读取的逻辑地址相对应的物理地址。

144.在操作s1111中,存储装置可以读取所获得的物理地址中存储的数据。

145.图12是示出图1的存储器控制器的另一实施例的示图。

146.参照图12,存储器控制器800可以包括处理器810、ram 820、错误校正电路830、主机接口840、rom 850和闪存接口860。

147.处理器810可以控制存储器控制器800的全部操作。ram 820可以用作存储器控制器800的缓冲存储器、高速缓存存储器、操作存储器等。例如,参照图1描述的映射数据控制器210可以以由处理器810运行的固件中包括的软件的形式被存储在ram 820或rom 850中。

148.rom 850可以以固件形式来存储存储器控制器800进行操作所需的各种信息。

149.存储器控制器800可以通过主机接口840与外部装置(例如,主机400、应用处理器等)通信。

150.存储器控制器800可以通过闪存接口860与非易失性存储器装置100通信。存储器控制器800可以通过闪存接口860将命令cmd、地址addr、控制信号ctrl等传输到非易失性存储器装置100并且接收数据data。例如,闪存接口860可以包括nand接口。

151.图13是示出应用根据本公开的实施例的存储装置的存储卡系统的框图。

152.参照图13,存储卡系统2000包括存储器控制器2100、存储器装置2200和连接器2300。

153.存储器控制器2100连接到存储器装置2200。存储器控制器2100被配置成访问存储器装置2200。例如,存储器控制器2100可以被配置成控制存储器装置2200的读取操作、编程操作、擦除操作和后台操作。存储器控制器2100被配置成提供存储器装置2200和主机之间的接口。存储器控制器2100被配置成驱动用于控制存储器装置2200的固件。存储器控制器2100可以与参照图1描述的存储器控制器200相同地实施。

154.例如,存储器控制器2100可以包括诸如随机存取存储器(ram)、处理器、主机接口、存储器接口和错误校正器的组件。

155.存储器控制器2100可以通过连接器2300与外部装置通信。存储器控制器2100可以根据特定的通信标准与外部装置(例如,主机)通信。例如,存储器控制器2100被配置成通过诸如以下的各种通信标准中的至少一种与外部装置通信:通用串行总线(usb)、多媒体卡(mmc)、嵌入式mmc(emmc)、外围组件互连(pci)、高速pci(pci-e)、高级技术附件(ata)、串行ata、并行ata、小型计算机系统接口(scsi)、增强型小型磁盘接口(esdi)、电子集成驱动器(ide)、火线、通用闪存(ufs)、wifi、蓝牙和nvme。例如,连接器2300可以由上述各种通信标

sdram、ddr3sdram、lpddr sdram、lpddr2 sdram和lpddr3 sdram的易失性随机存取存储器或者诸如pram、reram、mram和fram的非易失性随机存取存储器。例如,应用处理器4100和存储器模块4200可以基于堆叠封装(pop)来进行封装,并且被设置为一个半导体封装。

168.网络模块4300可以与外部装置通信。例如,网络模块4300可以支持诸如以下的无线通信:码分多址(cdma)、全球移动通信系统(gsm)、宽带cdma(wcdma)、cdma-2000、时分多址(tdma)、长期演进、wimax、wlan、uwb、蓝牙和wifi。例如,网络模块4300可以被包括在应用处理器4100中。

169.存储模块4400可以存储数据。例如,存储模块4400可以存储从应用处理器4100接收的数据。可选地,存储模块4400可以将存储模块4400中存储的数据传输到应用处理器4100。例如,存储模块4400可以利用诸如相变ram(pram)、磁性ram(mram)、电阻式ram(rram)、nand闪存、nor闪存和三维nand闪存的非易失性半导体存储器元件来实施。例如,存储模块4400可以被设置为用户系统4000的诸如存储卡和外部驱动器的可移动存储装置(可移动驱动器)。

170.例如,存储模块4400可以包括多个非易失性存储器装置,并且多个非易失性存储器装置可以与参照图1描述的非易失性存储器装置100相同地操作。存储模块4400可以与参照图1描述的存储装置50相同地操作。

171.用户接口4500可以包括用于向应用处理器4100输入数据或指令或者用于向外部装置输出数据的接口。例如,用户接口4500可以包括诸如以下的用户输入接口:键盘、小键盘、按钮、触摸面板、触摸屏、触摸板、触摸球、相机、麦克风、陀螺仪传感器、振动传感器和压电元件。用户接口4500可以包括诸如以下的用户输出接口:液晶显示器(lcd)、有机发光二极管(oled)显示装置、有源矩阵oled(amoled)显示装置、led、扬声器和监视器。

172.已经在附图和说明书中描述了本公开的各个实施例。尽管本文使用了特定术语,但是所使用的术语仅是为了描述本公开的实施例。因此,本公开不受限于上述实施例,并且在本公开的精神和范围内可能有许多变化。对于本领域技术人员应当显而易见的是,除了本文公开的实施例之外,还可以基于本公开的技术范围进行各种修改。鉴于本公开而显而易见的增加、减少或修改旨在落入所附权利要求书的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1