像素补偿电路、显示面板和驱动方法与流程

本申请涉及显示,尤其涉及一种像素补偿电路、显示面板和驱动方法。

背景技术:

1、oled(organic light-emitting diode,有机发光二极管)是一种新兴的平板显示器件,由于其具有能自发光、对比度高,色域广等优点,并且还具有制备工艺简单、成本低、功耗低、易于实现柔性显示等优点,因此具有广阔的应用前景。

2、虽然oled显示器件具有上述优点,但是在其应用过程中也延伸出许多问题,例如受供电线的线阻r影响,在上一行开启之后,levdd电源将会分流给上一行oled,电流为i1,则下一行的电源将不是levdd,而是levdd-i1*r,同理可知后面每一行都会如此,即会造成供电电压逐渐变小,导致亮度显示不均。

技术实现思路

1、本申请的目的是提供一种像素补偿电路、显示面板和驱动方法,控制改变像素补偿电路中的驱动管的栅极端电压,进而调整发光元件的发光电流,改善亮度不均。

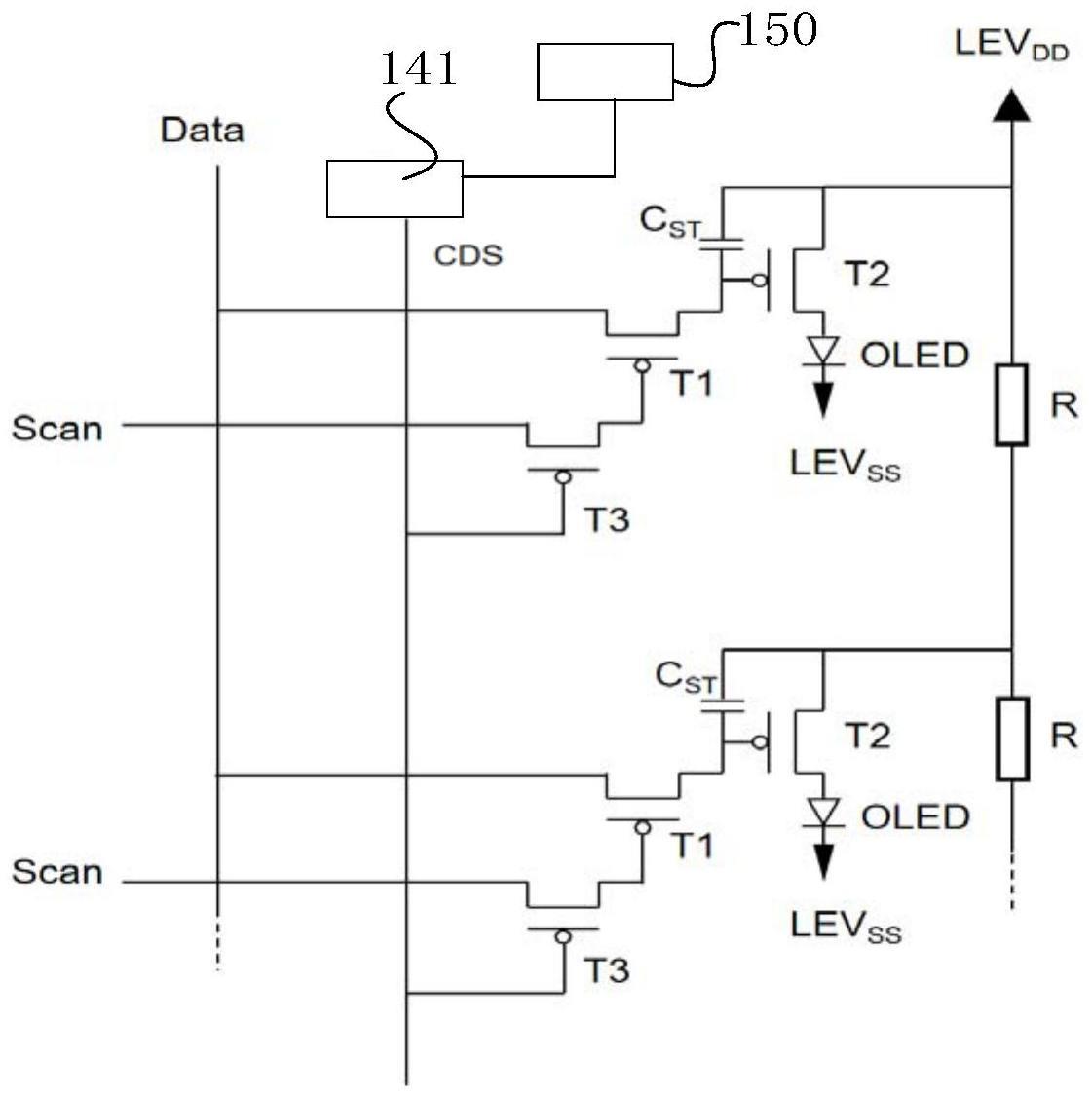

2、本申请公开了一种像素补偿电路,包括数据线、栅极线、由所述数据线和栅极线驱动的像素、第一晶体管、第二晶体管、储存电容和发光元件,所述第一晶体管和所述第二晶体管均包括栅极、源极和漏极;所述像素补偿电路还包括栅极信号输出控制模块;所述第一晶体管的栅极通过所述栅极信号输出控制模块连接所述栅极线,源极连接所述数据线,漏极连接第二晶体管的栅极;所述第二晶体管的源极连接电源电压,漏极通过所述发光元件连接一低电平;所述储存电容设置在所述第二晶体管的栅极和源极之间;其中,所述栅极信号输出控制模块控制所述栅极线上的栅极信号输出至所述第一晶体管的栅极以控制所述第一晶体管的导通时长,从而控制数据线上的数据电压输入至第二晶体管的栅极端的时间,以控制所述第二晶体管的栅极端的电压,调整所述发光元件的发光电流。

3、可选的,所述栅极信号输出控制模块包括信号控制单元和第三晶体管,所述第三晶体管包括栅极、源极和漏极;所述第三晶体管的栅极连接所述信号控制单元,源极连接所述栅极线,漏极连接所述第二晶体管的栅极;所述信号控制单元控制所述第三晶体管导通,所述栅极线上的信号经所述第三晶体管输入至所述第一晶体管的栅极,以导通所述第一晶体管,所述数据线上数据电压经所述第一晶体管输入至所述第二晶体管的栅极以导通所述第二晶体管。

4、可选的,所述第二晶体管为p型mos管,所述第一晶体管和第三晶体管为n型mos管;所述第三晶体管的栅极接收所述控制信号模块输出的控制信号以进行导通或关断,所述控制信号的高电平周期的时长小于等于所述栅极线上的栅极信号的高电平周期的时长。

5、可选的,所述像素补偿电路包括计算模块,所述计算模块与所述信号控制单元连接,所述计算模块通过以下公式①-③计算得到所述第二晶体管的栅极端的理想电压:

6、i1=a(elvdd-vdata1+vth)2……①

7、in=a[elvdd-(vdatan+in-1r)+vth]2……②

8、vdatan′=vdatan-(i1+i2+……+in-1)r……③

9、其中,vdatan′为第n行像素补偿后的所述第二晶体管的栅极端的理想电压,r为每行像素对应的电源电压供电线的等效电阻,i1为第1行像素对应的理想驱动电流值,in为第n行像素的理想驱动电流值;elvdd为电源电压值、vth为驱动管电压阈值,vdatan为第n行像素对应的所述第二晶体管的栅极端的的原始电压,a为常数,n为大于等于2的自然数;

10、所述计算模块通过以下公式④计算得到第一晶体管的导通时长:

11、t2=[vn*t1-(i1+i2+……+in-1)r]/vn……④

12、其中,t2为第一晶体管的导通时长,t1为栅极线高电平周期,vn为第n行像素的数据电压值,所述控制信号的高电平周期的时长等于t2。

13、可选的,所述栅极信号输出控制模块包括多个第三晶体管,每个所述像素补偿电路对应设置一个所述第三晶体管,所述信号控制单元连接所有的所述第三晶体管的栅极。

14、本申请还公开了一种显示面板,所述显示面板包括如上任一所述的像素补偿电路,所述显示面板还包括栅极驱动芯片和数据驱动芯片,所述栅极驱动芯片输出栅极信号至栅极线以输出至所述像素补偿电路,所述数据驱动芯片输出数据电压值数据线以输出至所述像素补偿电路。

15、可选的,所述栅极信号输出控制模块设置在所述栅极驱动芯片上,所述计算模块设置在所述数据驱动芯片上;所述栅极信号输出控制模块与所述计算模块耦接,所述栅极信号输出控制模块根据所述计算模块的计算结构生产控制信号以控制所述栅极线上的栅极信号输出至所述第一晶体管的栅极以控制所述第一晶体管的导通时长,从而控制数据线上的数据电压输入至第二晶体管的栅极端的时间,以控制所述第二晶体管的栅极端的电压。

16、本申请还公开了一种驱动方法,用于驱动如上任一所述的显示面板,所述驱动方法包括步骤:

17、输入栅极信号至所述像素补偿电路;

18、通过栅极信号控制所述像素补偿电路接收数据信号;以及

19、在预设时间内停止所述栅极信号的输入使得所述像素补偿电路停止接收数据信号;

20、其中,所述预设时间的时长小于所述栅极信号的高电平周期的时长。

21、可选的,所述驱动方法还包括步骤:

22、根据所述第二晶体管的栅极端的原始电压和理想电压计算得到第一晶体管的导通时长;

23、其中,所述第一晶体管的导通时长根据以下公式④计算得到:

24、t2=[vn*t1-(i1+i2+……+in-1)r]/vn……④

25、其中,r为每行像素对应的电源电压供电线的等效电阻,i1为第1行像素对应的理想驱动电流值,in为第n行像素的理想驱动电流值;t2为第一晶体管的导通时长,t1为栅极线高电平周期,vn为第n行像素的数据电压值,所述第一晶体管的导通时长t2为栅极信号的输入时长,等于所述预设时间的时长。

26、可选的,每一行像素的预设时间不同,从第一行像素至最后一行像素的预设时间依次增加。

27、相对于通过改变数据电压大小的方案来说,本申请不需要对数据电压进行计算改变,在像素补偿电路中对数据电压输入进行控制的第一晶体管与栅极线之间设置一个栅极信号输出控制模块,所述第一晶体管的栅极通过所述栅极信号输出控制模块连接所述栅极线,所述栅极信号输出控制模块控制所述栅极线上的栅极信号输出至所述第一晶体管的栅极以控制所述第一晶体管的导通时长,从而控制数据线上的数据电压输入至第二晶体管的栅极端的时间,以控制所述第二晶体管的栅极端的电压,调整所述发光元件的发光电流,从而改善显示面板的亮度不均。

技术特征:

1.一种像素补偿电路,包括数据线、栅极线、由所述数据线和栅极线驱动的像素、第一晶体管、第二晶体管、储存电容和发光元件,所述第一晶体管和所述第二晶体管均包括栅极、源极和漏极;其特征在于,

2.如权利要求1所述的像素补偿电路,其特征在于,所述栅极信号输出控制模块包括信号控制单元和第三晶体管,所述第三晶体管包括栅极、源极和漏极;

3.如权利要求2所述的像素补偿电路,其特征在于,所述第二晶体管为p型mos管,所述第一晶体管和第三晶体管为n型mos管;所述第三晶体管的栅极接收所述控制信号模块输出的控制信号以进行导通或关断,所述控制信号的高电平周期的时长小于等于所述栅极线上的栅极信号的高电平周期的时长。

4.如权利要求3所述的像素补偿电路,其特征在于,所述像素补偿电路包括计算模块,所述计算模块与所述信号控制单元连接,所述计算模块通过以下公式①-③计算得到所述第二晶体管的栅极端的理想电压:

5.如权利要求4所述的像素补偿电路,其特征在于,所述栅极信号输出控制模块包括多个第三晶体管,每个所述像素补偿电路对应设置一个所述第三晶体管,所述信号控制单元连接所有的所述第三晶体管的栅极。

6.一种显示面板,其特征在于,包括如权利要求1-5任意一项所述的像素补偿电路,所述显示面板还包括栅极驱动芯片和数据驱动芯片,所述栅极驱动芯片输出栅极信号至栅极线以输出至所述像素补偿电路,所述数据驱动芯片输出数据电压值数据线以输出至所述像素补偿电路。

7.如权利要求6所述的显示面板,其特征在于,所述栅极信号输出控制模块设置在所述栅极驱动芯片上,所述计算模块设置在所述数据驱动芯片上;

8.一种驱动方法,用于驱动如权利要求6-7任意一项所述的显示面板,其特征在于,所述驱动方法包括步骤:

9.如权利要求8所述的驱动方法,其特征在于,所述驱动方法还包括步骤:

10.如权利要求9所述的驱动方法,其特征在于,每一行像素的预设时间不同,从第一行像素至最后一行像素的预设时间依次增加。

技术总结

本申请公开了一种像素补偿电路、显示面板和驱动方法,所述像素补偿电路中设有栅极信号输出控制模块;第一晶体管的栅极通过栅极信号输出控制模块连接栅极线,源极连接数据线,漏极连接第二晶体管的栅极;第二晶体管的源极连接电源电压,漏极通过发光元件连接一低电平;储存电容设置在第二晶体管的栅极和源极之间。本申请在第一晶体管与栅极线之间设置的栅极信号输出控制模块控制栅极线上的栅极信号输出至第一晶体管的栅极以控制第一晶体管的导通时长,从而控制数据线上的数据电压输入至第二晶体管的栅极端的时间,以控制第二晶体管的栅极端的电压,调整发光元件的发光电流,从而改善显示面板的亮度不均。

技术研发人员:任鹏,李克林,李荣荣

受保护的技术使用者:重庆惠科金渝光电科技有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!