驱动电路、驱动方法和显示装置与流程

本发明涉及显示,尤其涉及一种驱动电路、驱动方法和显示装置。

背景技术:

1、在相关技术中,所述驱动电路为8t2c驱动电路,采用的晶体管的个数和电容的个数较多,不利于实现窄边框和节省成本。相关技术不能在简化驱动电路的情况下满足像素驱动的需求。

技术实现思路

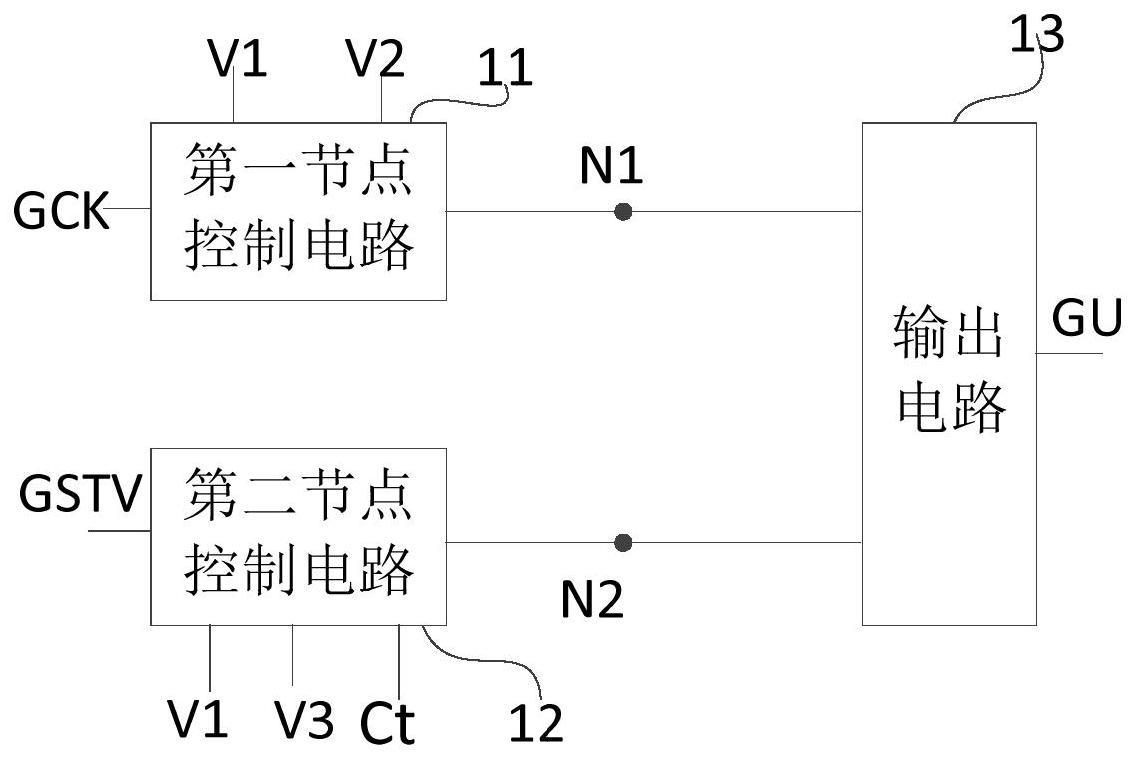

1、在一个方面中,本发明实施例提供一种驱动电路,包括第一节点控制电路、第二节点控制电路和输出电路;

2、所述第一节点控制电路分别与第一节点、第一时钟信号端、第一电压端和第二电压端电连接,用于在所述第一时钟信号端提供的第一时钟信号的控制下,控制所述第一节点与所述第一电压端之间连通,在所述第一时钟信号的控制下,控制所述第一节点与所述第二电压端之间连通;

3、所述第二节点控制电路分别与第二节点、输入端、第一电压端、控制端和第三电压端电连接,用于在所述输入端提供的输入信号的控制下,控制所述第二节点与所述第一电压端之间连通,在所述控制端提供的控制信号的控制下,控制所述第二节点与所述第三电压端之间连通;

4、所述输出电路分别与所述第一节点、所述第二节点和驱动输出端电连接,用于在所述第一节点的电位和所述第二节点的电位的控制下,控制所述驱动输出端输出驱动信号。

5、可选的,所述输出电路还分别与第二电压端和第二时钟信号端电连接,用于在所述第一节点的电位的控制下,控制所述驱动输出端与所述第二电压端之间连通,在所述第二节点的电位的控制下,控制所述驱动输出端与所述第二时钟信号端之间连通。

6、可选的,本发明至少一实施例所述的驱动电路还包括储能电路;

7、所述储能电路分别与所述第二节点和所述驱动输出端电连接,用于储存电能。

8、可选的,所述控制端为第一复位端;所述第一复位端与相邻下n级驱动输出端电连接,n为正整数。

9、可选的,所述控制端为第二复位端;

10、所述第二复位端用于在复位阶段包括的至少两个复位时间段,提供有效电压信号,以使得所述第二节点控制电路在所述第二复位端提供的第二复位信号的控制下,控制所述第二节点与所述第三电压端之间连通。

11、可选的,第一节点控制电路包括第一晶体管和第二晶体管;

12、所述第一晶体管的栅极与所述第一时钟信号端电连接,所述第一晶体管的第一极与所述第一电压端电连接,所述第一晶体管的第二极与所述第一节点电连接;

13、所述第二晶体管的栅极与所述第一时钟信号端电连接,所述第二晶体管的第一极与第二电压端电连接,所述第二晶体管的第二极与所述第一节点电连接;

14、所述第一晶体管为p型晶体管,所述第二晶体管为n型晶体管;或者,所述第一晶体管为n型晶体管,所述第二晶体管为p型晶体管。

15、可选的,所述第二节点控制电路包括第三晶体管和第四晶体管;

16、所述第三晶体管的栅极与所述输入端电连接,所述第三晶体管的第一极与所述第一电压端电连接,所述第三晶体管的第二极与所述第二节点电连接;

17、所述第四晶体管的栅极与所述第一复位端电连接,所述第四晶体管的第一极与所述第三电压端电连接,所述第四晶体管的第二极与所述第二节点电连接。

18、可选的,所述第二节点控制电路包括第三晶体管和第四晶体管;

19、所述第三晶体管的栅极与所述输入端电连接,所述第三晶体管的第一极与所述第一电压端电连接,所述第三晶体管的第二极与所述第二节点电连接;

20、所述第四晶体管的栅极与所述第二复位端电连接,所述第四晶体管的第一极与所述第三电压端电连接,所述第四晶体管第二极与所述第二节点电连接。

21、可选的,所述输出电路包括第五晶体管和第六晶体管;

22、所述第五晶体管的栅极与所述第一节点电连接,所述第五晶体管的第一极与所述第二电压端电连接,所述第五晶体管的第二极与所述驱动输出端电连接;

23、所述第六晶体管的栅极与所述第二节点电连接,所述第六晶体管的第一极与所述驱动输出端电连接,所述第六晶体管的第二极与所述第二时钟信号端电连接。

24、可选的,所述第六晶体管为p型晶体管,所述第三电压端提供的第三电压信号的电压值大于所述第二电压端提供的第二电压信号的电压值;或者,

25、所述第六晶体管为n型晶体管,所述第三电压端提供的第三电压信号的电压值小于所述第二电压端提供的第二电压信号的电压值。

26、可选的,所述储能电路包括存储电容;

27、所述存储电容的第一端与所述第二节点电连接,所述存储电容的第二电压端与所述驱动输出端电连接。

28、可选的,本发明实施例所述的驱动电路还包括第七晶体管;所述输出电路通过所述第七晶体管与所述第一节点电连接;

29、所述第七晶体管的栅极与第四电压端电连接,所述第七晶体管的第一极与所述第一节点电连接,所述第七晶体管的第二极与所述输出电路电连接。

30、在第二个方面中,本发明实施例提供一种驱动方法,应用于上述的驱动电路,所述驱动方法包括:

31、第一节点控制电路在第一时钟信号的控制下,控制第一节点与第一电压端之间连通,第一节点控制电路在所述第一时钟信号的控制下,控制所述第一节点与第二电压端之间连通;

32、第二节点控制电路在输入信号的控制下,控制第二节点与第一电压端之间连通,第二节点控制电路在控制信号的控制下,控制所述第二节点与第三电压端之间连通;

33、输出电路在所述第一节点的电位和所述第二节点的电位的控制下,控制驱动输出端输出驱动信号。

34、可选的,所述输出电路在所述第一节点的电位和所述第二节点的电位的控制下,控制驱动输出端输出驱动信号步骤包括:

35、所述输出电路在所述第一节点的电位的控制下,控制所述驱动输出端与第二电压端之间连通,所述输出电路在所述第二节点的电位的控制下,控制所述驱动输出端与第二时钟信号端之间连通。

36、在第三个方面中,本发明实施例提供一种显示装置,包括上述的驱动电路。

37、本发明实施例所述的驱动电路采用极简结构,能够在简化电路的情况下满足像素驱动的需求,同时简化后电路及其驱动能力,以及工艺margin(裕量)与现有量产的驱动电路相当,利于实现窄边框和低成本。

技术特征:

1.一种驱动电路,其特征在于,包括第一节点控制电路、第二节点控制电路和输出电路;

2.如权利要求1所述的驱动电路,其特征在于,所述输出电路还分别与第二电压端和第二时钟信号端电连接,用于在所述第一节点的电位的控制下,控制所述驱动输出端与所述第二电压端之间连通,在所述第二节点的电位的控制下,控制所述驱动输出端与所述第二时钟信号端之间连通。

3.如权利要求1所述的驱动电路,其特征在于,还包括储能电路;

4.如权利要求1所述的驱动电路,其特征在于,所述控制端为第一复位端;所述第一复位端与相邻下n级驱动输出端电连接,n为正整数。

5.如权利要求1所述的驱动电路,其特征在于,所述控制端为第二复位端;

6.如权利要求1所述的驱动电路,其特征在于,第一节点控制电路包括第一晶体管和第二晶体管;

7.如权利要求4所述的驱动电路,其特征在于,所述第二节点控制电路包括第三晶体管和第四晶体管;

8.如权利要求5所述的驱动电路,其特征在于,所述第二节点控制电路包括第三晶体管和第四晶体管;

9.如权利要求2所述的驱动电路,其特征在于,所述输出电路包括第五晶体管和第六晶体管;

10.如权利要求9所述的驱动电路,其特征在于,所述第六晶体管为p型晶体管,所述第三电压端提供的第三电压信号的电压值大于所述第二电压端提供的第二电压信号的电压值;或者,

11.如权利要求3所述的驱动电路,其特征在于,所述储能电路包括存储电容;

12.如权利要求1至11中任一权利要求所述的驱动电路,其特征在于,还包括第七晶体管;所述输出电路通过所述第七晶体管与所述第一节点电连接;

13.一种驱动方法,应用于如权利要求1至12中任一权利要求所述的驱动电路,其特征在于,所述驱动方法包括:

14.如权利要求13所述的驱动方法,其特征在于,所述输出电路在所述第一节点的电位和所述第二节点的电位的控制下,控制驱动输出端输出驱动信号步骤包括:

15.一种显示装置,其特征在于,包括如权利要求1至10中任一权利要求所述的驱动电路。

技术总结

本发明提供一种驱动电路、驱动方法和显示装置。驱动电路包括第一节点控制电路、第二节点控制电路和输出电路;第一节点控制电路控制第一节点与第一电压端之间连通,在第一时钟信号的控制下,控制第一节点与第二电压端之间连通;第二节点控制电路在输入信号的控制下,控制第二节点与第一电压端之间连通,在控制信号的控制下,控制第二节点与第三电压端之间连通;输出电路在第一节点的电位和第二节点的电位的控制下,控制驱动输出端输出驱动信号。本发明能够在简化电路的情况下满足像素驱动的需求。

技术研发人员:黄耀,都蒙蒙,董向丹,胡明

受保护的技术使用者:京东方科技集团股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!