像素布局结构和电致发光显示器的制作方法

本申请涉及像素布局领域,尤其涉及一种像素布局结构和电致发光显示器。

背景技术:

1、电致发光(electroluminescence)显示器使用发光二极管(light emittingdiode,led)或有机发光二极管(organic light emitting diode,oled)做为发光器件,现今已广泛应用在消费级和工业级领域,其中显示画质的提升是显示器技术开发的一个重要且持续性的目标。无论显示器的驱动基底为传统显示器采用的薄膜晶体管(thin filmtransistor,tft)工艺或微显示器(micro display)采用的互补式金属氧化物半导体(complementary metal-oxide-semiconductor,cmos)工艺,其中最重要的关注点之一在于像素密度(pixels per inch,ppi)的规格。

2、虽然cmos工艺可以大幅提升像素密度的规格,但是目前在奈米制程节点(nanotechnology node)或先进制程节点(advanced technology node)下所制作的显示器中,用于组成像素电路的元件受限于制程及设计规范(design rule),无法将高压元件与低压元件放置在有限的子像素布局面积内,导致这些显示器的像素密度(pixels per inch,ppi)受到限制,无法提升。

技术实现思路

1、本申请的多个方面提供一种像素布局结构和电致发光显示器,让高压元件和底压元件可以同时放置在有限的子像素布局面积内,解决了一般显示器的像素密度受到限制而无法提升的问题。

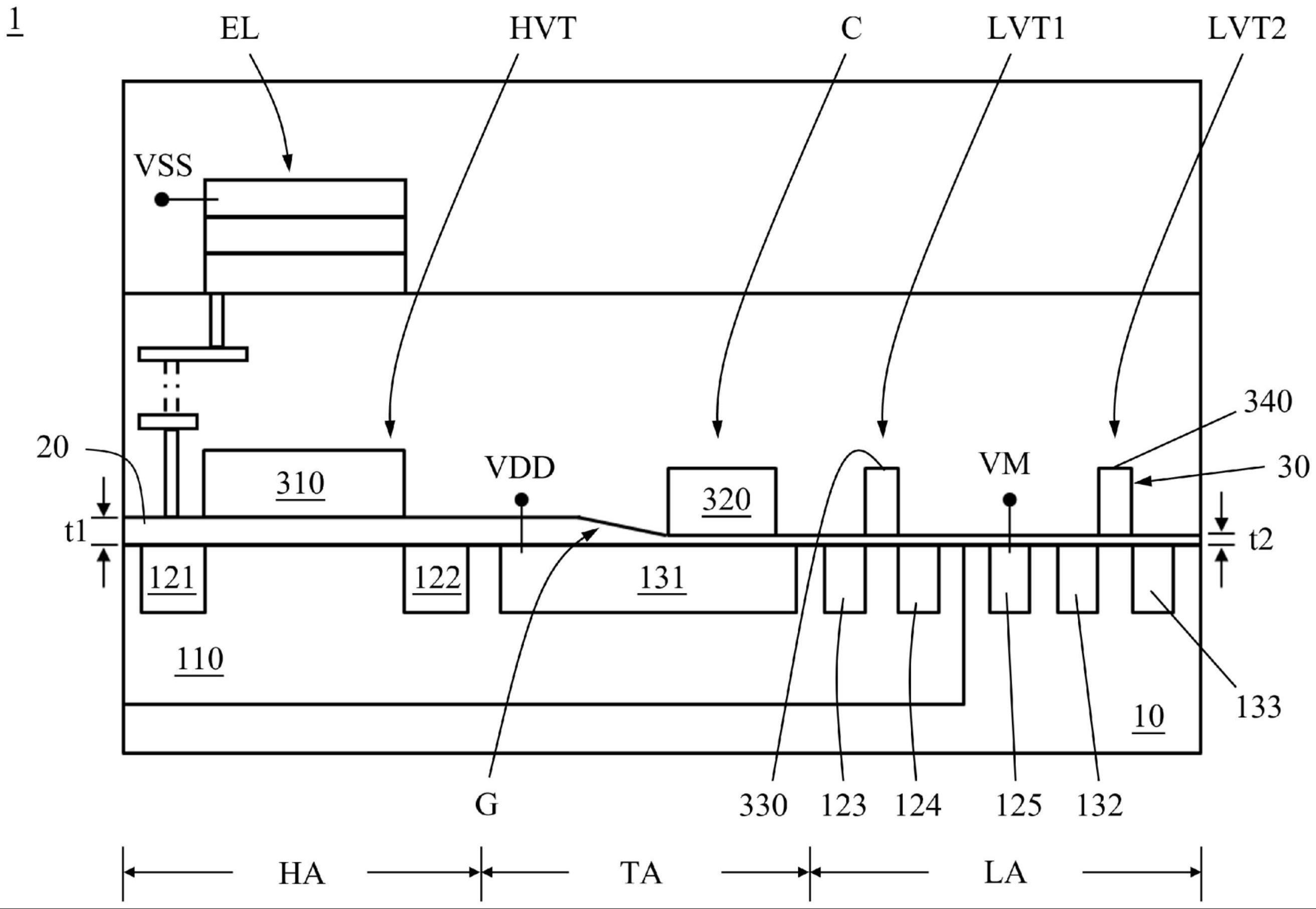

2、本申请实施例提供一种像素布局结构,适用于像素单元内。像素布局结构包括过渡区、高压元件区以及低压元件区。所述过渡区设置有第二型井接触区。所述第二型井接触区耦接于第一电压端,并且电性设置有一电容。所述高压元件区位于所述像素单元内的一侧,并且电性设置有第一型高压晶体管和电致发光元件。所述第一型高压晶体管和所述电容共享所述第二型井接触区,所述电致发光元件分别耦接于所述第一型高压晶体管和第二电压端。其中,所述第一电压端和所述第二电压端其中之一具有最高驱动电压,另一具有最低驱动电压。所述低压元件区位于所述像素单元内远离所述高压元件区的一侧,所述过渡区介于所述高压元件区和所述低压元件区之间。所述低压元件区电性设置有第二型低压晶体管,且所述第二型低压晶体管包括耦接于中间电压端的第一型井接触区。其中,所述中间电压端用以提供中间电压,所述中间电压介于所述最高驱动电压和所述最低驱动电压之间。

3、在本申请的一实施例中,所述低压元件区还电性设置有第一型低压晶体管,所述第一型低压晶体管和所述电容、所述第一型高压晶体管共享所述第二型井接触区。

4、在本申请的一实施例中,所述像素布局结构还包括绝缘层,自所述高压元件区延伸至所述低压元件区,并且在所述高压元件区内具有第一厚度、在所述低压元件区内具有第二厚度以及在所述过渡区内具有厚度梯度,所述第一厚度大于所述第二厚度,所述厚度梯度自所述高压元件区的一侧朝向所述低压元件区的一侧递减。

5、在本申请的一实施例中,所述电容位于所述厚度梯度靠近所述高压元件区的一侧、靠近所述低压元件区的一侧或位于所述厚度梯度上。

6、在本申请的一实施例中,所述像素布局结构还包括第一型基板。所述第一型基板内具有第二型井,所述第二型井涵盖所述高压元件区、所述过渡区以及部分的所述低压元件区,所述第二型井接触区位于所述第二型井内。

7、在本申请的一实施例中,所述像素布局结构在长度方向上具有第一边界和第二边界,且所述第一边界和所述第二边界之间具有第一预定距离;以及在宽度方向上具有第三边界和第四边界,且所述第三边界和所述第四边界之间具有第二预定距离,所述第一预定距离和所述第二预定距离不大于10微米。其中,所述高压元件区沿所述第一边界朝向所述第二边界配置,所述低压元件区沿所述第二边界朝向所述第一边界配置。

8、本申请实施例还提供一种电致发光显示器,包括阵列排列的多个像素单元,其中至少一像素单元包括像素布局结构。所述像素布局结构包括高压元件区、低压元件区以及介于所述高压元件区和所述低压元件区之间的过渡区。所述过渡区设置有第二型井接触区。所述第二型井接触区耦接于第一电压端,并且电性设置有电容。所述高压元件区位于所述像素单元内的一侧,并且电性设置有第一型高压晶体管和电致发光元件。所述第一型高压晶体管和所述电容共享所述第二型井接触区,所述电致发光元件分别耦接于所述第一型高压晶体管和第二电压端。其中,所述第一电压端和所述第二电压端其中之一具有最高驱动电压,另一具有最低驱动电压。所述低压元件区位于所述像素单元内远离所述高压元件区的一侧,并且电性设置有第二型低压晶体管。所述第二型低压晶体管包括耦接于中间电压端的第一型井接触区,其中所述中间电压端用以提供中间电压,其介于所述最高驱动电压和所述最低驱动电压之间。

9、本申请实施例所提供的像素布局结构在低压元件区设置中间电压端,提供介于像素单元使用到的最高和最低驱动电压之间的中间电压,用以设定第二型低压晶体管的运作电压。同时搭配电容和高压元件共享第二型井接触区作为主体(body)的配置方式,让像素布局结构应用于电致发光显示器时,高压元件和低压元件可以同时配置在有限面积的像素单元或子像素单元中,因此降低了晶体管必须占有的布局面积,而更容易实现于等于或小于10微米乘10微米的布局区域范围内,使得电致发光显示器中的像素单元或子像素单元的可配置数量增加,使像素密度获得具体提升。

技术特征:

1.一种像素布局结构,其特征在于,适用于像素单元内,所述像素布局结构包括:

2.如权利要求1所述的像素布局结构,其特征在于,所述低压元件区还电性设置有第一型低压晶体管,所述第一型低压晶体管和所述电容、所述第一型高压晶体管共享所述第二型井接触区。

3.如权利要求1所述的像素布局结构,其特征在于,还包括绝缘层,自所述高压元件区延伸至所述低压元件区,并且在所述高压元件区内具有第一厚度、在所述低压元件区内具有第二厚度以及在所述过渡区内具有厚度梯度,所述第一厚度大于所述第二厚度,所述厚度梯度自所述高压元件区的一侧朝向所述低压元件区的一侧递减。

4.如权利要求3所述的像素布局结构,其特征在于,所述电容位于所述厚度梯度靠近所述高压元件区的一侧、靠近所述低压元件区的一侧或位于所述厚度梯度上。

5.如权利要求1所述的像素布局结构,其特征在于,还包括第一型基板,所述第一型基板内具有第二型井,所述第二型井涵盖所述高压元件区、所述过渡区以及部分的所述低压元件区,所述第二型井接触区位于所述第二型井内。

6.如权利要求1所述的像素布局结构,其特征在于,在长度方向上具有第一边界和第二边界,且所述第一边界和所述第二边界之间具有第一预定距离,以及在宽度方向上具有第三边界和第四边界,且所述第三边界和所述第四边界之间具有第二预定距离,所述第一预定距离和所述第二预定距离不大于10微米,其中所述高压元件区沿所述第一边界朝向所述第二边界配置,所述低压元件区沿所述第二边界朝向所述第一边界配置。

7.一种电致发光显示器,其特征在于,包括阵列排列的多个像素单元,所述像素单元至少其中之一包括像素布局结构,所述像素布局结构包括:

8.如权利要求7所述的电致发光显示器,其特征在于,所述低压元件区还电性设置有第一型低压晶体管,所述第一型低压晶体管和所述电容、所述第一型高压晶体管共享所述第二型井接触区。

9.如权利要求8所述的电致发光显示器,其特征在于,还包括绝缘层,自所述高压元件区延伸至所述低压元件区,并且在所述高压元件区内具有第一厚度、在所述低压元件区内具有第二厚度以及在所述过渡区内具有厚度梯度,所述第一厚度大于所述第二厚度,所述厚度梯度自所述高压元件区的一侧朝向所述低压元件区的一侧递减。

10.如权利要求9所述的电致发光显示器,其特征在于,所述电容位于所述厚度梯度靠近所述高压元件区的一侧、靠近所述低压元件区的一侧或位于所述厚度梯度上。

11.如权利要求7所述的电致发光显示器,其特征在于,还包括第一型基板,所述第一型基板内具有第二型井,所述第二型井涵盖所述高压元件区、所述过渡区以及部分的所述低压元件区,所述第二型井接触区位于所述第二型井内。

12.如权利要求7所述的电致发光显示器,其特征在于,所述像素布局结构在长度方向上具有第一边界和第二边界,且所述第一边界和所述第二边界之间具有第一预定距离,以及在宽度方向上具有第三边界和第四边界,且所述第三边界和所述第四边界之间具有第二预定距离,所述第一预定距离和所述第二预定距离不大于10微米,其中所述高压元件区沿所述第一边界朝向所述第二边界配置,所述低压元件区沿所述第二边界朝向所述第一边界配置。

技术总结

本申请实施例提供一种像素布局结构和电致发光显示器,其中电致发光显示器内至少存在一像素单元包括此像素布局结构。像素布局结构包括高压元件区、低压元件区和过渡区。其中,高压元件区的第一型高压晶体管和过渡区的电容共享第二型井接触区,并且低压元件区的第二型低压晶体管包括耦接于中间电压端的第一型井接触区。通过此配置方式,调整各元件的运作电压,使像素电路可以在有限的子像素布局面积内正常运作,并解决像素密度无法提升的问题。

技术研发人员:郑士嵩,洪森全

受保护的技术使用者:超炫科技股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!