本申请涉及显示面板的驱动,具体涉及一种goa电路和显示面板。

背景技术:

1、goa(gate driver on array)技术即阵列基板行驱动技术,是利用薄膜晶体管液晶显示器阵列制程将栅极扫描驱动电路制作在薄膜晶体管阵列基板上,以实现逐行扫描的驱动方式。

2、goa驱动电路具备低成本(无需gate-ic)、无边框以及产品良率高(组装过程中的gate-driver不良)等优点,但goa电路对tft(thin film transistor,薄膜晶体管)的稳定性要求较高。goa电路很容易出现电路漏电的问题,使goa电路级传失效,出现显示异常。

技术实现思路

1、本申请实施例提供一种goa电路和显示面板,解决goa电路出现防漏电失效导致显示异常的技术问题。

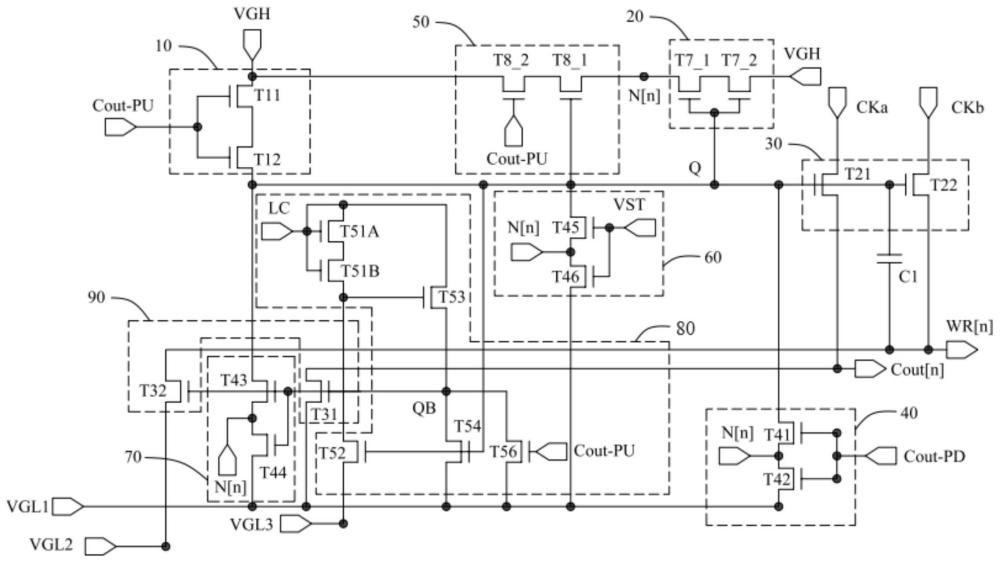

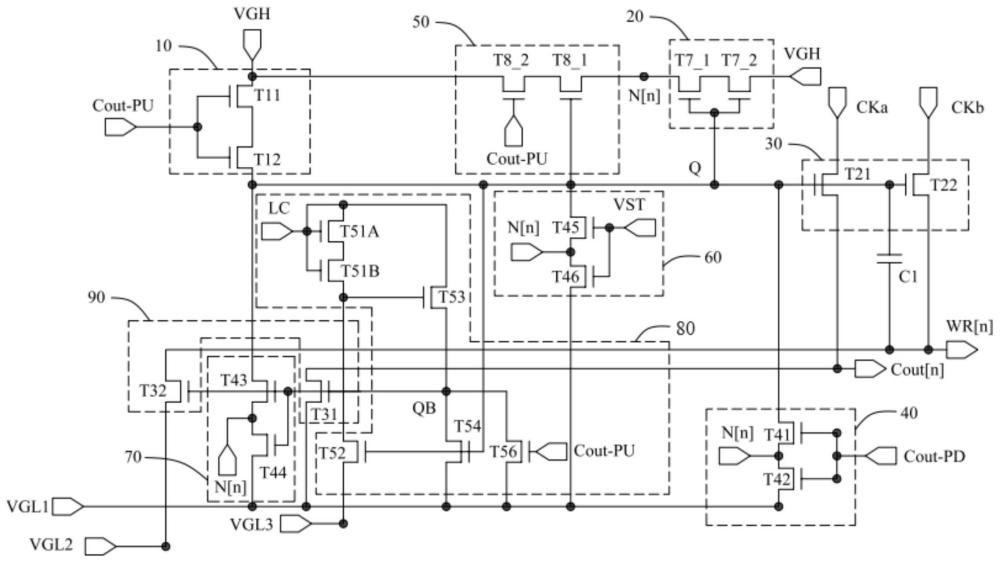

2、第一方面,本申请提供一种goa电路,包括:

3、上拉控制单元,与第一节点连接,用于将所述第一节点的电位拉高;

4、第一防漏电单元,所述第一防漏电单元的控制端与所述第一节点连接,所述第一防漏电单元的输出端与第二防漏电单元的输出端连接,所述第一防漏电单元的输入端与高电位信号端连接,所述第一防漏电单元用于在所述第一节点的电位处于高电位时开启工作,以阻断所述第一节点的漏电途径,使得所述第一节点充电至高电位;

5、上拉单元,与所述第一节点连接,用于将级传信号端和输出信号端的电位拉高;

6、下拉单元,所述下拉单元的输出端与所述第一节点连接,用于将所述第一节点的电位拉低;

7、第二防漏电单元,所述第二防漏电单元的第一控制端与所述第一节点连接,所述第二防漏电单元的输入端与所述上拉控制单元连接,所述第二防漏电单元用于在所述第一节点的电位处于低电位时开启,以阻断所述第一节点的漏电途径,使得所述第一节点充电至高电位,所述第二防漏电单元用于在所述第一节点的电位处于高电位时关闭。

8、在一些实施例中,所述第二防漏电单元包括:

9、第一晶体管和第二晶体管,所述第一晶体管的沟道类型与所述第二晶体管的沟道类型相反;

10、所述第一晶体管的漏极为所述第二防漏电单元的输出端,所述第一晶体管的源极与所述第二晶体管的漏极连接,所述第一晶体管的栅极为所述第二防漏电单元的第一控制端;

11、所述第二晶体管的源极为所述第二防漏电单元的输入端,所述第二晶体管的栅极与上拉控制信号端连接。

12、在一些实施例中,所述第一晶体管为p型mos管,所述第二晶体管为n型mos管。

13、在一些实施例中,所述第一防漏电单元包括:

14、第三晶体管和第四晶体管,所述第三晶体管的栅极和所述第四晶体管的栅极为所述第一防漏电单元的控制端;

15、所述第三晶体管的漏极为所述第一防漏电单元的输出端,所述第三晶体管的源极与所述第四晶体管的漏极连接;

16、所述第四晶体管的源极与高电位信号端连接。

17、在一些实施例中,所述下拉单元包括:

18、第五晶体管和第六晶体管;

19、所述第五晶体管的栅极和所述第六晶体管的栅极均与下拉控制信号端连接;

20、所述第五晶体管的源极与所述第一节点连接,所述第五晶体管的漏极和所述第六晶体管的源极与所述第一防漏电单元的输出端连接;

21、所述第六晶体管的漏极与第一低电位信号端连接。

22、在一些实施例中,所述上拉控制单元包括:

23、第七晶体管和第八晶体管;

24、所述第七晶体管的栅极和所述第八晶体管的栅极均与所述上拉控制信号端连接;

25、所述第七晶体管的源极与所述高电位信号端连接,所述第七晶体管的漏极与所述第八晶体管的源极连接;

26、所述第八晶体管的漏极与所述第一节点连接。

27、在一些实施例中,所述上拉单元包括:

28、第九晶体管和第十晶体管,所述第九晶体管的栅极和所述第十晶体管的栅极均与所述第一节点连接;

29、所述第九晶体管的源极与第一时钟信号端连接,所述第十晶体管的源极与第二时钟信号端连接,所述第九晶体管的漏极与所述级传信号端连接,所述第十晶体管的漏极与所述输出信号端连接。

30、在一些实施例中,所述goa电路还包括第一下拉维持单元,所述第一下拉维持单元包括:

31、第十一晶体管和第十二晶体管,所述第十一晶体管的栅极和第十二晶体管的栅极均与第二节点连接;

32、所述第十一晶体管的源极与所述第一节点连接,所述第十一晶体管的漏极和所述第十二晶体管的源极与所述第一防漏电单元的输出端连接;

33、所述第十二晶体管的漏极与所述第一低电位信号端连接。

34、在一些实施例中,所述goa电路还包括复位单元,与所述第一节点连接,所述复位单元包括:

35、第十三晶体管和第十四晶体管;

36、所述第十三晶体管的栅极和所述第十四晶体管的栅极均与全局复位信号端vs连接;

37、所述第十三晶体管的源极与所述第一节点连接,所述第十三晶体管的漏极和所述第十四晶体管的源极与所述第一防漏电单元的输出端连接;

38、所述第十四晶体管的漏极与所述第一低电位信号端连接。

39、第二方面,本申请还提供一种显示面板,包括第一方面所述的goa电路。

40、本申请提供的一种goa电路和显示面板,通过上拉控制单元与第一节点连接以拉高第一节点的电位,上拉单元的控制端与第一节点连接以拉高将级传信号端和输出信号端的电位,下拉单元的输出端与第一节点连接以拉低第一节点的电位,第一防漏电单元的输出端与第二防漏电单元的输出端连接,第一防漏电单元用于在第一节点为高电位时开启工作,以阻断所述第一节点的漏电途径,使得第一节点充电至高电位,第二防漏电单元的第一控制端与第一节点连接,第二防漏电单元的输入端与上拉控制单元连接,第二防漏电单元用于在第一节点的电位处于低电位时开启,以阻断所述第一节点的漏电途径,使得第一节点充电至高电位,提升goa电路充电过程的稳定性,使显示面板能够正常显示。

技术特征:1.一种goa电路,其特征在于,包括:

2.根据权利要求1所述的goa电路,其特征在于,所述第二防漏电单元(50)包括:

3.根据权利要求2所述的goa电路,其特征在于,所述第一晶体管(t8-1)为p型mos管,所述第二晶体管(t8-2)为n型mos管。

4.根据权利要求2所述的goa电路,其特征在于,所述第一防漏电单元(20)包括:

5.根据权利要求4所述的goa电路,其特征在于,所述下拉单元(40)包括:

6.根据权利要求5所述的goa电路,其特征在于,所述上拉控制单元(10)包括:

7.根据权利要求6所述的goa电路,其特征在于,所述上拉单元(30)包括:

8.根据权利要求7所述的goa电路,其特征在于,所述goa电路还包括第一下拉维持单元(70),所述第一下拉维持单元(70)包括:

9.根据权利要求8所述的goa电路,其特征在于,所述goa电路还包括复位单元(60),与所述第一节点(q)连接,所述复位单元(60)包括:

10.一种显示面板,其特征在于,包括如权利要求1至9任一项所述的goa电路。

技术总结本申请公开了一种GOA电路和显示面板,所述GOA电路新增了第二防漏电单元,所述第二防漏电单元的输出端与第一防漏电单元的输出端连接,所述第二防漏电单元的输入端与所述上拉控制单元连接,所述第二防漏电单元的第一控制端与所述第一节点连接,所述第二防漏电单元用于在所述第一节点的电位处于低电位时阻断所述第一节点的漏电途径,使得所述第一节点充电至高电位,第一防漏电单元在所述第一节点处于高电位时开启工作,阻断所述第一节点的漏电途径,使得所述第一节点充电至高电位。本申请提升GOA电路充电过程的稳定性,使显示面板能够正常显示。

技术研发人员:周翔,韩佰祥,李广耀

受保护的技术使用者:深圳市华星光电半导体显示技术有限公司

技术研发日:技术公布日:2024/2/25