显示驱动芯片及相关装置和方法与流程

本公开涉及显示,特别涉及一种显示驱动芯片及相关装置和方法。

背景技术:

1、低温多晶硅(low temperature poly-silicon,简称ltps)类的显示面板需要保持较高的刷新率,因此应用处理器(application processor,ap)需要以较高的帧率送图给显示面板。若应用处理器本身在低刷新率应用场景,例如小说阅读、网页浏览、电子书翻页等应用场景,应用处理器目前是通过频繁刷新同一图像帧来适配显示面板的高帧率,这样不仅导致从应用处理器到显示驱动芯片(display driver integrated circuit,简称ddic)的不必要的数据传输功耗,而且显示驱动芯片内各算法模块频繁针对同一图像帧进行相同处理也会产生较多不必要的功耗。

技术实现思路

1、鉴于上述问题,本公开提供了一种显示驱动芯片及相关装置和方法,旨在通过较低的功耗实现显示面板的高刷新率。

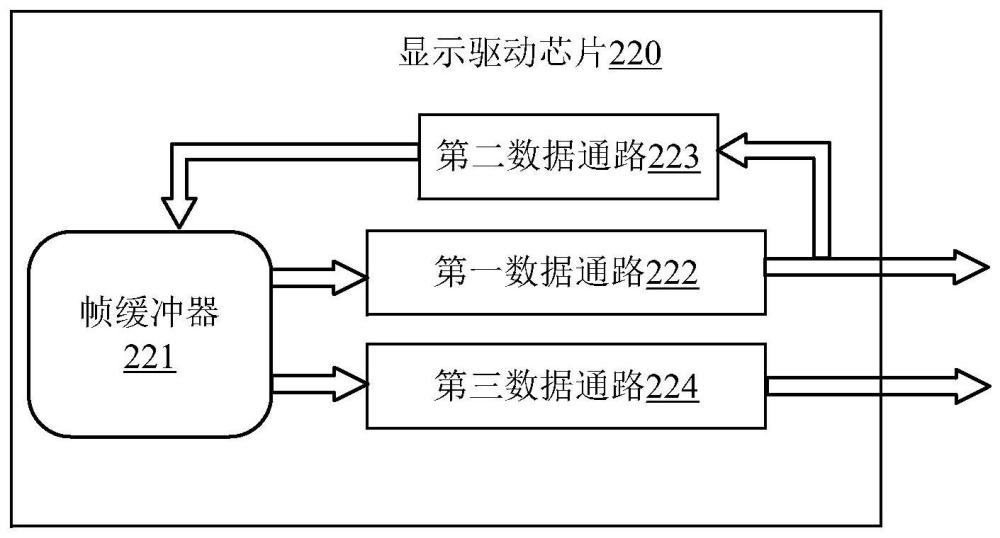

2、根据本公开的第一方面,提供一种显示驱动芯片,包括:

3、帧缓冲器;

4、第一数据通路,用于将应用处理器发送的图像帧处理为显示面板待显示的图像数据并向所述显示面板输出处理得到的所述图像数据;

5、第二数据通路,用于将处理得到的所述图像数据向所述帧缓冲器传输;

6、第三数据通路,用于将所述帧缓冲器内缓冲的图像数据向所述显示面板传输以实现所述显示面板对所述图像帧的刷新。

7、可选地,所述显示驱动芯片还包括:

8、多路选择器,输入端分别与所述第一数据通路的输出端和所述第三数据通路的输出端连接,输出端与所述显示面板连接;

9、其中,所述多路选择器的输入端,在所述应用处理器发送所述图像帧的情况下选通所述第一数据通路的输出端,在所述应用处理器刷新所述图像帧的情况下选通所述第三数据通路的输出端。

10、可选地,所述应用处理器输出的图像帧缓冲在所述帧缓冲器中;

11、所述第一数据通路的输入端和所述第三数据通路的输入端皆与所述帧缓冲器连接。

12、可选地,所述第二数据通路在所述应用处理器输出图像帧的频率适配所述显示面板的刷新率的情况下关闭。

13、可选地,所述第二数据通路上设置有编码器,所述编码器用于对所述第一数据通路输出的图像数据进行编码,编码后的图像数据被传输到所述帧缓冲器;

14、所述第三数据通路上设置有解码器,所述帧缓冲器内缓冲的编码后的图像数据传输到所述显示面板之前经所述解码器解码,所述显示面板接收解码后的图像数据。

15、可选地,所述第三数据通路上还设置有行缓冲器,以使所述第三数据通路上的数据传输延迟与所述第一数据通路上的数据传输延迟一致。

16、可选地,所述行缓冲器在所述第三数据通路上设置在所述解码器和所述帧缓冲器之间或者设置在所述解码器和所述显示面板之间。

17、根据本公开的第二方面,提供一种显示装置,包括:

18、应用处理器,用于发送图像帧;

19、第一方面所述的任一种显示驱动芯片,与所述应用处理器连接,用于将所述图像帧处理为待显示的图像数据并输出处理得到的所述图像数据;

20、显示面板,与所述显示驱动芯片连接,用于显示所述显示驱动芯片输出的图像数据。

21、可选地,所述应用处理器通过向所述显示驱动芯片发送所述图像帧的刷新指令来指示所述显示驱动芯片刷新所述图像帧。

22、根据本公开的第三方面,提供一种应用第一方面所述的任一种显示驱动芯片进行显示驱动的方法,包括:

23、将应用处理器发送的图像帧处理为显示面板待显示的图像数据并向所述显示面板输出处理得到的所述图像数据;

24、将处理得到的所述图像数据向帧缓冲器传输;

25、将所述帧缓冲器内缓冲的图像数据向所述显示面板传输以实现所述显示面板对所述图像帧的刷新。

26、本公开带来了以下有益效果:

27、本公开所提供的显示驱动芯片包括:帧缓冲器;第一数据通路,用于将应用处理器发送的图像帧处理为显示面板待显示的图像数据并向显示面板输出处理得到的图像数据;第二数据通路,用于将处理得到的图像数据向帧缓冲器传输;第三数据通路,用于将帧缓冲器内缓冲的图像数据向显示面板传输以实现显示面板对图像帧的刷新。因而,显示面板对图像帧的刷新不再需要重复执行图像帧处理为图像数据的过程,这样应用处理器本身在低刷新率应用场景时显示驱动芯片能够通过自刷新适配显示面板的高刷新率,从而有效降低了功耗。

28、本公开的其他特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本公开而了解。本公开的目的和其他优点在说明书以及附图中所特别指出的结构来实现和获得。

29、为使本公开的上述目的、特征和优点能更明显易懂,下文特举较佳实施例,并配合所附附图,作详细说明如下。

技术特征:

1.一种显示驱动芯片,包括:

2.根据权利要求1所述的显示驱动芯片,还包括:

3.根据权利要求2所述的显示驱动芯片,其中,

4.根据权利要求1所述的显示驱动芯片,其中,所述第二数据通路在所述应用处理器输出图像帧的频率适配所述显示面板的刷新率的情况下关闭。

5.根据权利要求1所述的显示驱动芯片,其中,

6.根据权利要求5所述的显示驱动芯片,其中,所述第三数据通路上还设置有行缓冲器,以使所述第三数据通路上的数据传输延迟与所述第一数据通路上的数据传输延迟一致。

7.根据权利要求6所述的显示驱动芯片,其中,所述行缓冲器在所述第三数据通路上设置在所述解码器和所述帧缓冲器之间或者设置在所述解码器和所述显示面板之间。

8.一种显示装置,包括:

9.根据权利要求8所述的显示装置,其中,所述应用处理器通过向所述显示驱动芯片发送所述图像帧的刷新指令来指示所述显示驱动芯片刷新所述图像帧。

10.一种应用权利要求1-7中任一项所述的显示驱动芯片进行显示驱动的方法,包括:

技术总结

本公开提供了一种显示驱动芯片及相关装置和方法,该显示驱动芯片包括:帧缓冲器;第一数据通路,用于将应用处理器发送的图像帧处理为显示面板待显示的图像数据并向显示面板输出处理得到的图像数据;第二数据通路,用于将处理得到的图像数据向帧缓冲器传输;第三数据通路,用于将帧缓冲器内缓冲的图像数据向显示面板传输以实现显示面板对图像帧的刷新。本公开能够通过较低的功耗实现显示面板的高刷新率。

技术研发人员:徐阳,李蓬勃,曲孔宁,刘宏辉

受保护的技术使用者:北京集创北方科技股份有限公司

技术研发日:

技术公布日:2024/2/19

- 还没有人留言评论。精彩留言会获得点赞!