栅极驱动电路及显示面板的制作方法

本申请涉及显示,具体涉及一种栅极驱动电路及显示面板。

背景技术:

1、显示面板作为电子设备的显示部件,已经得到广泛应用,而栅极驱动电路是显示面板的一个重要组成部分。

2、因此,栅极驱动电路的稳定性是衡量信赖性的重要参数。然而,栅极驱动电路内部的节点电位出现异常,会降低稳定性,导致显示不良。

技术实现思路

1、本申请提供一种栅极驱动电路及显示面板,以缓解栅极驱动信号在一帧中的脉冲数量异常导致稳定性较低的技术问题。

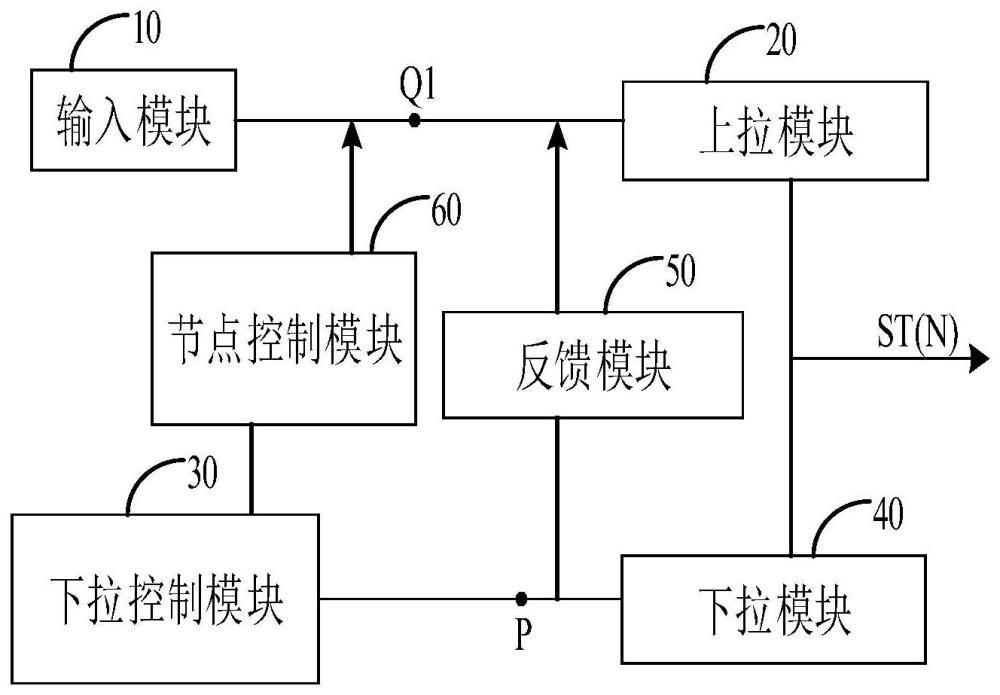

2、第一方面,本申请提供一种栅极驱动电路,该栅极驱动电路包括移位寄存器,移位寄存器包括输入模块、上拉模块、下拉模块、反馈模块、下拉控制模块以及节点控制模块,输入模块与正向扫描控制线、第一控制线以及上拉节点连接;上拉模块与上拉节点、第一时钟线以及栅极驱动线连接;下拉模块与下拉节点、栅极驱动线以及低电位线连接;反馈模块与下拉节点、低电位线以及上拉节点连接;下拉控制模块包括第一晶体管、第二晶体管以及第三晶体管,第一晶体管与第二时钟线、正向扫描控制线以及第一节点连接,第二晶体管与第三时钟线、反向扫描控制线以及第一节点连接,第三晶体管与第一节点、高电位线以及下拉节点连接;节点控制模块与上拉节点、第一节点以及低电位线连接,节点控制模块根据第一节点的电位拉低上拉节点的电位至低电位线的电位。

3、在其中一些实施方式中,节点控制模块包括第四晶体管,第四晶体管的第一极与上拉节点连接,第四晶体管的第二极与低电位线连接,第四晶体管的栅极与第一节点连接,第四晶体管为n沟道型晶体管。

4、在其中一些实施方式中,移位寄存器还包括第五晶体管和第六晶体管,第五晶体管与反向扫描控制线、第二控制线以及上拉节点连接;第六晶体管与第五晶体管、上拉节点、低电位线以及下拉节点连接。

5、在其中一些实施方式中,栅极驱动线用于传输第n级栅极驱动信号;第五晶体管的栅极与第二控制线连接;栅极驱动电路包括级联的多个移位寄存器,在栅极驱动电路的尾级移位寄存器中,第二控制线为起始线,起始线用于传输下帧的起始信号;在栅极驱动电路的非尾级移位寄存器中,第二控制线为第n+2级栅极驱动线,第n+2级栅极驱动线用于传输第n+2级栅极驱动信号。

6、在其中一些实施方式中,尾级移位寄存器设置有节点控制模块,非尾级移位寄存器未设置有节点控制模块。

7、在其中一些实施方式中,输入模块包括输入晶体管,输入晶体管的第一极与正向扫描控制线连接,输入晶体管的第二极与上拉节点连接,输入晶体管的栅极与第一控制线连接。

8、在其中一些实施方式中,在栅极驱动电路的首级移位寄存器中,第一控制线为起始线,起始线用于传输本帧的起始信号;在栅极驱动电路的非首级移位寄存器中,第一控制线为第n-2级栅极驱动线,第n-2级栅极驱动线用于传输第n-2级栅极驱动信号。

9、在其中一些实施方式中,尾级移位寄存器、首级移位寄存器均设置有节点控制模块,尾级移位寄存器与首级移位寄存器之间的移位寄存器未设置有节点控制模块。

10、在其中一些实施方式中,移位寄存器还包括第一全局晶体管、第二全局晶体管以及第三全局晶体管,第一全局晶体管的第一极与栅极驱动线连接,第一全局晶体管的第二极与第一全局晶体管的栅极、第一全局控制线连接;第二全局晶体管的栅极与第一全局控制线连接,第二全局晶体管的第一极与下拉节点连接,第二全局晶体管的第二极与低电位线连接;第三全局晶体管的第一极与栅极驱动线连接,第三全局晶体管的第二极与低电位线连接,第三全局晶体管的栅极与第二全局控制线连接。

11、在其中一些实施方式中,栅极驱动电路包括级联的多个移位寄存器,栅极驱动电路中的每个移位寄存器均设置有节点控制模块。

12、第二方面,本申请提供一种显示面板,该显示面板包括上述的栅极驱动电路。

13、本申请提供的栅极驱动电路及显示面板,通过新增的节点控制模块可以根据第一节点的电位拉低上拉节点的电位至低电位线的电位,以降低或者防止上拉模块异常打开,使得其输出的栅极驱动信号在一帧中的脉冲数量与预期一致,从而改善或者避免了栅极驱动信号在一帧中脉冲数量异常的风险,提高了栅极驱动电路的稳定性。

技术特征:

1.一种栅极驱动电路,其特征在于,所述栅极驱动电路包括移位寄存器,所述移位寄存器包括:

2.根据权利要求1所述的栅极驱动电路,其特征在于,所述节点控制模块包括第四晶体管,所述第四晶体管的第一极与所述上拉节点连接,所述第四晶体管的第二极与所述低电位线连接,所述第四晶体管的栅极与所述第一节点连接,所述第四晶体管为n沟道型晶体管。

3.根据权利要求2所述的栅极驱动电路,其特征在于,所述移位寄存器还包括:

4.根据权利要求3所述的栅极驱动电路,其特征在于,所述栅极驱动线用于传输第n级栅极驱动信号;所述第五晶体管的栅极与所述第二控制线连接;

5.根据权利要求4所述的栅极驱动电路,其特征在于,所述尾级移位寄存器设置有所述节点控制模块,所述非尾级移位寄存器未设置有所述节点控制模块。

6.根据权利要求4所述的栅极驱动电路,其特征在于,所述输入模块包括输入晶体管,所述输入晶体管的第一极与所述正向扫描控制线连接,所述输入晶体管的第二极与所述上拉节点连接,所述输入晶体管的栅极与所述第一控制线连接。

7.根据权利要求6所述的栅极驱动电路,其特征在于,在所述栅极驱动电路的首级移位寄存器中,所述第一控制线为所述起始线,所述起始线用于传输本帧的起始信号;在所述栅极驱动电路的非首级移位寄存器中,所述第一控制线为第n-2级栅极驱动线,所述第n-2级栅极驱动线用于传输第n-2级栅极驱动信号。

8.根据权利要求7所述的栅极驱动电路,其特征在于,所述尾级移位寄存器、所述首级移位寄存器均设置有所述节点控制模块,所述尾级移位寄存器与所述首级移位寄存器之间的移位寄存器未设置有所述节点控制模块。

9.根据权利要求3所述的栅极驱动电路,其特征在于,所述移位寄存器还包括:

10.根据权利要求9所述的栅极驱动电路,其特征在于,所述栅极驱动电路包括级联的多个所述移位寄存器,所述栅极驱动电路中的每个所述移位寄存器均设置有所述节点控制模块。

11.一种显示面板,其特征在于,所述显示面板包括如权利要求1-10任一项所述的栅极驱动电路。

技术总结

本申请公开了一种栅极驱动电路及显示面板,该栅极驱动电路包括移位寄存器,移位寄存器包括输入模块、上拉模块、下拉模块、反馈模块、下拉控制模块以及节点控制模块,通过新增的节点控制模块可以根据第一节点的电位拉低上拉节点的电位至低电位线的电位,以降低或者防止上拉模块异常打开,使得其输出的栅极驱动信号在一帧中的脉冲数量与预期一致,从而改善或者避免了栅极驱动信号在一帧中脉冲数量异常的风险,提高了栅极驱动电路的稳定性。

技术研发人员:李明月,田超,王超

受保护的技术使用者:武汉华星光电技术有限公司

技术研发日:

技术公布日:2024/7/15

- 还没有人留言评论。精彩留言会获得点赞!