移位寄存器单元及驱动方法、栅极驱动电路及显示面板与流程

本发明涉及显示,尤其涉及一种移位寄存器单元及驱动方法、栅极驱动电路及显示面板。

背景技术:

1、显示面板中,设置在非显示区的驱动电路是不可或缺的电路结构,用于实现显示面板的显示、触控等功能。

2、驱动电路通常由多级移位寄存器构成,驱动芯片通过信号线给驱动电路中每级移位寄存器提供驱动信号以使驱动电路正常运转。

3、然而,现有移位寄存器的输出不稳定,影响显示效果。

技术实现思路

1、本发明提供了一种移位寄存器单元及驱动方法、栅极驱动电路及显示面板,以解决现有移位寄存器输出不稳定的问题。

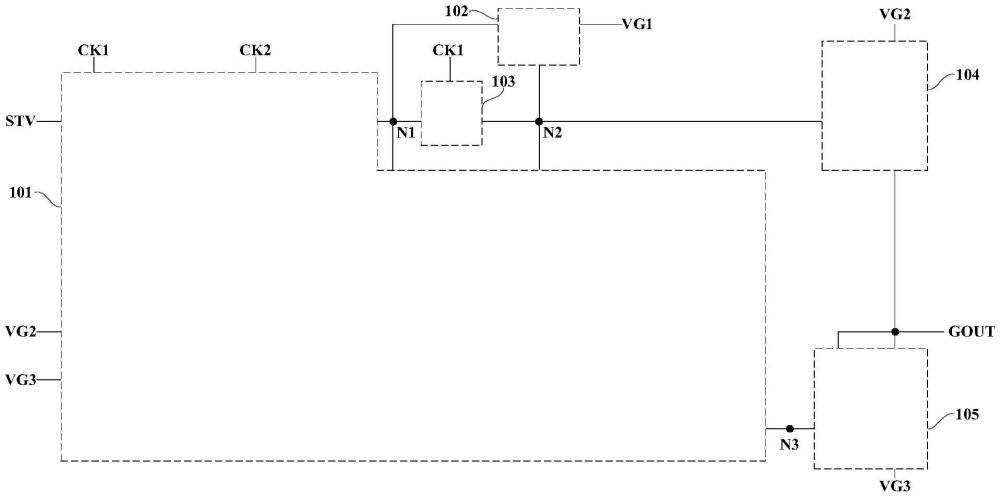

2、根据本发明的一方面,提供了一种移位寄存器单元,包括:

3、输入模块,至少连接第一节点和第二节点,用于控制所述第一节点的电位和所述第二节点的电位;

4、第一控制模块,连接在第一电源端和所述第一节点之间,所述第一控制模块的控制端连接所述第二节点,用于响应于所述第二节点的电位,控制所述第一电源端和所述第一节点之间的通断;

5、第二控制模块,连接在所述第一节点和所述第二节点之间,所述第二控制模块的控制端接收第一时钟端提供的第一时钟信号,用于响应于所述第一时钟端的第一时钟信号,控制所述第一节点和所述第二节点之间的通断;

6、输出模块,连接在第二电源端和移位输出端之间,所述输出模块的控制端连接所述第二节点,用于响应于所述第二节点的电位,控制所述第二电源端和所述移位输出端之间的通断。

7、根据本发明的另一方面,提供了一种移位寄存器单元的驱动方法,所述移位寄存器单元为如前所述的移位寄存器单元;

8、所述移位寄存器单元的驱动方法包括:

9、非输出阶段,所述输入模块控制所述第二节点的电位,使所述第一控制模块和所述输出模块同时切换为关断状态;

10、输出阶段,所述输入模块控制所述第二控制模块的通断状态和所述第二节点的电位,使所述第一控制模块和所述输出模块同时切换为导通状态,所述第一电源端的信号写入所述第一节点。

11、根据本发明的另一方面,提供了一种栅极驱动电路,包括如前所述的移位寄存器单元。

12、根据本发明的另一方面,提供了一种显示面板,包括如前所述的栅极驱动电路。

13、本发明中,移位寄存器单元中增设第一控制模块,第一控制模块连接在第一电源端和第一节点之间,第二节点分别连接第一控制模块的控制端和输出模块的控制端,第二控制模块连接在第一节点和第二节点之间,第二控制模块的控制端接收第一时钟信号,输入模块控制第一节点和第二节点的电位。本发明中,第二节点的电位为导通电平时,控制第一控制模块和输出模块同时导通,则第一电源端的第一电源信号写入第一节点,第一电源端和输入模块共同作用以调节第一节点的电位,以此减少第一节点对第二节点的耦合电荷量,进而减小第二节点的电位被耦合波动的幅度,如此可降低输出模块开启时移位输出端输出第二电源信号的抖动程度,提高移位寄存器单元的输出稳定性,提升显示效果。

14、应当理解,本部分所描述的内容并非旨在标识本发明的实施例的关键或重要特征,也不用于限制本发明的范围。本发明的其它特征将通过以下的说明书而变得容易理解。

技术特征:

1.一种移位寄存器单元,其特征在于,包括:

2.根据权利要求1所述的移位寄存器单元,其特征在于,所述输出模块包括第一晶体管和第一电容;所述第一晶体管的栅极连接所述第二节点,所述第一晶体管连接在所述第二电源端和所述移位输出端之间;所述第一电容连接在所述第二电源端和所述第二节点之间;

3.根据权利要求2所述的移位寄存器单元,其特征在于,所述第一控制模块包括第三晶体管;

4.根据权利要求3所述的移位寄存器单元,其特征在于,所述第三晶体管为pmos,所述第一电源端提供的第一电源信号为低电压;

5.根据权利要求3所述的移位寄存器单元,其特征在于,所述输入模块用于控制所述第一节点的电位在第一低电平和第一高电平之间切换;

6.根据权利要求3所述的移位寄存器单元,其特征在于,所述第一晶体管的宽长比大于所述第三晶体管的宽长比。

7.根据权利要求3所述的移位寄存器单元,其特征在于,所述第三晶体管的宽长比大于所述第二晶体管的宽长比。

8.根据权利要求3所述的移位寄存器单元,其特征在于,所述第一晶体管和所述第三晶体管均为nmos;或者,所述第一晶体管和所述第三晶体管均为pmos。

9.根据权利要求3所述的移位寄存器单元,其特征在于,所述第一晶体管为nmos,所述第二电源端复用为所述第一电源端。

10.根据权利要求3所述的移位寄存器单元,其特征在于,所述第一晶体管包括第一栅极金属层、第一源极金属层和第一漏极金属层;

11.根据权利要求2所述的移位寄存器单元,其特征在于,所述输入模块还连接第三节点,用于控制所述第三节点的电位;

12.根据权利要求11所述的移位寄存器单元,其特征在于,所述输出控制模块包括第四晶体管和第二电容;

13.根据权利要求12所述的移位寄存器单元,其特征在于,所述第一电容的电容量大于所述第二电容的电容量。

14.根据权利要求12所述的移位寄存器单元,其特征在于,所述第一晶体管为pmos,所述第三电源端复用为所述第一电源端。

15.根据权利要求2所述的移位寄存器单元,其特征在于,所述输入模块还连接第四节点,用于控制所述第四节点的电位;

16.根据权利要求15所述的移位寄存器单元,其特征在于,所述第一电容的电容量大于所述第三电容的电容量。

17.根据权利要求1所述的移位寄存器单元,其特征在于,所述输入模块还连接第三节点和第四节点,用于控制所述第三节点的电位和所述第四节点的电位;

18.根据权利要求17所述的移位寄存器单元,其特征在于,所述第八晶体管包括第一子晶体管和第二子晶体管;所述第九晶体管包括第三子晶体管和第四子晶体管;

19.根据权利要求18所述的移位寄存器单元,其特征在于,所述输入模块还包括:第十三晶体管,第十四晶体管和第四电容;

20.根据权利要求18所述的移位寄存器单元,其特征在于,所述输入模块还包括:第十五晶体管;

21.一种移位寄存器单元的驱动方法,其特征在于,所述移位寄存器单元为权利要求1-20任一项所述的移位寄存器单元;

22.一种栅极驱动电路,其特征在于,包括权利要求1-20任一项所述的移位寄存器单元。

23.一种显示面板,其特征在于,包括权利要求22所述的栅极驱动电路。

技术总结

本发明公开了一种移位寄存器单元及驱动方法、栅极驱动电路及显示面板,该移位寄存器单元包括:输入模块,至少连接第一节点和第二节点;第一控制模块,连接在第一电源端和第一节点之间,第一控制模块的控制端连接第二节点;第二控制模块,连接在第一节点和第二节点之间,第二控制模块的控制端接收第一时钟端提供的第一时钟信号;输出模块,连接在第二电源端和移位输出端之间,输出模块的控制端连接第二节点。本发明中,增设第一控制模块,通过第一电源端和输入模块共同调节第一节点的电位,减少第一节点对第二节点的耦合电荷量,进而减小第二节点的电位被耦合波动的幅度,提高移位寄存器单元的输出稳定性,提升显示效果。

技术研发人员:陈昱

受保护的技术使用者:武汉天马微电子有限公司

技术研发日:

技术公布日:2024/11/14

- 还没有人留言评论。精彩留言会获得点赞!