栅极驱动电路、显示面板及显示面板驱动方法与流程

本申请涉及显示,尤其涉及一种栅极驱动电路、显示面板及显示面板驱动方法。

背景技术:

1、阵列基板栅极驱动电路(gate-driver on array,goa)是将栅极驱动电路集成在显示面板的阵列基板上,利用薄膜晶体管(thin film transistor,tft)实现逐行输出栅极扫描信号的驱动方式。栅极驱动电路包括多级级联的栅极驱动单元。以第n级栅极驱动单元为例,第n级栅极驱动单元的q点是控制栅极扫描信号g(n)高电位的相关薄膜晶体管的栅极的点,q点电压的稳定性决定了栅极扫描信号g(n)的稳定性,其中,n为正整数。

2、相关技术中,上拉控制模块由薄膜晶体管t11组成。上拉控制模块有两种常见的接法,分别为二极管接法、vgh接法。无论是哪种接法,如果薄膜晶体管t11的阈值电压发生负向偏移(简称“负偏”),或者薄膜晶体管t11在高温下工作,则qn点的漏电增加。

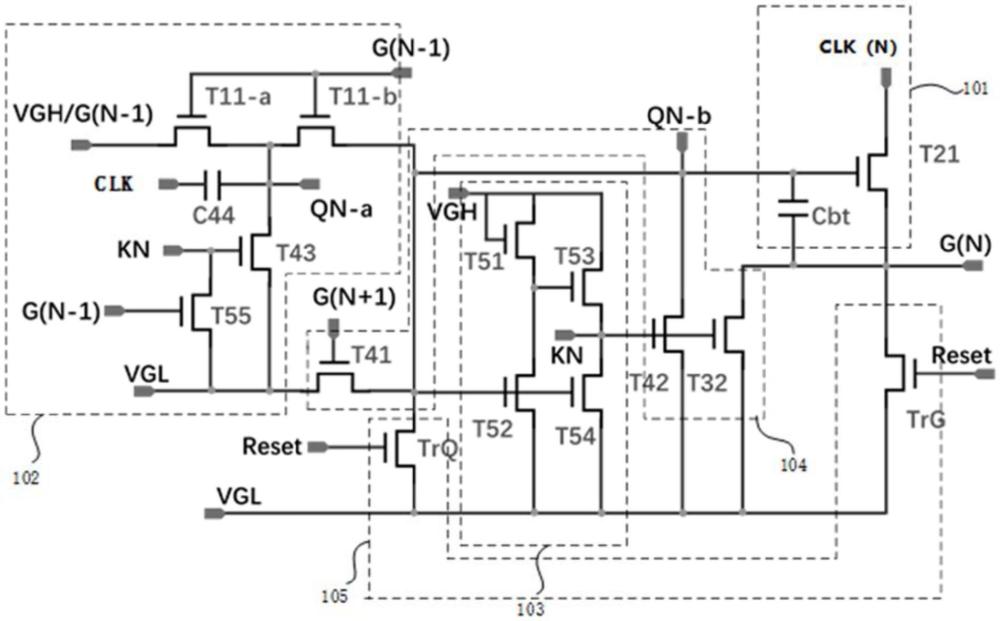

3、图1示出相关技术中的栅极驱动单元的示意图。如图1所示,相关技术的栅极驱动单元利用薄膜晶体管电路逐行输出栅极信号g(n),n为该栅极驱动单元的级数。在图1的栅极驱动单元中,通过将上一级栅极驱动单元的栅极信号g(n-1)拉高,进而打开上拉控制模块的薄膜晶体管t11,从而将qn点电位拉高。由于qn点电位拉高,上拉单元的薄膜晶体管t21打开,以输出栅极信号g(n),同时通过下级栅极驱动单元的栅极信号g(n+1)控制下拉单元的薄膜晶体管t41打开,进而拉低qn点电位,实现级传。因此,在栅极驱动电路的工作中,qn点的电位稳定对栅极驱动电路的运行至关重要。

4、图2示出相关技术中的上拉控制模块的示意图。如图2所示,相关技术的两种常见的接法中,(a)为二极管接法,(b)为vgh接法。在二极管接法设计中,当上一级栅极驱动单元的栅极信号g(n-1)电位降低,使得薄膜晶体管t11关闭后,由于qn点向g(n-1)漏电,qn点的工作电位会降低。如果qn点工作电位降低幅度过大,薄膜晶体管t21打开不完全,会导致g(n)充电不足。随着级传的进行,该效应累积最终导致栅极信号g(n)失效。在vgh接法设计中,薄膜晶体管t11的源极和漏极均为高电位,可以改善qn点工作期间的漏电,但是在qn点低电位期间,漏电的存在会使qn点电位升高,进而使薄膜晶体管t21微微打开,经过级传的积累,会导致栅极信号g(n)产生循环峰。

技术实现思路

1、有鉴于此,本申请提出了一种栅极驱动电路、显示面板及显示面板驱动方法,能够降低q点的漏电程度,降低q点漏电对栅极信号输出的影响,从而提高栅极驱动电路在高温等漏电严重环境下工作的稳定性。

2、根据本申请的一方面,提供了一种栅极驱动电路,所述栅极驱动电路包括多级级联的栅极驱动单元,第n级栅极驱动单元包括:上拉模块,电连接于第二q点,所述上拉模块用于输出第n级栅极驱动单元的栅极信号,n为正整数;上拉控制模块,包括第一晶体管和第二晶体管,所述第一晶体管的栅极和所述第二晶体管的栅极均电连接于第n-1级栅极驱动单元的栅极信号端,第n-1级栅极驱动单元的栅极信号端用于输出第n-1级栅极驱动单元的栅极信号,所述第一晶体管的源极电连接于高电压端或第n-1级栅极驱动单元的栅极信号端,所述第一晶体管的漏极电连接于第二晶体管的源极;所述第二晶体管的栅极电连接于述第一晶体管的栅极,所述第二晶体管的漏极电连接于该第n级栅极驱动单元的第二q点,所述第一晶体管的漏极以及所述第二晶体管的源极均电连接于第一q点;其中,所述第一q点的电位和所述第二q点的电位相一致。

3、根据本申请的又一方面,提供了一种显示面板,所述显示面板包括所述栅极驱动电路。

4、根据本申请的又一方面,提供了一种显示面板驱动方法,所述显示面板驱动方法应用于所述的栅极驱动电路,所述显示面板驱动方法包括:在第一时刻,控制第n-1级栅极驱动单元的栅极信号端的电位从低电位变为高电位,以使第n级栅极驱动单元的第一q点和第二q点均升高至第一高电位;在第二时刻,控制第n-1级栅极驱动单元的栅极信号端的电位从高电位变为低电位,使所述第一q点的电位和第二q点的电位维持在第一高电位;在第三时刻,控制第n级栅极驱动单元的时钟信号端从低电位变为高电位,使所述第一q点的电位以及所述第二q点的电位被耦合至第二高电位,其中,在第一时刻、第二时刻和第三时刻,所述第一q点的电位和所述第二q点的电位相一致。

5、通过在上拉控制模块中设置共栅极结构的两上拉控制晶体管,并将其中一上拉控制晶体管的源极以及另一上拉控制晶体管的漏极均电连接于第一q点,将第一q点电连接于第n级栅极驱动单元的低电压端,且第一q点的电位和第二q点的电位相一致,本申请能够降低q点的漏电程度,降低q点漏电对栅极信号输出的影响,从而提高栅极驱动电路在高温等漏电严重环境下工作的稳定性。

技术特征:

1.一种栅极驱动电路,其特征在于,所述栅极驱动电路包括多级级联的栅极驱动单元,第n级栅极驱动单元包括:

2.根据权利要求1所述的栅极驱动电路,其特征在于,第n级栅极驱动单元的所述上拉控制模块还包括:

3.根据权利要求2所述的栅极驱动电路,其特征在于,第n级栅极驱动单元的所述上拉控制模块还包括:

4.根据权利要求3所述的栅极驱动电路,其特征在于,第n级栅极驱动单元的所述上拉控制模块还包括:

5.根据权利要求4所述的栅极驱动电路,其特征在于,第n级栅极驱动单元的所述上拉模块包括:

6.根据权利要求5所述的栅极驱动电路,其特征在于,所述第一电容和所述第二电容均为可变电容,通过调节所述第一电容的容值和所述第二电容的容值,使所述第一q点的电位和所述第二q点的电位保持一致。

7.根据权利要求5所述的栅极驱动电路,其特征在于,第n级栅极驱动单元还包括下拉模块,第n级栅极驱动单元的所述下拉模块包括:

8.一种显示面板,其特征在于,所述显示面板包括如权利要求1-7任一项所述的栅极驱动电路。

9.一种显示面板驱动方法,其特征在于,所述显示面板驱动方法应用于如权利要求1-7任一项所述的栅极驱动电路,所述显示面板驱动方法包括:

技术总结

本申请涉及一种栅极驱动电路、显示面板及显示面板驱动方法,栅极驱动电路包括多级级联的栅极驱动单元,第N级栅极驱动单元包括:上拉模块,电连接于第二Q点,N为正整数;上拉控制模块,包括第一晶体管和第二晶体管,第一晶体管的栅极和第二晶体管的栅极均电连接于第N‑1级栅极驱动单元的栅极信号端,第一晶体管的源极电连接于高电压端或第N‑1级栅极驱动单元的栅极信号端,第一晶体管的漏极电连接于第二晶体管的源极;第二晶体管的栅极电连接于述第一晶体管的栅极,第二晶体管的漏极电连接于该第N级栅极驱动单元的第二Q点,第一晶体管的漏极以及第二晶体管的源极均电连接于第一Q点;其中,第一Q点的电位和第二Q点的电位相一致。

技术研发人员:刘昊天

受保护的技术使用者:广州华星光电半导体显示技术有限公司

技术研发日:

技术公布日:2024/10/21

- 还没有人留言评论。精彩留言会获得点赞!