一种减小光刻沟槽线宽极限的方法与流程

本发明属于半导体制备领域,特别涉及一种减小光刻沟槽线宽极限的方法。

背景技术:

1、半导体领域的发展离不开光刻工艺。目前光刻机已从436nm g线光刻、365nm i线光刻、248nm深紫外光刻(duv)、193nm arf准分子光刻发展到13.5nm极紫外光刻(euv)以及浸式光刻和电子束刻蚀(ebl)等。通常随着光刻机分辨率的提升,增加了刻蚀难度,进而提升刻蚀成本。现有处理方式如图1a至图1d所示,并不能有效减小沟槽宽度,不能克服技术困难。在控制成本的同时,即使用现成的较大线宽极限的光刻机得到更小线宽沟槽是目前半导体领域人员亟待解决的难题之一。

技术实现思路

1、针对现有的光刻机线宽的限制且采用高精度光刻机获得沟槽造成成本增加的问题,本发明提供一种减小波导线宽极限的方法,通过沉积隔离层克服了所使用的光刻机线宽限制的问题,获得更小的沟槽线宽。

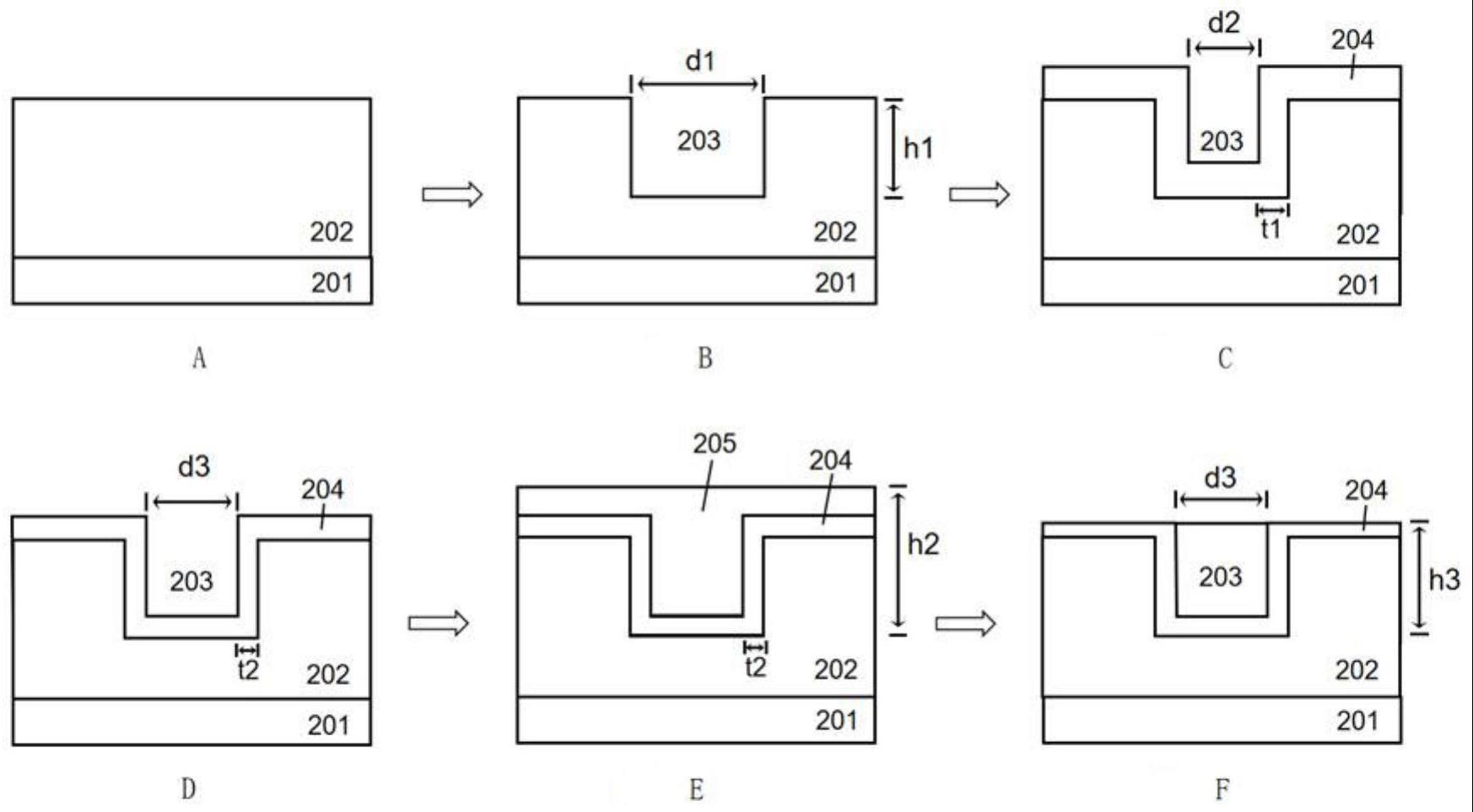

2、本发明采用技术方案如下:一种减小光刻沟槽线宽极限的方法,包括:

3、步骤1,在半导体衬底表面形成下包层;

4、步骤2,在所述下包层表面涂覆光刻胶,采用光刻工艺在光刻胶表面形成光刻胶图形,所述光刻工艺为g线、i线、duv、euv或ebl光刻工艺;

5、步骤3,利用湿法刻蚀或干法刻蚀,刻蚀不包覆光刻胶的下包层上表面,得到沟槽;

6、步骤4,在步骤1得到的下包层表面和所述沟槽表面沉积隔离层,得到更小线宽的沟槽。

7、本发明通过在沟槽中沉积隔离层,通过隔离层减小沟槽宽度,从而得到更小线宽的沟槽结构,达到克服光刻极限值的目的,即在使用更低分辨率的光刻机的情况下,就可以实现更高分辨率的光刻机才能达到的光刻效果。

8、进一步地,所述隔离层的厚度为1-300纳米,所述隔离层可为单层或多层结构,每层为二氧化硅、氮化硅、氮氧化硅、单晶硅或多晶硅中的一种。隔离层(spacer),也可称为间隔层或垫片。隔离层不仅可以减小光刻线宽极限,在集成光学应用上,可通过设置隔离层和下包层的折射率梯度,起到降低折射率对比度的作用,从而降低光信号的散射损耗;在集成电路应用上,隔离层还可以作为钝化层防止不必要的元素扩散,或作为介电层减小电介质材料的设备尺寸。隔离层可根据具体的沉积材料种类和厚度进行单次或多次沉积。例如,当隔离层为一种材料且厚度较大时,为得到保形沉积或较好的沉积结果,可进行分步多次沉积;当隔离层为多种材料也需进行多次沉积;当其中一次沉积未达到目标厚度的情况下,也可进行再次沉积或多次沉积进行厚度调整,直至达到目标厚度。

9、进一步地,沉积隔离层的方式包括低压化学气相沉积高温氧化法(lpcvd hto)、低压化学气相沉积低温氧化法(lpcvd lto)、基于四乙氧基硅烷源的低压化学气相沉积法(lpcvd teos)、基于四乙氧基硅烷源的等离子增强化学气相沉积法(pecvd teos)、低压化学气相沉积(lpcvd)氮化硅或低压化学气相沉积(lpcvd)氮氧化硅、硅气相外延生长和原子层沉积中的一种,沉积温度为100-1300℃,沉积速度控制在0.1纳米/分钟到1微米/分钟;

10、沉积时间可根据所需隔离层的厚度和隔离层的沉积速度来调节。隔离层可根据需要进行多次沉积。

11、进一步地,所述半导体衬底包括单晶硅、多晶硅、无定形硅、碳化硅、二氧化硅、蓝宝石或iii-v族半导体衬底中的一种,厚度为100μm~5mm;所述下包层包括二氧化硅、氮化硅、氮氧化硅、单晶硅或多晶硅中的一种,厚度为10nm~100μm。

12、进一步地,所述方法可选择性使用如下方式:通过刻蚀隔离层的厚度,以修饰隔离层的宽度。刻蚀的方法可为湿法刻蚀或干法刻蚀,其刻蚀剂可根据隔离层的材料进行选择,刻蚀时间需根据目标厚度进行调节。根据具体需求,刻蚀工艺可为一步或多步。

13、进一步地,所述方法还包括在隔离层上沉积波导芯层,获得波导结构,此时沟槽底部到波导芯层上表面的距离为h2,然后采用磨片和/或化学机械平坦化(cmp)和/或回蚀(etchback)处理,使得波导结构的厚度和表面粗糙度满足使用要求。磨片工艺和cmp的磨料、抛光速率、压力等具体工艺参数可根据所需处理的表面的材料和结构、需要去除的厚度、以及对平坦化后的表面粗糙度的要求来决定。回蚀工艺中的光刻胶选择及其涂敷,以及刻蚀和cmp等具体步骤也可根据具体的波导表面材料和结构、需要去除的厚度、以及对处理后表面的粗糙度的要求来决定。最终沟槽底部到晶圆表面的距离为h3,h3<=h2,h3也可<=h1。根据使用的不同光刻机,最终得到的沟槽宽度都可小于所用光刻机的最小线宽极限。

14、进一步地,所述波导芯层为一层或多层结构,每层结构为无机波导材料或有机波导材料,所述无机波导材料包括氮化硅、掺杂或未掺杂二氧化硅、氮氧化硅、硅、碳化硅、锗化硅中的一种,所述有机波导材料包括光刻胶、凝胶或树脂。

15、本申请还保护在隔离层上沉积波导芯层的集成光波导结构,及其在集成光学领域的应用。

16、本发明具有的有益效果:本发明通过在沟槽中沉积隔离层,从而减小光刻沟槽线宽的极限,即在使用更低分辨率的光刻机的情况下,就可以实现更高分辨率的光刻机才能达到的光刻效果。

技术特征:

1.一种减小光刻沟槽线宽极限的方法,其特征在于,包括:

2.根据权利要求1所述的减小光刻沟槽线宽极限的方法,其特征在于,所述隔离层的厚度为1-300纳米,所述隔离层可为单层或多层结构,每层为二氧化硅、氮化硅、氮氧化硅、单晶硅或多晶硅中的一种。

3.根据权利要求1所述的减小光刻沟槽线宽极限的方法,其特征在于,沉积隔离层的方式包括低压化学气相沉积高温氧化法、低压化学气相沉积低温氧化法、基于四乙氧基硅烷源的低压化学气相沉积法、基于四乙氧基硅烷源的等离子增强化学气相沉积法、低压化学气相沉积氮化硅、低压化学气相沉积氮氧化硅、硅气相外延生长和原子层沉积中的一种,沉积温度为100-1300℃,沉积速度控制在0.1纳米/分钟到1微米/分钟。

4.根据权利要求1所述的减小光刻沟槽线宽极限的方法,其特征在于,所述半导体衬底包括单晶硅、多晶硅、无定形硅、碳化硅、二氧化硅、蓝宝石或iii-v族半导体衬底中的一种,厚度为100μm~5mm;所述下包层包括二氧化硅、氮化硅、氮氧化硅、单晶硅或多晶硅中的一种,厚度为10nm~100μm。

5.根据权利要求1所述的减小光刻沟槽线宽极限的方法,其特征在于,通过刻蚀隔离层的厚度,以修饰隔离层的宽度。

6.根据权利要求1所述的减小光刻沟槽线宽极限的方法,其特征在于,在隔离层上沉积波导芯层,获得波导结构,并采用磨片和/或化学机械平坦化和/或回蚀处理。

7.根据权利要求6所述的减小光刻沟槽线宽极限的方法,其特征在于,所述波导芯层为一层或多层结构,每层结构为无机波导材料或有机波导材料,所述无机波导材料包括氮化硅、掺杂或未掺杂二氧化硅、氮氧化硅、硅、碳化硅、锗化硅中的一种,所述有机波导材料包括光刻胶、凝胶或树脂。

8.根据权利要求6或7所述的减小光刻沟槽线宽极限的方法制备得到一种集成光波导结构。

9.根据权利要求8所述的集成光波导结构在集成光学领域的应用。

技术总结

本发明为一种减小光刻沟槽线宽极限的方法,属于半导体制备领域,克服了现有的光刻机线宽的限制,可替代采用更高精度的光刻机获得沟槽的方法,采用技术方案如下:步骤1,在半导体衬底表面形成下包层;步骤2,在所述下包层表面涂覆光刻胶,采用光刻工艺在光刻胶表面形成光刻胶图形;步骤3,利用湿法刻蚀或干法刻蚀,刻蚀不包覆光刻胶的下包层得到沟槽;步骤4,在步骤1得到的下包层表面和所述沟槽表面沉积隔离层,获得更小线宽沟槽。本发明通过在沟槽中沉积隔离层,通过隔离层减小沟槽宽度,从而得到更小线宽的沟槽结构,克服了光刻线宽的限制,即在使用更低分辨率的光刻机的情况下,就可以实现更高分辨率的光刻机才能达到的光刻线宽。

技术研发人员:刘骏秋,叶志超,贾海燕

受保护的技术使用者:杭州芯傲光电有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!