制造半导体装置的方法与流程

本公开涉及制造半导体装置的方法,具体地,涉及使用光学邻近校正(opc)方法制造半导体装置的方法。

背景技术:

1、由于半导体装置的小尺寸、多功能和/或低成本特性,它们被认为是电子工业中的重要元件。半导体装置可以被分类为用于储存数据的存储器装置、用于处理数据的逻辑装置以及包括存储器元件和逻辑元件两者的混合装置。随着电子工业变得更加高度发达,对具有改善特性的半导体装置的需求增加。例如,对具有高可靠性、高性能和/或多功能的半导体装置的需求增加。为了解决这种需求,半导体装置的复杂性和/或集成密度已经增加。

技术实现思路

1、发明构思的实施例提供了一种可以以高度准确的方式执行而不违反掩模规则的光学邻近校正(opc)方法。

2、发明构思的实施例提供了一种制造具有高集成密度和高可靠性的半导体装置的方法。

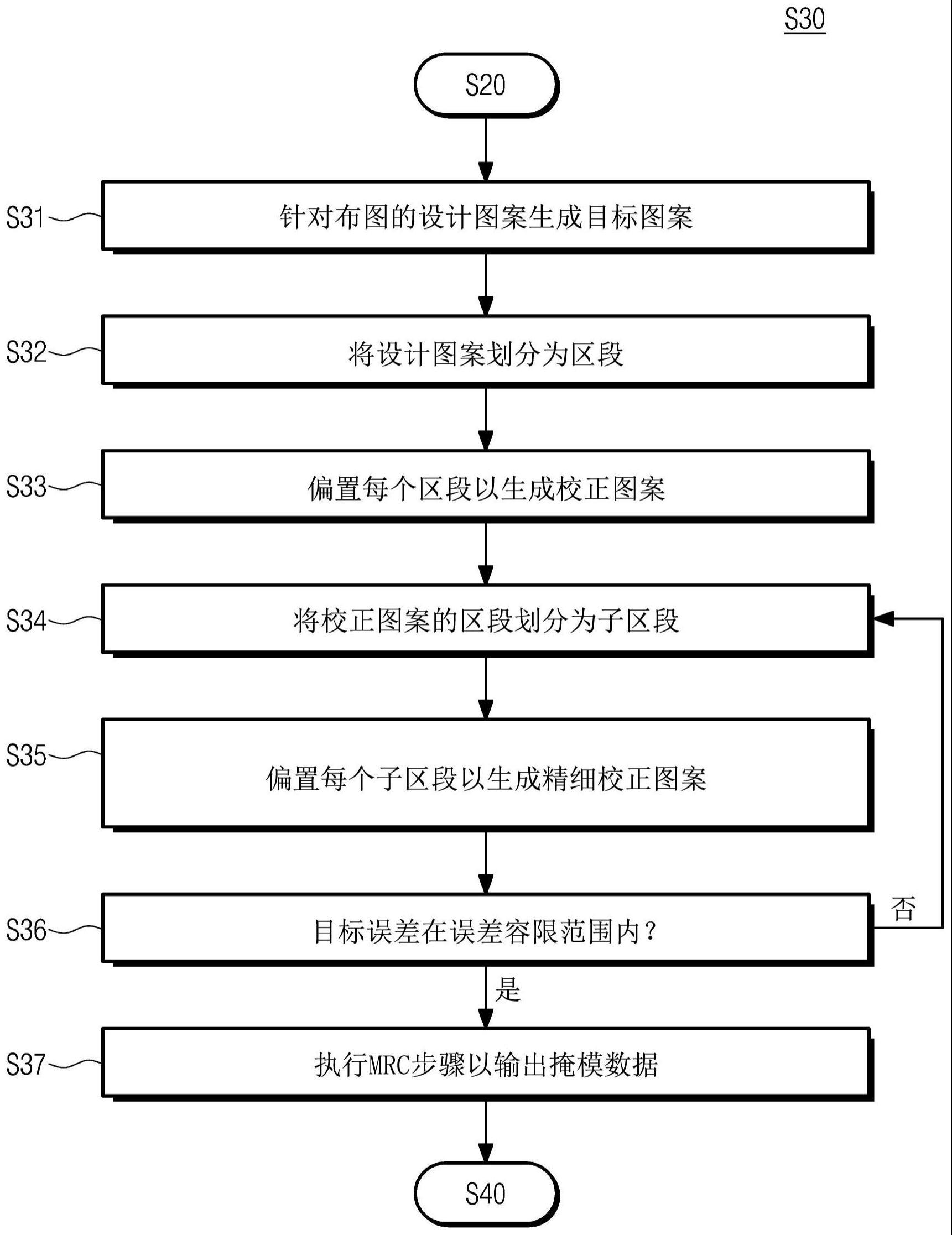

3、根据发明构思的实施例,一种制造半导体装置的方法可以包括:对布图的设计图案执行光学邻近校正(opc);以及使用基于通过opc校正的布图制造的光掩模在基底上形成光致抗蚀剂图案。执行opc可以包括:针对设计图案生成目标图案;将设计图案划分为多个区段;修改区段以生成校正图案;将区段中的第一区段划分为多个子区段;以及修改子区段以生成精细校正图案。

4、根据发明构思的实施例,一种制造半导体装置的方法可以包括:对布图的设计图案执行光学邻近校正(opc);以及使用基于通过opc校正的布图制造的光掩模在基底上形成光致抗蚀剂图案。执行opc可以包括:针对设计图案生成目标图案;将设计图案划分为多个区段;以及生成精细校正图案,使得精细校正图案的模拟轮廓符合目标图案。在opc期间,精细校正图案的区段的数量可以增加到比设计图案的区段的数量大的值。

5、根据发明构思的实施例,一种制造半导体装置的方法可以包括:对布图的设计图案执行光学邻近校正(opc);以及使用基于通过opc校正的布图制造的光掩模在基底上形成光致抗蚀剂图案。执行opc可以包括:针对设计图案生成目标图案;将设计图案划分为多个区段;修改区段中的第一区段,使得与第一区段对应的模拟轮廓与目标图案相邻;将模拟轮廓的波纹划分为多个像素;计算像素中的每个像素的光的相应的强度值;选择像素中具有强度值之间的最大差异的相邻像素;以及选择像素中具有强度值之间的最大差异的所述相邻像素之间的点作为拆解点,以将第一区段划分为第一子区段和第二子区段。

技术特征:

1.一种制造半导体装置的方法,所述方法包括:

2.根据权利要求1所述的方法,其中,执行修改区段和修改子区段的步骤,直到精细校正图案的模拟轮廓符合目标图案。

3.根据权利要求1所述的方法,其中,执行光学邻近校正还包括:

4.根据权利要求3所述的方法,其中,执行光学邻近校正还包括:将子区段中的至少一个子区段划分为更小的子区段,直到目标误差在误差容限范围内。

5.根据权利要求1所述的方法,其中,在修改子区段之前,校正图案的第一区段的长度大于设计图案的第一区段的长度。

6.根据权利要求1所述的方法,其中,将第一区段划分为所述多个子区段包括在第一区段上限定至少一个拆解点。

7.根据权利要求6所述的方法,其中,响应于确定第一区段的长度大于预定阈值长度,生成所述至少一个拆解点。

8.根据权利要求6所述的方法,其中,在校正图案的模拟轮廓具有波纹的点处生成所述至少一个拆解点。

9.根据权利要求8所述的方法,其中,生成所述至少一个拆解点包括:

10.根据权利要求1所述的方法,所述方法还包括:

11.一种制造半导体装置的方法,所述方法包括:

12.根据权利要求11所述的方法,

13.根据权利要求11所述的方法,其中,精细校正图案在精细校正图案的中心轴的第一侧上的区段的数量不同于精细校正图案在所述中心轴的相对的第二侧上的区段的数量。

14.根据权利要求11所述的方法,其中,在光学邻近校正期间,迭代地增加精细校正图案的区段的数量,直到模拟轮廓符合目标图案。

15.根据权利要求11所述的方法,其中,执行光学邻近校正还包括:

16.一种制造半导体装置的方法,所述方法包括:

17.根据权利要求16所述的方法,其中,执行光学邻近校正还包括修改第一子区段和第二子区段以生成精细校正图案。

18.根据权利要求17所述的方法,其中,重复修改第一子区段和第二子区段,直到模拟轮廓符合目标图案。

19.根据权利要求17所述的方法,其中,执行光学邻近校正还包括:

20.根据权利要求19所述的方法,其中,执行光学邻近校正还包括将第一子区段和第二子区段中的至少一个子区段划分为更小的子区段,直到目标误差在误差容限范围内。

技术总结

提供了一种制造半导体装置的方法。所述方法包括对布图的设计图案执行光学邻近校正(OPC),并且使用基于通过OPC校正的布图制造的光掩模在基底上形成光致抗蚀剂图案。执行OPC包括:针对设计图案生成目标图案;将设计图案划分为多个区段;修改区段以生成校正图案;将区段中的第一区段划分为多个子区段;以及修改子区段以生成精细校正图案。

技术研发人员:韩奎斌

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!