叠加校正方法以及曝光方法和半导体器件制造方法与流程

本发明构思涉及叠加(overlay)校正方法,更具体而言,涉及用于校正由晶片台引起的叠加的叠加校正方法,以及包括该叠加校正方法的曝光方法和半导体器件制造方法。

背景技术:

1、近来,由于半导体电路的线宽逐渐变得更精细,所以在制造期间实施具有更短波长的光源。例如,极紫外(euv)光已被用作曝光光源。由于euv光的吸收特性,反射式euv掩模通常用于euv曝光工艺中。此外,用于将euv光传输到euv掩模的照明光学器件和用于将从euv掩模反射的euv光投影到曝光目标上的投影光学器件可以包括多个反射镜。同时,随着图案变得更精细,在euv曝光工艺中已经出现了由于各种原因引起的叠加误差。

技术实现思路

1、本发明构思提供了一种有效校正由于晶片台退化引起的叠加的叠加校正方法,以及一种包括该叠加校正方法的曝光方法和半导体器件制造方法。

2、此外,本发明构思要实现的目标不限于上述目标,本领域普通技术人员可以从以下描述清楚地理解其他目标。

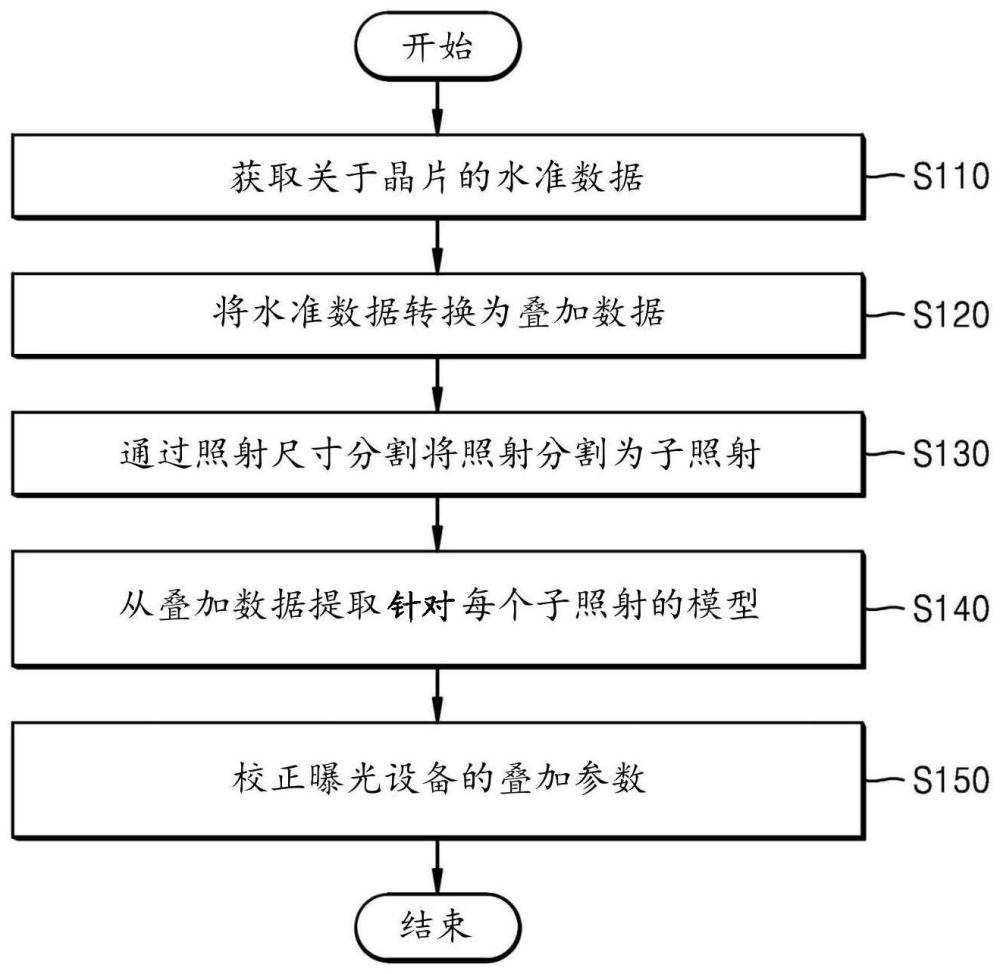

3、根据发明构思的一方面,提供了一种叠加校正方法,该方法包括:获取晶片的水准数据;将水准数据转换成叠加数据;通过照射尺寸分割将晶片的照射分割成子照射;从叠加数据提取针对每个子照射的模型;以及基于针对每个子照射的模型,校正曝光设备的叠加参数,其中叠加参数的校正被实时应用。

4、根据发明构思的另一方面,提供一种曝光方法,该方法包括:获取第一晶片的第一水准数据;将第一水准数据转换为叠加数据;通过照射尺寸分割将第一晶片的照射分割成子照射;从叠加数据提取针对每个子照射的模型;基于针对每个子照射的模型,校正曝光设备的叠加参数;以及使用基于校正后的叠加参数调整的曝光设备,对第一晶片执行曝光工艺。

5、根据发明构思的另一方面,提供了一种半导体器件制造方法,该方法包括:获取多个晶片中的至少一个晶片的水准数据;将水准数据转换成叠加数据;通过照射尺寸分割将所述至少一个晶片的照射分割成子照射;从叠加数据提取针对每个子照射的模型;基于针对每个子照射的模型,校正曝光设备的叠加参数;使用基于校正后的叠加参数调整的曝光设备,对所述至少一个晶片执行曝光工艺;图案化曝光的晶片;以及对图案化的晶片执行后续的半导体工艺,其中通过实时校正对于所述多个晶片中的每个晶片和每个子照射的叠加参数来执行曝光工艺。

技术特征:

1.一种叠加校正方法,包括:

2.根据权利要求1所述的叠加校正方法,其中,所述叠加参数的校正在对于所述晶片的曝光工艺之前执行,并且对于所述晶片的所述曝光工艺使用校正后的叠加参数。

3.根据权利要求1所述的叠加校正方法,其中

4.根据权利要求3所述的叠加校正方法,其中

5.根据权利要求1所述的叠加校正方法,其中

6.根据权利要求5所述的叠加校正方法,其中,分割成所述子照射包括将所述照射分割成3*5个子照射。

7.根据权利要求1所述的叠加校正方法,其中

8.根据权利要求1所述的叠加校正方法,其中,校正所述叠加参数实时校正用于所述曝光工艺中的针对每个晶片和每个子照射的所述叠加参数。

9.根据权利要求1所述的叠加校正方法,其中,所述水准数据按时间序列反映其上装载有所述晶片的晶片台的顶表面的状态,并且校正所述叠加参数包括校正由于所述晶片台的所述顶表面的时间序列退化引起的叠加。

10.一种曝光方法,包括:

11.根据权利要求10所述的曝光方法,其中

12.根据权利要求10所述的曝光方法,其中

13.根据权利要求10所述的曝光方法,其中

14.根据权利要求10所述的曝光方法,其中

15.根据权利要求10所述的曝光方法,其中所述曝光工艺使用远紫外光。

16.一种半导体器件制造方法,包括:

17.根据权利要求16所述的半导体器件制造方法,其中

18.根据权利要求16所述的半导体器件制造方法,其中

19.根据权利要求16所述的半导体器件制造方法,其中

20.根据权利要求16所述的半导体器件制造方法,其中,所述曝光工艺使用极紫外光,并且校正所述叠加参数包括校正由于其上装载有所述晶片的晶片台的顶表面的时间序列退化而引起的叠加。

技术总结

提供了一种用于有效校正由于晶片台退化引起的叠加的叠加校正方法,以及包括该叠加校正方法的曝光方法和半导体器件制造方法,其中该叠加校正方法包括:获取关于晶片的水准数据;将水准数据转换成叠加数据;通过照射尺寸分割将照射分割成子照射;从叠加数据提取针对每个子照射的模型;以及基于针对每个子照射的模型来校正曝光设备的叠加参数,其中以前馈方法将叠加参数的校正实时应用于晶片的曝光工艺。

技术研发人员:郑羽容,金岛辉,金俊贤,李汀镇,李承润,黄灿

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/5/16

- 还没有人留言评论。精彩留言会获得点赞!