光学多裸片互连桥(OMIB)的制作方法

本公开的实施方式总体上涉及用在互连半导体裸片中的设备和方法,尤其涉及使用集成电路和/或外部芯粒(chiplet)进行光学互连的设备和方法。

背景技术:

1、本部分中讨论的主题不应仅仅因为在本部分中提及而被认为是现有技术。类似地,本部分中提到的或者与作为背景提供的主题相关联的问题不应该被认为是先前在现有技术中已经被承认。本部分中的主题仅仅表示不同的方法,这些方法本身也可以对应于所要求保护的技术的实施方式。

2、具有处理器的集成电路(ic),尤其是用于执行人工智能和机器学习功能的集成电路,在一个或更多个处理器ic和一个或更多个存储器ic之间移动大量数据。芯粒可以有助于处理器裸片、存储器裸片和其它电路的互连,以增加带宽并减少过程中的延迟和功耗。

技术实现思路

1、处理ai工作负载通常使用专用硬件。典型的硬件用电互连桥接两个芯片。电互连消耗高功率,具有引脚数限制,并且只能将数据带到芯片的边缘。当存储器位于芯片的中心区域时,每次处理器从芯片外部向芯片的边缘发送请求来访问存储器时,信号都需要额外的传输距离。这是非常低效的,并且使得ai计算硬件很难跟上ai应用所要求的需求。

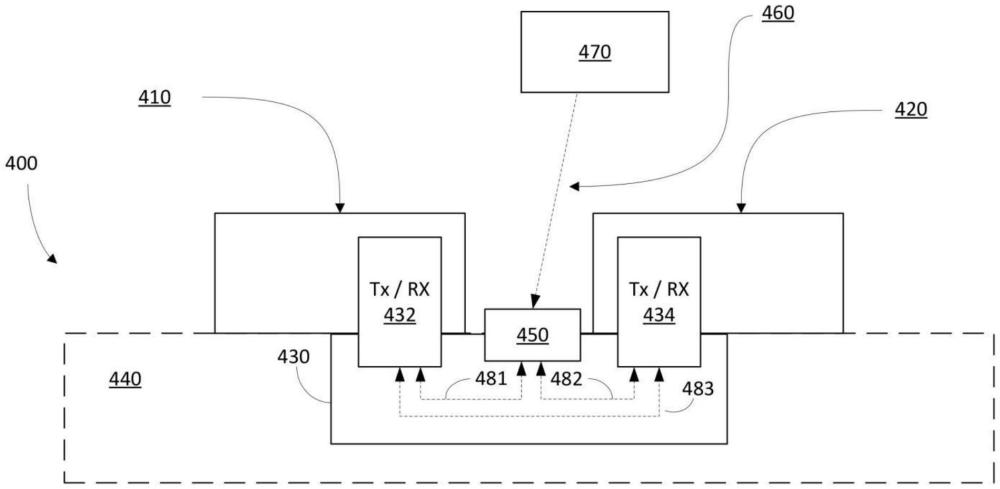

2、在第一方面,实施方式提供了一种封装,该封装包括桥接元件、第一单向光子路径和第二单向光子路径。桥接元件包括第一互连区域和第二互连区域,两者都被配置为与一个或更多个裸片电连接。单向光子路径在两个互连区域之间以相反的方向耦接。第三单向光子路径和第四单向光子路径可以在第一互连区域和光学接口(oi)之间双向耦接。光子收发器的第一部分可以与第一互连区域耦接,以通过第一单向光子路径发送第一光学信号,并且通过第二单向光子路径接收第二光学信号。它还可以被配置为通过第三单向光子路径发送第三光学信号,并且通过第四单向光子路径接收第四光学信号。光子收发器的第一部分可以位于光子集成电路(pic)中,光子收发器的第二部分可以位于电子集成电路(eic)中。第一部分和第二部分可以通过长度小于2mm的电互连耦接。调制器可以是用锗、硅、锗合金、硅合金、基于磷化铟(inp)的iii-v材料或基于砷化镓(gaas)的iii-v材料制造的电吸收调制器。eic可以包括围绕中心区域的两个或更多个计算元件。第二部分靠近其中一个计算元件。

3、通过参考说明书的剩余部分和所附的附图,可以进一步理解本文公开的特定实施方式的性质和优点。

技术特征:

1.一种封装,包括:

2.根据权利要求1所述的封装,还包括:

3.根据权利要求1所述的封装,还包括:

4.根据权利要求3所述的封装,其中,所述光子收发器的所述第一部分包括调制器和/或光电探测器。

5.根据权利要求3所述的封装,其中:

6.根据权利要求3所述的封装,其中:

7.根据权利要求6所述的封装,其中:

8.根据权利要求7所述的封装,其中:

9.根据权利要求7所述的封装,其中:

10.根据权利要求9所述的封装,其中:

11.根据权利要求9所述的封装,其中:

12.根据权利要求9所述的封装,其中:

13.根据权利要求1所述的封装,还包括:

14.根据权利要求12所述的封装,其中:

15.根据权利要求12所述的封装,其中:

技术总结

一种封装包括桥接元件(OMIB)、第一光子路径和第二光子路径,从形成双向光子路径。OMIB具有第一互连区域和第二互连区域以与一个或更多个裸片连接。第三单向光子路径和第四单向光子路径可以耦接在第一互连区域和光学接口(OI)之间。光子收发器具有在OMIB中的第一部分和其中一个裸片的第二部分。第一部分和第二部分可以通过长度小于2mm的电互连耦接。该裸片包括靠近第二部分的围绕中心区域的计算元件。OMIB可以包括由锗、硅、锗合金、硅合金、基于磷化铟(InP)的III‑V材料或基于砷化镓(GaAs)的III‑V材料制成的电吸收调制器。OMIB可以包括调制器的温度补偿。

技术研发人员:菲利普·温特伯顿,大卫·拉佐夫斯基,安库尔·阿加瓦尔,马蒂纳斯·博斯,苏巴尔·萨尼

受保护的技术使用者:天体人工智能公司

技术研发日:

技术公布日:2024/11/7

- 还没有人留言评论。精彩留言会获得点赞!