NorFlash中多晶硅栅的制造方法、器件和存储介质与流程

nor flash中多晶硅栅的制造方法、器件和存储介质

技术领域

1.本发明涉及集成电路制造领域,尤其涉及一种nor flash中多晶硅栅的制造方法、器件和计算机可读存储介质。

背景技术:

2.nor flash是两种主要的非易失闪存之一,55nm nor flash器件的栅极通常采用杂质硼(b)注入多晶硅的方式掺杂。由于硼在多晶硅中的扩散不均匀,靠近栅氧化层处的浓度分布较低,形成多晶硅耗尽,cpk长期fail,器件性能退化。因此需要一种制造工艺,既能够改善多晶硅耗尽现象提高器件性能,又能够简化制造工艺。

技术实现要素:

3.在发明内容部分中引入了一系列简化形式的概念,该简化形式的概念均为本领域现有技术简化,这将在具体实施方式部分中进一步详细说明。本发明的发明内容部分并不意味着要试图限定出所要求保护的技术方案的关键特征和必要技术特征,更不意味着试图确定所要求保护的技术方案的保护范围。

4.为解决上述技术问题,本发明提供一种nor flash中多晶硅栅的制造方法,包括以下步骤:

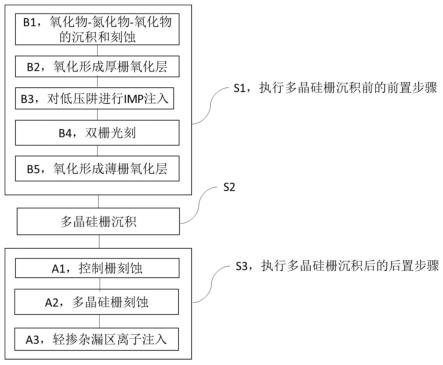

5.s1,执行多晶硅栅沉积前的前置步骤;s2,多晶硅栅沉积,所述步骤s2中,控制多晶硅的沉积厚度直接至多晶硅栅的目标厚度;s3,执行多晶硅栅沉积后的后置步骤。

6.优选地,所述步骤s1中,所述前置步骤包括:b1,氧化物-氮化物-氧化物的沉积和刻蚀;b2,氧化形成厚栅氧化层;b3,对低压阱进行imp注入;b4,双栅光刻;b5,氧化形成薄栅氧化层。

7.优选地,所述步骤s3中,所述后置步骤包括:a1,控制栅刻蚀;a2,多晶硅栅刻蚀;a3,轻掺杂漏区离子注入。

8.优选地,在所述步骤s2中,使外围区的多晶硅栅厚度与元胞区的多晶硅栅的厚度一致。

9.优选地,所述步骤a3,轻掺杂漏区离子注入的为硼离子。

10.优选地,所述步骤a3,轻掺杂漏区离子注入的参数可调。

11.本发明还提供一种nor flash器件,其由前述发明内容中的nor flash中多晶硅栅的制造方法制造。

12.本发明还一种计算机可读存储介质,其上存储有计算机程序,所述计算机程序被处理器执行时实现如前述发明内容中所述的nor flash中多晶硅栅的制造方法。

13.与现有技术相比本发明的技术方案既能够改善nor flash器件制造过程中多晶硅耗尽现象提高器件性能,又能够简化制造工艺。

附图说明

14.本发明附图旨在示出根据本发明的特定示例性实施例中所使用的方法、结构和/或材料的一般特性,对说明书中的描述进行补充。然而,本发明附图是未按比例绘制的示意图,因而可能未能够准确反映任何所给出的实施例的精确结构或性能特点,本发明附图不应当被解释为限定或限制由根据本发明的示例性实施例所涵盖的数值或属性的范围。下面结合附图与具体实施方式对本发明作进一步详细的说明:

15.图1为现有技术的器件形貌示意图;

16.图2为本发明实施例1的制造方法流程示意图;

17.图3为本发明实施例1的器件形貌示意图。

具体实施方式

18.以下通过特定的具体实施例说明本发明的实施方式,本领域技术人员可由本说明书所公开的内容充分地了解本发明的其他优点与技术效果。本发明还可以通过不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点加以应用,在没有背离发明总的设计思路下进行各种修饰或改变。需说明的是,在不冲突的情况下,以下实施例及实施例中的特征可以相互组合。本发明下述示例性实施例可以多种不同的形式来实施,并且不应当被解释为只限于这里所阐述的具体实施例。应当理解的是,提供这些实施例是为了使得本发明的公开彻底且完整,并且将这些示例性具体实施例的技术方案充分传达给本领域技术人员。

19.实施例1

20.现有技术在nor flash制造过程中,在多晶硅栅沉积前的前置步骤示例性如下:

21.b1,氧化物-氮化物-氧化物(ono)沉积和刻蚀;b2,氧化形成厚栅氧化层;b3,对低压阱(lv well)进行imp注入;b4,双栅光刻;b5,氧化形成薄栅氧化层。

22.然后进行多晶硅栅沉积,如图1所示,现有技术中多晶硅栅的沉积厚度通常都大于目标厚度thk,在元胞区(cell)的多晶硅栅的沉积厚度大于目标厚度thk,在后续步骤中通过对元胞区进行回刻,使控制栅达到目标厚度thk。由于在外围区(peri)的多晶硅厚度依旧很厚,因此导致了硼在多晶硅中的扩散不均匀,靠近栅氧化层处的浓度分布较低,形成多晶硅耗尽。

23.考虑到低压pmos器件的阈值电压(vt)与多晶硅厚度存在一定相关性,采用了如下改进的制造方法,如图2。

24.在多晶硅栅沉积前的前置步骤与现有技术相同,示例性地如前述的b1至b5。在多晶硅栅沉积步骤中,直接控制沉积厚度至目标厚度thk,使外围区(peri)的多晶硅栅厚度与元胞区(cell)的多晶硅栅的厚度一致,如图3。后续步骤中无需对元胞区进行回刻,直接进行控制栅刻蚀(cg etch loop)后续步骤示例性如下:

25.a1,控制栅刻蚀(cg etch loop);a2,多晶硅栅刻蚀(gpl etch loop);a3,轻掺杂漏区(ldd)离子注入(ldd loop)。

26.示例性的步骤a3,轻掺杂漏区(ldd)离子注入的为硼离子。

27.此外通过调整注入参数,使外围器件meet target,同时达到改善pmos波动性的目的。

28.实施例2

29.本实施例提供一种nor flash器件,其由实施例1中所述的nor flash中多晶硅栅的制造方法制造。

30.实施例3

31.本实施例提供一种计算机可读存储介质,其上存储有计算机程序,所述计算机程序被处理器执行时实现如实施例1所述的nor flash中多晶硅栅的制造方法。

32.除非另有定义,否则这里所使用的全部术语(包括技术术语和科学术语)都具有与本发明所属领域的普通技术人员通常理解的意思相同的意思。还将理解的是,除非这里明确定义,否则诸如在通用字典中定义的术语这类术语应当被解释为具有与它们在相关领域语境中的意思相一致的意思,而不以理想的或过于正式的含义加以解释。

33.以上通过具体实施方式和实施例对本发明进行了详细的说明,但这些并非构成对本发明的限制。在不脱离本发明原理的情况下,本领域的技术人员还可做出许多变形和改进,这些也应视为本发明的保护范围。

技术特征:

1.一种nor flash中多晶硅栅的制造方法,其特征在于,包括以下步骤:s1,执行多晶硅栅沉积前的前置步骤;s2,多晶硅栅沉积,所述步骤s2中,控制多晶硅的沉积厚度直接至多晶硅栅的目标厚度;s3,执行多晶硅栅沉积后的后置步骤。2.如权利要求1所述的nor flash中多晶硅栅的制造方法,其特征在于,所述步骤s1中,所述前置步骤包括:b1,氧化物-氮化物-氧化物的沉积和刻蚀;b2,氧化形成厚栅氧化层;b3,对低压阱进行imp注入;b4,双栅光刻;b5,氧化形成薄栅氧化层。3.如权利要求1所述的nor flash中多晶硅栅的制造方法,其特征在于,所述步骤s3中,所述后置步骤包括:a1,控制栅刻蚀;a2,多晶硅栅刻蚀;a3,轻掺杂漏区离子注入。4.如权利要求1所述的nor flash中多晶硅栅的制造方法,其特征在于:在所述步骤s2中,使外围区的多晶硅栅厚度与元胞区的多晶硅栅的厚度一致。5.如权利要求3所述的nor flash中多晶硅栅的制造方法,其特征在于:所述步骤a3,轻掺杂漏区离子注入的为硼离子。6.如权利要求3所述的nor flash中多晶硅栅的制造方法,其特征在于:所述步骤a3,轻掺杂漏区离子注入的参数可调。7.一种nor flash器件,其特征在于:其由权利要求1至5任一项所述的nor flash中多晶硅栅的制造方法制造。8.一种计算机可读存储介质,其上存储有计算机程序,其特征在于,所述计算机程序被处理器执行时实现如权利要求1至6任一项所述的nor flash中多晶硅栅的制造方法。

技术总结

本发明公开了一种Nor Flash中多晶硅栅的制造方法,包括以下步骤:S1,执行多晶硅栅沉积前的前置步骤;S2,多晶硅栅沉积,所述步骤S2中,控制多晶硅的沉积厚度直接至多晶硅栅的目标厚度;S3,执行多晶硅栅沉积后的后置步骤。与现有技术相比本发明的技术方案既能够改善Nor Flash器件制造过程中多晶硅耗尽现象提高器件性能,又能够简化制造工艺。又能够简化制造工艺。又能够简化制造工艺。

技术研发人员:衣云鸽 焦佳晖 王虎 郭霞文

受保护的技术使用者:华虹半导体(无锡)有限公司

技术研发日:2022.11.23

技术公布日:2023/3/14

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1