半导体层叠体、半导体元件及半导体元件的制造方法与流程

本发明涉及半导体层叠体、半导体元件及半导体元件的制造方法。

背景技术:

1、作为可实现高耐压、低损失及高耐热的新一代开关元件,使用带隙(band gap)大的氧化镓(ga2o3)的半导体元件受到关注,其被期待适用于逆变器(inverter)等电力用半导体装置。

2、特别是刚玉(corundum)型α-ga2o3金属氧化物能够进行使用了相对廉价的蓝宝石基体的外延生长(epitaxial growth),进一步能够适用喷雾cvd(化学气相沉积)法(专利文献1)或hvpe(hydride vapor phase epitaxy,氢化物气相沉积)法(专利文献2)这样的常压工艺,因此期待能够以低于既存的电力用半导体元件的成本进行制造。

3、现有技术文献

4、专利文献

5、专利文献1:日本特开2013-28480号公报

6、专利文献2:日本特开2019-34882号公报

7、专利文献3:日本特开2018-002544号公报

技术实现思路

1、本发明要解决的技术问题

2、另一方面,在如上所述的异质外延生长中,存在由于基体与外延层之间的晶格失配或热膨胀系数不同而产生的应力,导致产生位错等结晶缺陷、翘曲或裂纹这样的问题。特别是对大面积的基体进行造膜时,这些问题变得更加显著,导致难以进行生产。

3、在专利文献3中,例示出了使用在衬底基板上形成有两层以上氧化物层的衬底基板,形成在300μm见方以上的区域内不含裂纹的膜厚为3μm以上的具有刚玉结构的inalgao类半导体膜。然而,通过专利文献3所示的实例能够抑制裂纹的情况实际上仅限于直径小于4英寸(约10厘米)的小口径基板,在使用实用尺寸(直径为4英寸以上)的基板时效果则不充分。此外,即使在小口径基板中,也无法抑制基板的翘曲。

4、本发明是为了解决上述问题而实施的,其目的在于提供即使通过异质外延生长而形成时,也具有结晶缺陷、翘曲及裂纹被抑制的高品质的刚玉型结晶性金属氧化物半导体膜的半导体层叠体及高性能的半导体元件。

5、解决技术问题的技术手段

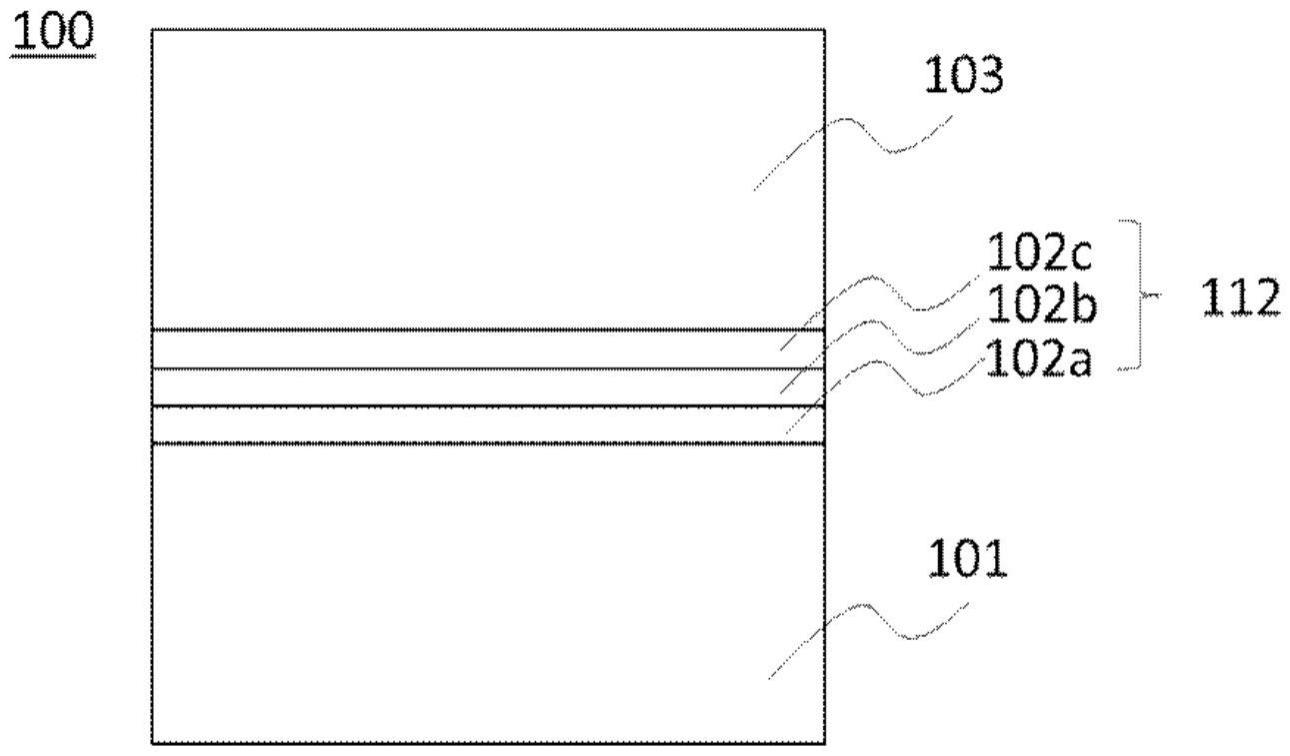

6、本发明是为了实现上述目的而实施的,提供一种半导体层叠体,其至少包括基体、缓冲层及至少包含一种金属元素的具有刚玉结构的结晶性金属氧化物半导体膜,所述半导体层叠体在所述基体的主表面上直接或隔着其他层具有所述缓冲层、在所述缓冲层上具有所述结晶性金属氧化物半导体膜,所述半导体层叠体中,所述缓冲层为组成各自不同的多层缓冲膜的层叠结构体,所述多层缓冲膜中至少有两层缓冲膜的膜厚为200nm以上650nm以下。

7、此外,本发明提供一种半导体层叠体,其至少包括基体、缓冲层及至少包含一种金属元素的具有刚玉结构的结晶性金属氧化物半导体膜,所述半导体层叠体在所述基体的主表面上直接或隔着其他层具有所述缓冲层、在所述缓冲层上具有所述结晶性金属氧化物半导体膜,所述半导体层叠体中,所述缓冲层为组成各自不同的多层缓冲膜的层叠结构体,所述多层缓冲膜的膜厚全部为200nm以上650nm以下。

8、由于通过具有这样的缓冲层,能够有效缓和基体与结晶性金属氧化物半导体膜的晶格失配所引起的应力,因此可得到具有减少了结晶缺陷的混入、进一步抑制了裂纹与翘曲的高品质的结晶性金属氧化物半导体膜的半导体层叠体。

9、此时,优选所述缓冲膜包含所述结晶性金属氧化物半导体膜所含的金属元素中所含最多的主成分金属元素。

10、进一步,优选所述缓冲层为以随着从所述缓冲层的所述基体侧朝向所述结晶性金属氧化物半导体膜侧,所述结晶性金属氧化物半导体膜的所述主成分金属元素的组成比变大的方式层叠所述多层缓冲膜而成的层叠结构体。

11、由此,由于能够进一步提高缓冲层的应力缓和效果,因此缓冲层上的结晶性金属氧化物半导体膜的品质进一步变高。

12、此时,优选所述缓冲膜包含所述缓冲层的衬底所含的金属元素中所含最多的主成分金属元素。

13、进一步,优选所述缓冲层为以随着从所述缓冲层的所述基体侧朝向所述结晶性金属氧化物半导体膜侧,所述缓冲层的衬底的所述主成分金属元素的组成比变小的方式层叠所述多层缓冲膜而成的层叠结构体。

14、由此,由于能够进一步提高缓冲层的应力缓和效果,因此缓冲层上的结晶性金属氧化物半导体膜的品质进一步变高。

15、此时,优选所述缓冲层的衬底为所述基体,所述基体的所述主成分金属元素为铝。

16、从品质及成本的角度出发,以铝作为主成分金属元素的例如蓝宝石晶圆这样的晶圆能够适宜地用作基体。

17、此时,优选所述结晶性金属氧化物半导体膜的所述主成分金属元素为镓。

18、镓氧化膜的带隙大,能够适宜地用作本发明的结晶性金属氧化物半导体膜。

19、此时,优选所述结晶性金属氧化物半导体膜的膜厚为1μm以上。

20、由此,结晶性金属氧化物半导体膜的品质变得更高。

21、此时,优选所述基体的主表面的面积为10cm2以上。

22、由此,结晶性金属氧化物半导体膜的品质进一步变高。此外,器件设计的自由度变高。

23、此时,优选提供一种半导体元件,其至少具备上文中记载的半导体层叠体中的所述缓冲层与所述结晶性金属氧化物半导体膜。

24、由此,成为电特性优异且高性能的半导体元件。

25、此外,本发明提供一种半导体元件的制造方法,其为至少具有结晶性金属氧化物半导体膜与电极的半导体元件的制造方法,其具有:在基体的主表面上,形成包括两层以上具有各自不同的组成且同时厚度为200nm以上650nm以下的缓冲膜的多层缓冲膜作为缓冲层的工序;在所述缓冲层上形成具有刚玉结构的结晶性金属氧化物半导体膜的工序;及至少在所述结晶性金属氧化物半导体膜上形成电极的工序。

26、此外,本发明进一步提供一种半导体元件的制造方法,其为至少具有结晶性金属氧化物半导体膜与电极的半导体元件的制造方法,其具有:在基体的主表面上,形成多层具有各自不同的组成且同时厚度为200nm以上650nm以下的缓冲膜作为缓冲层的工序;在所述缓冲层上形成具有刚玉结构的结晶性金属氧化物半导体膜的工序;及至少在所述结晶性金属氧化物半导体膜上形成电极的工序。

27、由于通过形成这样的缓冲层,能够有效缓和基体与结晶性金属氧化物半导体膜的晶格失配所引起的应力,因此可得到使用减少了结晶缺陷的混入、进一步抑制了裂纹与翘曲的高品质的结晶性金属氧化物半导体膜的高性能的半导体元件。

28、发明效果

29、如上所述,根据本发明,能够提供即使通过异质外延生长而形成时,也具有结晶缺陷、翘曲及裂纹被抑制的高品质的刚玉型结晶性金属氧化物半导体膜的半导体层叠体、半导体元件及半导体元件的制造方法。此外,通过使用具有本发明的结晶性金属氧化物半导体膜的半导体层叠体,能够制造高性能的半导体元件。

技术特征:

1.一种半导体层叠体,其至少包括基体、缓冲层及至少包含一种金属元素的具有刚玉结构的结晶性金属氧化物半导体膜,

2.一种半导体层叠体,其至少包括基体、缓冲层及至少包含一种金属元素的具有刚玉结构的结晶性金属氧化物半导体膜,

3.根据权利要求1或2所述的半导体层叠体,其特征在于,

4.根据权利要求3所述的半导体层叠体,其特征在于,

5.根据权利要求3或4中任一项所述的半导体层叠体,其特征在于,

6.根据权利要求5所述的半导体层叠体,其特征在于,

7.根据权利要求5或6中任一项所述的半导体层叠体,其特征在于,

8.根据权利要求3~7中任一项所述的半导体层叠体,其特征在于,

9.根据权利要求1~8中任一项所述的半导体层叠体,其特征在于,

10.根据权利要求1~9中任一项所述的半导体层叠体,其特征在于,

11.一种半导体元件,其特征在于,

12.一种半导体元件的制造方法,其为至少具有结晶性金属氧化物半导体膜与电极的半导体元件的制造方法,其特征在于,具有:

13.一种半导体元件的制造方法,其为至少具有结晶性金属氧化物半导体膜与电极的半导体元件的制造方法,其特征在于,具有:

技术总结

本发明为一种半导体层叠体,其至少包括基体、缓冲层及至少包含一种金属元素的具有刚玉结构的结晶性金属氧化物半导体膜,所述半导体层叠体在所述基体的主表面上直接或隔着其他层具有所述缓冲层、在所述缓冲层上具有所述结晶性金属氧化物半导体膜,所述半导体层叠体的特征在于,所述缓冲层为组成各自不同的多层缓冲膜的层叠结构体,所述多层缓冲膜中至少有两层缓冲膜的膜厚为200nm以上650nm以下。由此,可提供即使通过异质外延生长而形成时,也具有结晶缺陷、翘曲及裂纹被抑制的高品质的刚玉型结晶性金属氧化物半导体膜的半导体层叠体。

技术研发人员:桥上洋

受保护的技术使用者:信越化学工业株式会社

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!