用于制备约瑟夫森结的掩膜结构及相关方法与流程

本说明书中实施方式涉及量子芯片制备领域,特别是涉及一种用于制备约瑟夫森结的掩膜结构及相关方法。

背景技术:

1、约瑟夫森结可以用于构建超导量子比特。通过在超导回路中嵌入约瑟夫森结,可以实现超导量子比特。约瑟夫森结通常包括两个超导电极和介于其中间的非超导绝缘层。

2、目前,通常利用掩膜结构,通过两次电子束斜蒸发的方式进行超导材料沉积,以制备约瑟夫森结。然而,制备得到的约瑟夫森结存在线宽不准确的问题。

技术实现思路

1、有鉴于此,本说明书中多个实施方式致力于提供一种用于制备约瑟夫森结的掩膜结构及相关方法,以在一定程度上提升利用所述掩膜结构制备出的约瑟夫森结线宽的准确性。

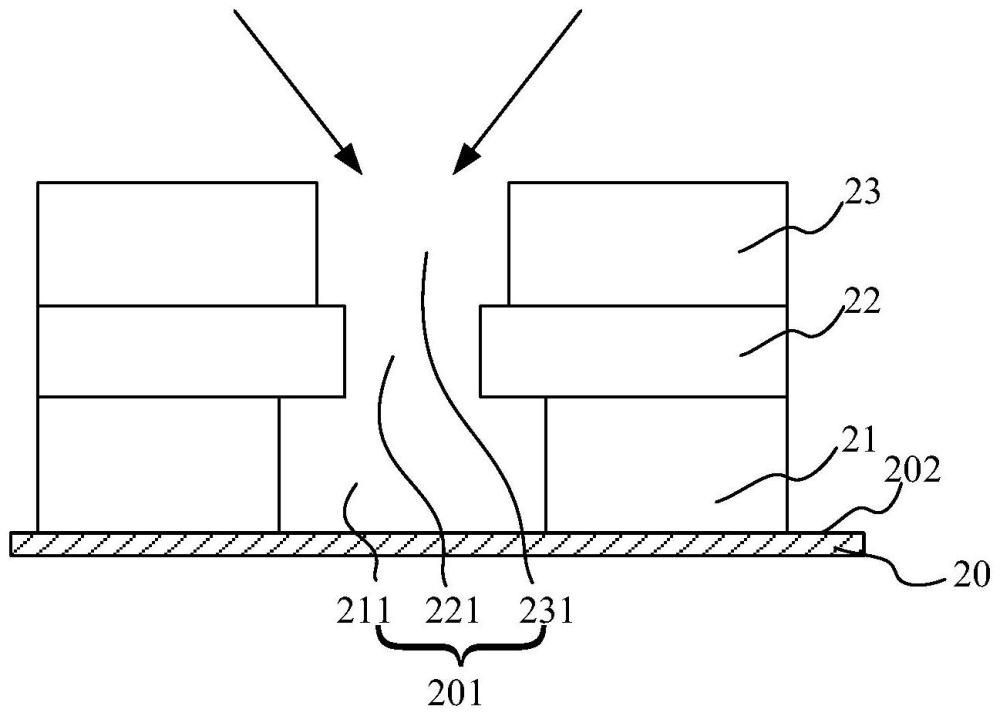

2、本说明书的一个实施方式提供一种用于制备约瑟夫森结的掩膜结构,所述掩膜结构包括层叠设置的第一掩膜层、第二掩膜层和第三掩膜层;所述第一掩膜层用于设置在基材的基材表面上;所述第二掩膜层位于所述第一掩膜层与所述第三掩膜层之间;所述掩膜结构具有贯通的窗口;所述窗口用于在所述基材表面制备约瑟夫森结;所述窗口包括位于所述第一掩膜层的第一开口,位于所述第二掩膜层的第二开口和位于所述第三掩膜层的第三开口;其中,所述第二开口在所述基材表面的垂直投影,位于所述第一开口和所述第三开口在所述基材表面的垂直投影内。

3、本说明书的一个实施方式提供一种约瑟夫森结的制备方法,所述方法包括:将上述实施方式中所述的掩膜结构设置在基材上;其中,所述掩膜结构的窗口与所述基材用于制造约瑟夫森结的制备区域相对应;利用超导材料向所述制备区域进行斜蒸发镀膜工艺,以在所述制备区域形成第一超导层;其中,所述第三掩膜层止挡至少部分向着形成所述第二开口的开口侧壁运动的超导材料。

4、本说明书的一个实施方式提供一种避免在斜蒸发制造约瑟夫森结时掩膜的沉积窗口减小而导致约瑟夫森结线宽波动的方法,所述掩膜的沉积窗口具有第一开口和第二开口,且所述第一开口和第二开口共同构成底切结构,其特征在于,所述方法包括:于所述掩膜表面形成阻挡层,所述阻挡层具有第三开口,所述第三开口与第二开口共同构成顶切结构,所述阻挡层被构造为阻止蒸发材料于斜蒸发过程中沉积于第二开口侧壁内从而避免第二开口的宽度减小;以及通过第一开口、第二开口和第三开口进行斜蒸发以制造约瑟夫森结。

5、本说明书提供的掩膜结构,通过层叠设置具有第一开口的第一掩膜层、具有第二开口的第二掩膜层和具有第三开口的第三掩膜层,且第二开口在所述基材表面的垂直投影,位于第一开口和第三开口在所述基材表面的垂直投影内,使得在进行斜蒸发镀膜以制备约瑟夫森结时,至少部分向着形成所述第二开口的开口侧壁运动的超导材料被第三掩膜层阻挡,从而使第二开口的宽度不会因超导材料沉积于开口侧壁而减小,一定程度上提升了制备出的约瑟夫森结线宽的准确性。

技术特征:

1.一种用于制备约瑟夫森结的掩膜结构,其特征在于,所述掩膜结构包括层叠设置的第一掩膜层、第二掩膜层和第三掩膜层;所述第一掩膜层用于设置在基材的基材表面上;所述第二掩膜层位于所述第一掩膜层与所述第三掩膜层之间;

2.根据权利要求1所述的掩膜结构,其特征在于,所述掩膜结构为多层硬掩膜结构;其中,所述第一掩膜层和所述第三掩膜层为硬掩膜层;所述第二掩膜层为截止层。

3.根据权利要求2所述的掩膜结构,其特征在于,所述第一掩膜层和所述第三掩膜层的材质为硅;所述第二掩膜层的材质为氧化硅、碳化硅或氮化硅。

4.根据权利要求1所述的掩膜结构,其特征在于,所述掩膜结构为多层光刻胶结构;其中,所述第一掩膜层和所述第三掩膜层的材质为光刻胶mma;所述第二掩膜层的材质为光刻胶pmma。

5.根据权利要求1所述的掩膜结构,其特征在于,所述第三掩膜层的厚度与所述第三开口的开口侧壁间的距离满足:h=d*tanθ;其中,h表示所述第三掩膜层的厚度;d表示所述第三开口的开口侧壁间的距离;θ表示使用所述掩膜结构制备约瑟夫森结的预设斜蒸发镀膜角度。

6.一种约瑟夫森结的制备方法,其特征在于,所述方法包括:

7.根据权利要求6所述的方法,其特征在于,利用超导材料向所述制备区域进行斜蒸发镀膜工艺,以在所述制备区域形成第一超导层的步骤中,至少部分超导材料沉积于所述第三掩膜层背向所述第二掩膜层的表面。

8.根据权利要求6所述的方法,其特征在于,利用超导材料向所述制备区域进行斜蒸发镀膜工艺,以在所述制备区域形成第一超导层的步骤中,至少部分超导材料沉积于形成所述第三开口的开口侧壁上,以使所述第三开口的开口侧壁间距离减小;其中,所述第三开口的开口侧壁间距离不小于所述第二开口的开口侧壁间距离。

9.根据权利要求6所述的方法,其特征在于,所述方法还包括:

10.一种避免在斜蒸发制造约瑟夫森结时掩膜的沉积窗口减小而导致约瑟夫森结线宽波动的方法,所述掩膜的沉积窗口具有第一开口和第二开口,且所述第一开口和第二开口共同构成底切结构,其特征在于,所述方法包括:

技术总结

本说明书实施方式提供了一种用于制备约瑟夫森结的掩膜结构及相关方法,掩膜结构包括层叠设置的第一掩膜层、第二掩膜层和第三掩膜层;第一掩膜层用于设置在基材的基材表面上;第二掩膜层位于所述第一掩膜层与第三掩膜层之间;掩膜结构具有贯通的窗口;窗口用于在基材表面制备约瑟夫森结;窗口包括位于第一掩膜层的第一开口,位于第二掩膜层的第二开口和位于第三掩膜层的第三开口;其中,第二开口在基材表面的垂直投影,位于第一开口和第三开口在基材表面的垂直投影内。该方案可以在一定程度上提升制备出的约瑟夫森结线宽的准确性。

技术研发人员:请求不公布姓名,请求不公布姓名,贾志龙

受保护的技术使用者:本源量子计算科技(合肥)股份有限公司

技术研发日:

技术公布日:2024/3/4

- 还没有人留言评论。精彩留言会获得点赞!