一种晶圆固定装置及晶圆镀膜设备的制作方法

本申请涉及半导体制造,具体涉及一种晶圆固定装置及晶圆镀膜设备。

背景技术:

1、晶圆验收实验(wafer acceptance test,wat)是测试晶圆中芯片的一种实验,其原理为利用探针卡的探针接触晶圆上的芯片以将测试讯号经由探针传导至芯片上,以测试芯片的功能,最后由测试程序判定各个芯片的好坏,以取得晶圆的测试图(map)。

2、现有技术中,高密度等离子体化学气相沉积(high density plasma chemicalvapor deposition,hdp cvd)工艺具有良好的间隙填充能力,常被用来作为金属间隔离的重要工艺,在铝线制程中被广泛使用,此工艺还可以用于晶圆测试中。

3、但是,由于hdp cvd工艺进程中,高密度等离子会在晶圆芯片上的多层金属上沉积,由于晶圆上有个缺口(notch),高密度等离子经过晶圆缺口处时会穿过缺口沉积在静电吸盘上,从而产生电弧(arcing),进而出现高密度等离子在晶圆芯片上沉积不均匀的结果,使得后续的晶圆测试中出现特殊测试图案(special map),并且会导致对晶圆芯片的栅极氧化层完整性(goi:gate oxide integrity)测试进程不能顺利进行。

4、因此,如何避免高密度等离子在晶圆芯片上沉积不均匀而导致晶圆测试失败是目前亟待解决的问题。

技术实现思路

1、鉴于此,本申请提供一种晶圆固定装置及晶圆镀膜设备,以解决因高密度等离子在晶圆芯片上沉积不均匀而导致晶圆测试失败的问题。

2、本申请提供的晶圆固定装置包括固定盘和吸附装置,所述固定盘用于放置晶圆,所述吸附装置设置于所述固定盘底端;

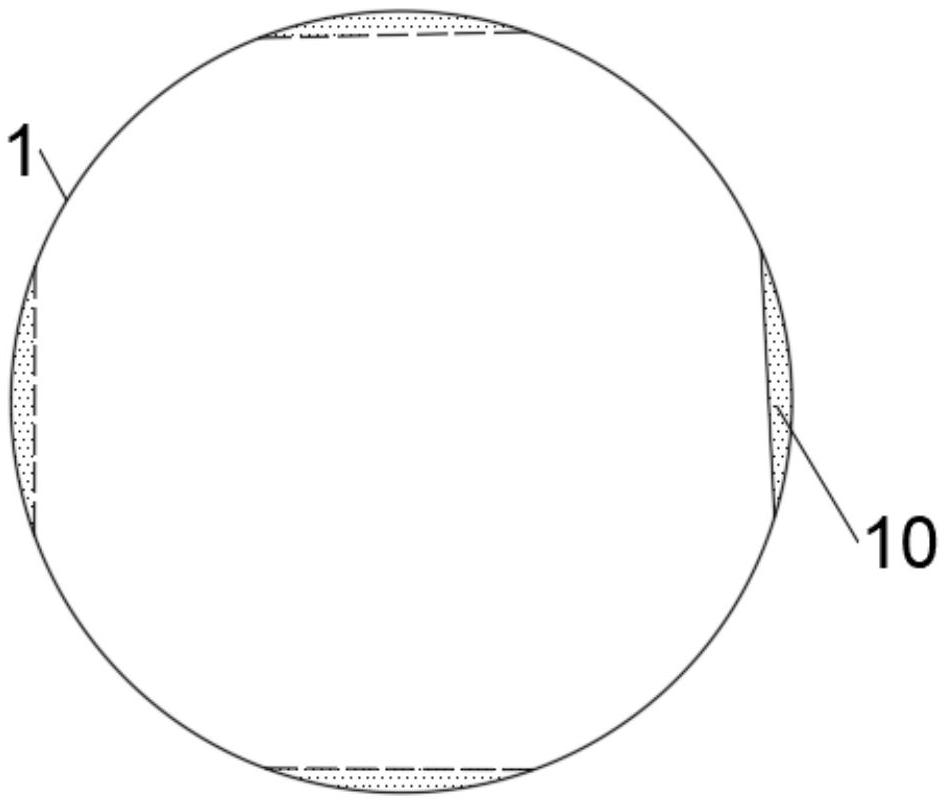

3、所述固定盘的顶端边缘外侧设置有若干缺口槽,若干所述缺口槽在所述固定盘上均匀且等距分布,所述晶圆的边缘设置有缺口,所述缺口槽的形状与所述缺口的形状相匹配。

4、可选地,所述缺口槽的底面面积大于所述缺口的底面面积。

5、可选地,所述缺口槽的数量为3个,任意一个所述缺口槽的中心分别与其相邻两个所述缺口槽的中心连线形成的连线角的角度为60°,任意两个所述缺口槽关于所述固定盘的中心对称。

6、可选地,所述缺口槽的数量为4个,任意一个所述缺口槽的中心分别与其相邻的两个所述缺口槽的中心连线形成的连线角的角度为90°,任意两个所述缺口槽关于所述固定盘的中心对称。

7、可选地,所述固定盘包括静电吸盘,所述吸附装置包括静电产生组件,所述静电产生组件连接所述静电吸盘。

8、可选地,所述固定盘上设置有温度监测单元和红外感应发射单元,所述温度监测单元和所述红外感应发射单元均连接控制单元。

9、本申请提供的晶圆镀膜设备包括腔体和所述晶圆固定装置,所述腔体内设置有反应腔,所述晶圆固定装置设置于所述反应腔的底端。

10、本申请的晶圆固定装置及晶圆镀膜设备的有益效果在于:

11、在腔体的反应腔内设置晶圆固定装置,晶圆固定装置包括固定盘和吸附装置,通过固定盘和吸附装置的配合稳定晶圆,进而保证了晶圆镀膜时的稳定性和镀膜质量;在固定盘的顶端边缘外侧均匀且等距设置有若干与晶圆的缺口匹配的缺口槽,在每次镀膜前,放置晶圆使得缺口位于缺口槽正上方,使得后续hdp cvd工艺进程中,高密度等离子不会穿过缺口沉积在固定盘上,避免产生电弧影响镀膜质量;在每完成一次cvd沉积的工艺流程后,旋转晶圆使得旋转后的缺口与缺口槽上下位置对应匹配,在避免产生电弧的同时使得高密度等离子能在晶圆上均匀沉积和分布,解决了因高密度等离子在晶圆芯片上沉积不均匀而导致晶圆测试失败的问题,进而提高了晶圆的镀膜质量和晶圆的良品率。

技术特征:

1.一种晶圆固定装置,其特征在于,包括固定盘和吸附装置,所述固定盘用于放置晶圆,所述吸附装置设置于所述固定盘底端;

2.如权利要求1所述的晶圆固定装置,其特征在于,所述缺口槽的底面面积大于所述缺口的底面面积。

3.如权利要求2所述的晶圆固定装置,其特征在于,所述缺口槽的数量为3个,任意一个所述缺口槽的中心分别与其相邻两个所述缺口槽的中心连线形成的连线角的角度为60°,任意两个所述缺口槽关于所述固定盘的中心对称。

4.如权利要求2所述的晶圆固定装置,其特征在于,所述缺口槽的数量为4个,任意一个所述缺口槽的中心分别与其相邻的两个所述缺口槽的中心连线形成的连线角的角度为90°,任意两个所述缺口槽关于所述固定盘的中心对称。

5.如权利要求1所述的晶圆固定装置,其特征在于,所述固定盘包括静电吸盘,所述吸附装置包括静电产生组件,所述静电产生组件连接所述静电吸盘。

6.如权利要求5所述的晶圆固定装置,其特征在于,所述固定盘上设置有温度监测单元和红外感应发射单元,所述温度监测单元和所述红外感应发射单元均连接控制单元。

7.一种晶圆镀膜设备,其特征在于,包括腔体和如权利要求1-6任意一项所述的晶圆固定装置,所述腔体内设置有反应腔,所述晶圆固定装置设置于所述反应腔的底端。

技术总结

本申请公开一种晶圆固定装置及晶圆镀膜设备,包括固定盘和吸附装置,固定盘用于放置晶圆,吸附装置设置于固定盘底端;固定盘的顶端边缘外侧设置有若干缺口槽,若干缺口槽在固定盘上均匀且等距分布,晶圆的边缘设置有缺口,缺口槽的形状与缺口的形状相匹配,本申请的晶圆固定装置保证了晶圆镀膜时的稳定性和镀膜质量,在避免产生电弧的同时使得高密度等离子能在晶圆上均匀沉积和分布,解决了因高密度等离子在晶圆芯片上沉积不均匀而导致晶圆测试失败的问题,进而提高了晶圆的镀膜质量和晶圆的良品率。

技术研发人员:李冯意郎,施敏,官亚洲,刘洋

受保护的技术使用者:粤芯半导体技术股份有限公司

技术研发日:20230804

技术公布日:2024/3/21

- 还没有人留言评论。精彩留言会获得点赞!