半导体单晶衬底的宏观缺陷消除方法及半导体单晶衬底

本申请涉及一种半导体单晶衬底,具体涉及一种半导体单晶衬底的宏观缺陷消除方法,属于半导体。

背景技术:

1、半导体单晶衬底作为微电子和光电子的关键支撑材料,具有巨大的市场价值和极大的附加值及特有的产业生态作用,特别是以碳化硅、氮化镓、氧化锌等为代表的第三代半导体晶体,具有高击穿电场、高饱和电子速度、高热导率、高电子密度、高迁移率等特点,可广泛应用于光电器件和高功率器件,被视为未来支撑信息、能源、交通、国防等产业发展的重点新材料,是各国竞相发展的战略性新兴产业。

2、iii-v族半导体材料单晶通常采用的生长方法有气相法和液相法。气相法有氢化物气相外延(hvpe)、物理气相传输(pvt)、金属有机化学气相沉积(mocvd)和分子束外延(mbe)等。液相法有高压溶液法,氨热法、液相外延法等。气相生长方法中,mocvd、mbe生长速率慢,不适于体单晶生长,主要用来生长gan薄膜和器件结构。氢化物气相hvpe、pvt生长速率快、易得到大尺寸晶体,是目前商业上生产iii-v单晶衬底的主要方法;但这两种方法为远离平衡态生长,受到位错、反相畴和杂质等影响易产生v型坑,产生的部分v形坑随着生长厚度的增加无法合并进而形成孔洞;其他合并的v形坑尽管抛光后表面平整,但由于杂质含量过高,与周围材料光学差别大,在肉眼观察下可以看到“晕”,这些“晕”在外延生长时会向上延伸,极大的影响器件的成品率。一旦iii-v族半导体单晶衬底表面存在上述的孔洞及晕的结构,将会对后续的外延材料生长和器件制备带来极大的影响。首先,孔洞结构的裸露晶面与单晶衬底的表面存在显著的区别,在孔洞及晕的裸露晶面生长的外延材料和器件,与单晶衬底上生长的外延材料和器件结构存在较大的区别,不能制备出满足设计需要的器件,属于无效区域;其次,孔洞结构存在一定的深度,且其边界是不同晶面的连接处,这不仅会导致输入源在孔洞周围形成较大的扰动,也会严重影响原子在孔洞周围的迁移能力,进而影响孔洞周围外延材料的组分、应力甚至是缺陷密度等关键指标,进一步扩大了孔洞的影响范围,特别是能够影响到孔洞周围0.5mm到1mm的范围,造成器件制备良率的下降。最后,由于孔洞存在一定的深度,在后续的器件加工工艺中,由于涉及光刻、刻蚀等工艺,孔洞也会对这些工艺造成很大的影响,例如影响光刻胶甩胶厚度的均匀性,从而降低器件工艺制备的良率。

技术实现思路

1、本申请的主要目的在于提供一种半导体单晶衬底的宏观缺陷消除方法及半导体单晶衬底,以克服现有技术中的不足之处。

2、为实现前述发明目的,本申请采用的技术方案包括:

3、本申请的一个方面提供了一种半导体单晶衬底的宏观缺陷消除方法,其包括:

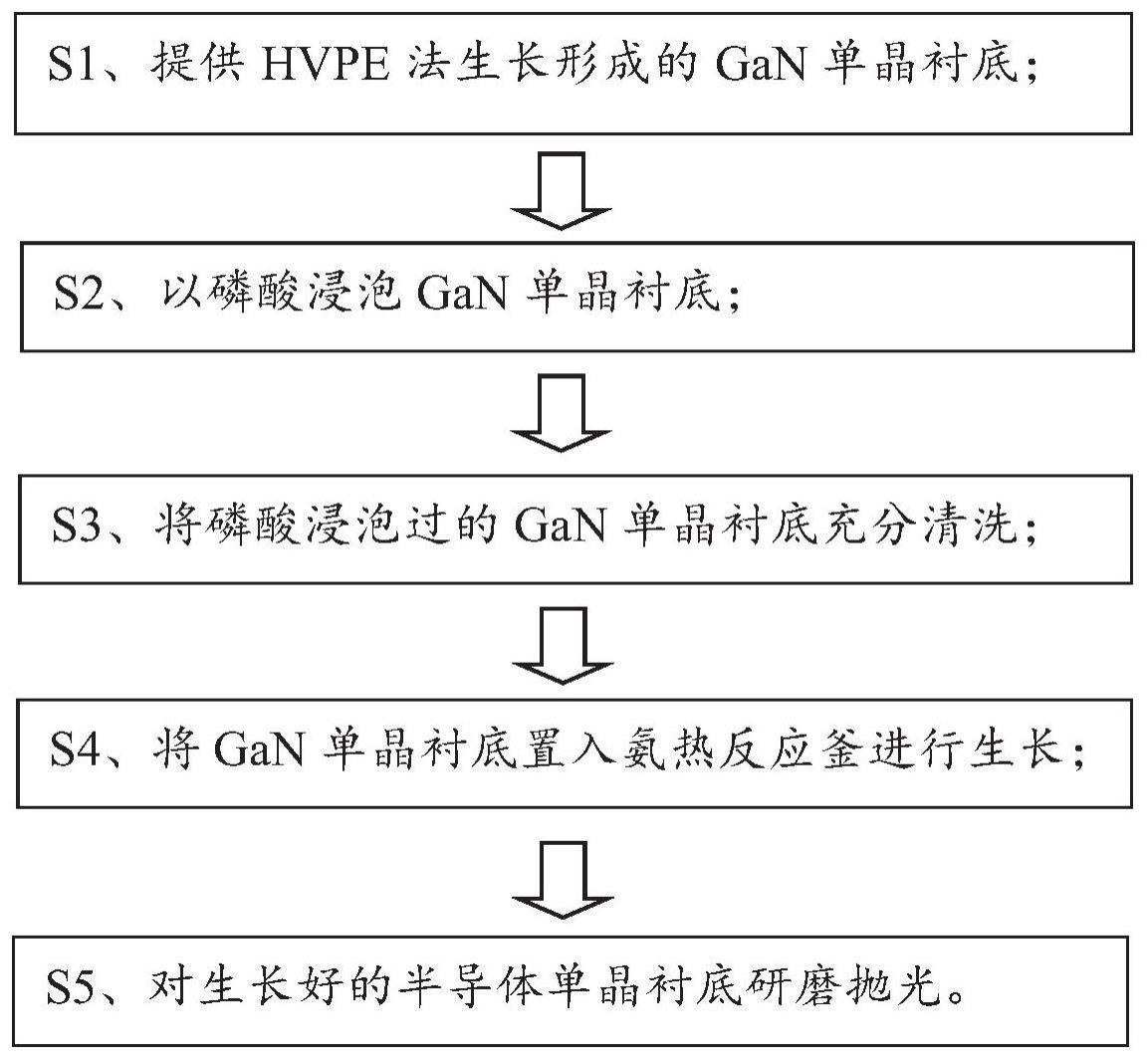

4、s1、提供具有宏观缺陷的iii-v族半导体单晶衬底;

5、s2、采用液相法在所述iii-v族半导体单晶衬底表面生长连续的iii-v族半导体单晶材料层,以将所述宏观缺陷修复及掩盖。

6、其中,所述宏观缺陷的直径在100μm以上,并包括孔洞结构和/或晕状结构。

7、本申请的另一个方面还提供了一种半导体单晶衬底,其包括:

8、iii-v族半导体单晶衬底,其具有一个以上宏观缺陷;

9、iii-v族半导体单晶材料层,其连续覆设于所述iii-v族半导体单晶衬底表面,至少用于将所述宏观缺陷修复及掩盖。

10、较之现有技术,本申请能够有效消除iii-v族半导体单晶衬底中的孔洞结构、晕结构等宏观缺陷,使iii-v族半导体单晶衬底表面材料性能一致且光滑平整,防止在衬底上进行外延工艺时因孔洞结构周围的气体运动产生扰动,并消除了晕状结构的影响,有利于提升后续器件制程的良率,且本申请的工艺简单易行,适合于规模化生产。

技术特征:

1.一种半导体单晶衬底的宏观缺陷消除方法,其特征在于,包括:

2.根据权利要求1所述的半导体单晶衬底的宏观缺陷消除方法,其特征在于,所述宏观缺陷的直径在100μm以上,并包括孔洞结构和/或晕状结构;和/或,步骤s1中所述iii-v族半导体单晶衬底是利用气相法生长形成,所述气相法包括氢化物气相外延法或物理气相传输法;和/或,所述iii-v族半导体单晶衬底、iii-v族半导体单晶材料层的材质包括ga、al、in中的一种或多种与n组成的二元、三元或四元单晶材料。

3.根据权利要求1或2所述的半导体单晶衬底的宏观缺陷消除方法,其特征在于,所述宏观缺陷的直径为100μm~5000μm。

4.根据权利要求1-3中任一项所述的半导体单晶衬底的宏观缺陷消除方法,其特征在于,步骤s1具体包括:以酸或碱溶液浸泡所述iii-v族半导体单晶衬底,以至少除去所述宏观缺陷周边的损伤层及反转畴,之后清洗。

5.根据权利要求4所述的半导体单晶衬底的宏观缺陷消除方法,其特征在于,步骤s1具体包括:

6.根据权利要求2-3中任一项所述的半导体单晶衬底的宏观缺陷消除方法,其特征在于,步骤s2具体包括:

7.根据权利要求1所述的半导体单晶衬底的宏观缺陷消除方法,其特征在于,步骤s2中所述的液相法包括氨热法、高压溶液生长法或助熔剂法;

8.根据权利要求7所述的半导体单晶衬底的宏观缺陷消除方法,其特征在于,步骤s2中所述的液相法为氨热法,且所述液相法具体包括:将经步骤s1处理后的iii-v族半导体单晶衬底置入氨热反应釜,然后使生长区和原料区按照相同升温速度同时升温至一中间温度,并在所述中间温度停留设定时长,之后使生长区和原料区按照不同升温速度升温,直至生长区的温度达到生长温度,并在生长区和原料区之间形成温差。

9.根据权利要求1所述的半导体单晶衬底的宏观缺陷消除方法,其特征在于,步骤s2还包括:在完成所述iii-v族半导体单晶材料层的生长后,对所获半导体单晶衬底进行抛光处理。

10.一种半导体单晶衬底,其特征在于,包括:

11.根据权利要求10所述的半导体单晶衬底,其特征在于,所述宏观缺陷的直径在100μm以上;和/或,所述宏观缺陷包括孔洞结构、晕状结构中的任意一种或多种的组合;和/或,所述半导体单晶衬底的表面平整,且所述半导体单晶衬底表层的材料性能一致;和/或,所述iii-v族半导体单晶衬底、iii-v族半导体单晶材料层的材质包括ga、al、in中的一种或多种与n组成的二元、三元或四元单晶材料。

12.根据权利要求10所述的半导体单晶衬底,其特征在于,所述宏观缺陷的直径为100μm~5000μm;和/或,所述半导体单晶衬底中分布有封闭图形结构,所述封闭图形结构的边界由所述宏观缺陷的边界限定,且所述封闭图形结构的边界内外的半导体材料的发光性质和光学反射率不同。

技术总结

本申请公开了一种半导体单晶衬底的宏观缺陷消除方法及半导体单晶衬底。所述的宏观缺陷消除方法包括:提供具有宏观缺陷的III‑V族半导体单晶衬底;采用液相法在所述III‑V族半导体单晶衬底表面生长连续的III‑V族半导体单晶材料层,以将所述宏观缺陷修复及掩盖。本申请能够有效消除III‑V族半导体单晶衬底中的孔洞结构、晕结构等宏观缺陷,使III‑V族半导体单晶衬底表面材料性能一致且光滑平整,有利于提升后续器件制程的良率,且本申请的工艺简单易行,适合于规模化生产。

技术研发人员:任国强,李腾坤,徐科

受保护的技术使用者:中国科学院苏州纳米技术与纳米仿生研究所

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!