半导体器件、制备方法及微机电系统MEMS与流程

本申请涉及半导体领域,尤其涉及一种半导体器件、制备方法及微机电系统mems。

背景技术:

1、目前,在半导体领域经常用到多晶硅薄膜作为半导体层,尤其是在mems(微机电系统)领域,多晶硅薄膜经常会作为一种功能性或者结构性薄膜来实现振动或者电传导的功能。多晶硅材料表现为典型的半导体材料特性,可以通过对多晶硅材料进行掺杂实现其导电特性。

2、然而,通常为减少掺杂对于多晶硅材料的生长缺陷的影响,降低掺杂气体的流量从而降低掺杂元素的浓度,会导致气体流量精度变差,导致掺杂浓度与设计值有较大的偏差,不能得到想要的目标多晶硅结构薄膜。另外,离子注入是将具有一定能量的离子直接注入到非掺杂多晶硅薄膜中,而具有能量的离子会破坏原有的非掺杂多晶硅薄膜的晶格结构,会对其造成一定的损伤,虽然后续的退火工艺可以消除一部分的晶格损伤,但是对于多晶硅材料的强度会有一定的影响。

技术实现思路

1、本申请实施例提供一种半导体器件、制备方法及微机电系统mems,能够平衡半导体层的杂质掺杂浓度和材料强度的需求,可以保证半导体结构的电学性能和机械强度。

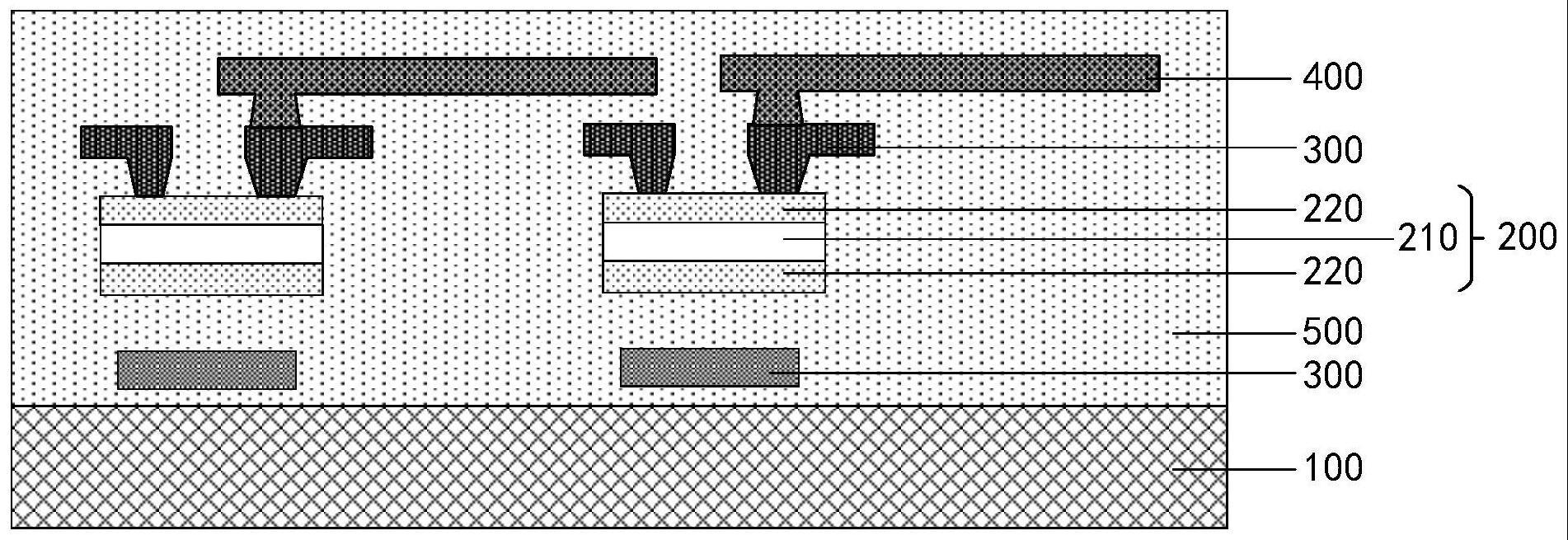

2、本申请实施例的第一方面,提供一种半导体器件,包括:

3、衬底;

4、半导体层,设置于衬底的一侧,所述半导体层包括至少一层非掺杂半导体薄膜层和至少两层掺杂半导体薄膜层,所述非掺杂半导体薄膜层设置于至少两层所述掺杂半导体薄膜层之间;

5、电极,设置于所述衬底与所述半导体层之间,和/或,设置于所述半导体层远离所述衬底的一侧。

6、在一些实施方式中,所述非掺杂半导体薄膜层的厚度大于所述掺杂半导体薄膜层的厚度。

7、在一些实施方式中,所述半导体层包括第一掺杂半导体薄膜层、非掺杂半导体薄膜层和第二掺杂半导体薄膜层,所述非掺杂半导体薄膜层设置于所述第一掺杂半导体薄膜层与所述第二掺杂半导体薄膜层之间,所述第一掺杂半导体薄膜层设置于所述非掺杂半导体薄膜层与所述衬底之间;

8、所述电极包括第一电极和第二电极,所述第一电极与所述半导体层之间设置有绝缘层,所述第二电极与所述半导体层电连接;

9、在所述第一电极设置于所述半导体层远离所述衬底的一侧的情况下,所述第二掺杂半导体薄膜层的厚度大于所述第一掺杂半导体薄膜层的厚度;

10、在所述第一电极设置于所述衬底与所述半导体层之间的情况下,所述第二掺杂半导体薄膜层的厚度小于或等于所述第一掺杂半导体薄膜层的厚度;

11、和/或,

12、所述非掺杂半导体薄膜层的厚度范围为0.4μm至0.6μm;和/或,

13、所述掺杂半导体薄膜层的厚度范围为0.2μm至0.3μm;和/或,

14、所述半导体层的厚度范围为1μm。

15、在一些实施方式中,所述掺杂半导体薄膜层包括杂质粒子和多晶硅薄膜;

16、所述非掺杂半导体薄膜层包括多晶硅薄膜。

17、在一些实施方式中,至少两层所述掺杂半导体薄膜层的所述杂质粒子的掺杂浓度相同。

18、在一些实施方式中,所述掺杂半导体薄膜层和/或所述非掺杂半导体薄膜层是通过化学气相沉积制备得到的;和/或,

19、所述杂质粒子包括硼或磷;和/或,

20、所述衬底包括硅晶片。

21、本申请实施例的第二方面,提供一种半导体器件的制备方法,包括:

22、在衬底的一侧分别设置半导体层和电极,其中,所述电极设置于所述衬底与所述半导体层之间,和/或,所述电极设置于所述半导体层远离所述衬底的一侧;

23、所述设置所述半导体层,包括:

24、在所述衬底的一侧设置至少一层掺杂半导体薄膜层;

25、在至少一层所述掺杂半导体薄膜层远离所述衬底的一侧设置至少一层非掺杂半导体薄膜层;

26、在至少一层所述非掺杂半导体薄膜层远离所述衬底的一侧设置至少一层掺杂半导体薄膜层。

27、在一些实施方式中,设置所述掺杂半导体薄膜层包括:

28、向低压化学气相沉积成膜腔室通入硅烷和杂质粒子化合物,以生长所述掺杂半导体薄膜层,其中,成膜工艺温度大于580℃;

29、或,

30、向等离子增强化学气相沉积成膜腔室通入硅烷和杂质粒子化合物,以生长所述掺杂半导体薄膜层,其中,成膜工艺温度小于580℃;

31、对制备完成的所述掺杂半导体薄膜层进行热退火。

32、在一些实施方式中,所述杂质粒子化合物在化学气相沉积成膜腔室中通入气体总量的体积占比大于或等于1%。

33、本申请实施例的第三方面,提供一种微机电系统mems,包括:

34、如第一方面所述的半导体器件。

35、本申请实施例提供的半导体器件,通过设置半导体层包括至少一层非掺杂半导体薄膜层和至少两层掺杂半导体薄膜层,非掺杂半导体薄膜层设置于至少两层掺杂半导体薄膜层之间,非掺杂半导体薄膜层内未掺杂杂质元素,掺杂半导体薄膜层内掺杂有杂质元素。由于非掺杂半导体薄膜层中未掺杂杂质,则不存在或具有极少的缺陷,机械强度较大。掺杂半导体薄膜层中由于杂质的掺杂,存在微观结构缺陷,机械强度较弱。则将机械强度较强的非掺杂半导体薄膜层设置在机械强度较弱的至少两层掺杂半导体薄膜层之间,至少两层掺杂半导体薄膜层的设置,无需采用降低掺杂材料流量掺杂半导体薄膜层,可以保证掺杂浓度的精度和均匀性,进而可以保证半导体层的掺杂带来的电学性能;非掺杂半导体薄膜层设置在半导体层中间还可以保证半导体层具有一定的机械强度,以抗击外界的冲击和机械应力的缓冲,避免半导体层的机械损伤风险。

技术特征:

1.一种半导体器件,其特征在于,包括:

2.根据权利要求1所述的半导体器件,其特征在于,

3.根据权利要求2所述的半导体器件,其特征在于,

4.根据权利要求1所述的半导体器件,其特征在于,

5.根据权利要求4所述的半导体器件,其特征在于,

6.根据权利要求4所述的半导体器件,其特征在于,

7.一种半导体器件的制备方法,其特征在于,包括:

8.根据权利要求7所述的半导体器件的制备方法,其特征在于,

9.根据权利要求8所述的半导体器件的制备方法,其特征在于,

10.一种微机电系统mems,其特征在于,包括:

技术总结

本申请公开一种半导体器件、制备方法及微机电系统MEMS,涉及半导体技术领域,能够平衡半导体层的杂质掺杂浓度和材料强度的需求,可以保证半导体结构的电学性能和机械强度。半导体器件,包括:衬底;半导体层,设置于衬底的一侧,所述半导体层包括至少一层非掺杂半导体薄膜层和至少两层掺杂半导体薄膜层,所述非掺杂半导体薄膜层设置于至少两层所述掺杂半导体薄膜层之间;电极,设置于所述衬底与所述半导体层之间,和/或,设置于所述半导体层远离所述衬底的一侧。

技术研发人员:王飞飞,李健飞,晋海涛,徐宝盈

受保护的技术使用者:赛莱克斯微系统科技(北京)有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!