具有改进的电荷转移效率的集成电路及相关技术的制作方法

本发明涉及集成器件和相关仪器,其可以通过将较短光学脉冲同时提供到数万个或更多个样本井,并从样本井接收荧光信号以供样本分析来执行样本的大规模并行分析。该仪器可以适用于护理点基因定序和用于个人化医疗。

背景技术:

1、光检测器用于在多种应用中检测光。已经研发出集成光检测器,其产生指示入射光的强度的电信号。用于成像应用的集成光检测器包括像素阵列以检测从跨越场景接收的光的强度。集成光检测器的示例包括电荷耦合器件(charge coupled device,ccd)和互补金属氧化物半导体(complementary metal oxide semiconductor,cmos)图像感测器。

2、能够进行生物或化学样本的大规模并行分析的仪器由于若干因素而通常限于实验室设定,该因素可以包括仪器的较大尺寸、缺乏便携性、需要熟练技术员操作仪器、功率需求、对受控操作环境的需求和成本。在使用这种设备分析样本时,常见范式是在护理点处或现场中提取样本,将样本传送到实验室,并等待分析结果。结果的等待时间可以在数小时至数天范围内。

技术实现思路

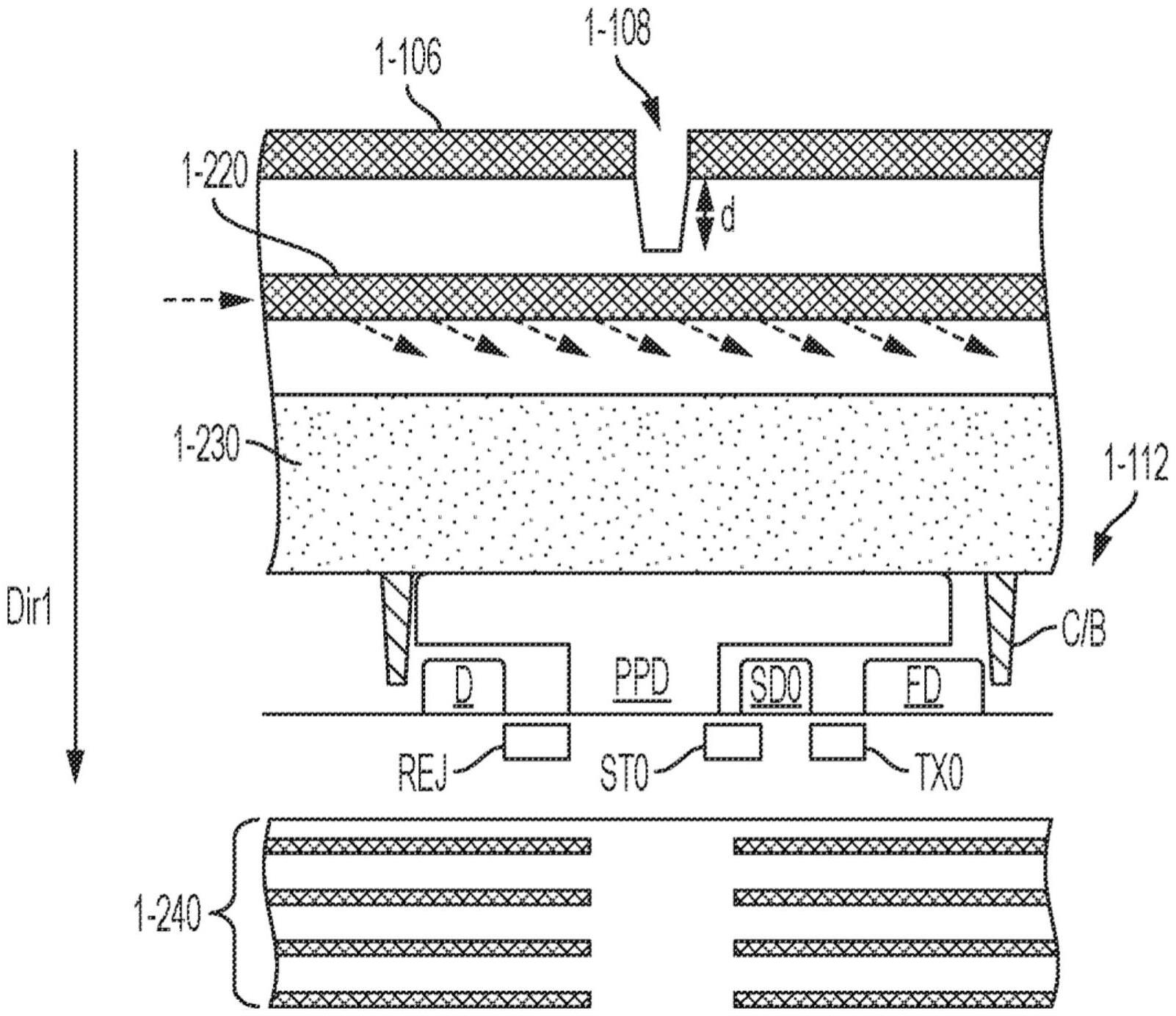

1、本发明的一些方面提供了一种集成电路,其包括:光检测区,其被配置为在第一方向上接收入射光子,响应于接收入射光子而产生电荷载子,并第一方向上引发第一本征电场;以及一个或多个电荷存储区,其被配置为从光检测区接收电荷载子。

2、本发明的一些方面提供了一种方法,其包括:在集成电路的光检测区中在第一方向上引发第一本征电场;在光检测区处在第一方向上接收入射光子;以及在集成电路的一个或多个电荷存储区处接收响应于入射光子而在光检测区中产生的电荷载子。

3、本发明的一些方面提供了一种集成电路,其包括:光检测区,其被配置为响应于接收入射光子而产生电荷载子,并且在第一方向上引发第一本征电场;一个或多个电荷存储区,其被配置为从光检测区接收电荷载子;以及一个或多个转移门,其在第一方向上定位在光检测区和一个或多个电荷存储区之后,并且被配置为控制电荷载子从光检测区到一个或多个电荷存储区和/或从一个或多个电荷存储区到读出区的转移。

4、本发明的一些方面提供了一种方法,其包括:在集成电路的光检测区中在第一方向上引发第一本征电场;响应于接收入射光子而在光检测区中产生电荷载子;在一个或多个电荷存储区处从光检测区接收电荷载子;以及使用在第一方向上定位在光检测区和一个或多个电荷存储区之后的一个或多个转移门控制电荷载子从光检测区到一个或多个电荷存储区和/或从一个或多个电荷存储区到读出区的转移。

5、本发明的一些方面提供了一种集成电路,其包括:光检测区,其被配置为在第一方向上接收入射光子并响应于接收入射光子而产生电荷载子;一个或多个电荷存储区,其被配置为从光检测区接收电荷载子;以及一个或多个带电和/或偏压区,其被配置为引发光检测区中的电荷载子耗尽,以至少部分地在第一方向上将电荷载子从光检测区朝向一个或多个电荷存储区传播。

6、本发明的一些方面提供了一种方法,其包括:在集成电路的光检测区中引发电荷载子耗尽;在光检测区处在第一方向上接收入射光子;响应于接收入射光子而在光检测区中产生电荷载子;至少部分地在第一方向上传播;以及在集成电路的一个或多个电荷存储区处从光检测区接收电荷载子。

7、本发明的一些方面提供了一种集成电路,其包括:光检测区,其被配置为在第一方向上接收入射光子并响应于接收入射光子而产生电荷载子;一个或多个电荷存储区,其被配置为从光检测区接收电荷载子;以及一个或多个区,其被配置为引发光检测区中的本征电荷载子耗尽。

8、本发明的一些方面提供了一种方法,其包括:在集成电路的光检测区中引发本征电荷载子耗尽;在光检测区处在第一方向上接收入射光子;响应于接收入射光子而在光检测区中产生电荷载子;以及在集成电路的一个或多个电荷存储区处从光检测区接收电荷载子。

9、本发明的一些方面提供了一种制造集成电路的方法,该方法包括:形成集成电路的光检测区以便在光检测区中在第一方向上引发第一电场,其中光检测区被配置为在第一方向上接收入射光子。

10、本发明的一些方面提供了一种制造集成电路的方法,该方法包括:形成集成电路的光检测区,并形成一个或多个带电区以引发光检测区中的本征电荷载子耗尽。

11、本发明的一些方面提供了一种制造集成电路的方法,该方法包括:在第一像素的第一光检测区与第二像素的第二光检测区之间形成一个或多个带电和/或偏压区。

12、前文概述不旨在限制。此外,根据各个实施例,本发明的方面可以单独实施或与其他方面结合实施。

技术特征:

1.一种集成电路,其包括:

2.根据权利要求1所述的集成电路,其中,所述光检测区包括具有第一本征电位水平的第一层、和在所述第一方向上定位在所述第一层之后并且具有不同于所述第一本征电位水平的第二本征电位水平的第二层。

3.根据权利要求2所述的集成电路,其中,所述第一层具有第一掺杂剂浓度,并且所述第二层具有高于所述第一掺杂剂浓度的第二掺杂剂浓度。

4.根据权利要求3所述的集成电路,其中,所述光检测区还包括在所述第一方向上定位在所述第二层之后并且具有高于所述第二掺杂剂浓度的第三掺杂剂浓度的第三层。

5.根据权利要求1-4中任一项所述的集成电路,其中,所述光检测区包括具有三角形开口的掩模,其中所述三角形开口的基底在第二方向上定位在所述三角形开口的顶点之后,所述掩模被配置为在所述第二方向上引发从所述光检测区到所述一个或多个电荷存储区的第二本征电场。

6.根据权利要求1-5中任一项所述的集成电路,其中,所述光检测区具有第一掺杂剂浓度并且所述一个或多个电荷存储区至少具有高于所述第一掺杂剂浓度的第二掺杂剂浓度。

7.根据权利要求1-6中任一项所述的集成电路,其还包括被配置为控制电荷载子从所述光检测区到所述一个或多个电荷存储区和/或从所述一个或多个电荷存储区到读出区的转移的一个或多个转移门,其中,所述一个或多个转移门在所述第一方向上定位在所述光检测区和所述一个或多个电荷存储区之后。

8.一种集成电路,其包括:

9.根据权利要求8所述的集成电路,其中,所述光检测区包括具有第一本征电位水平的第一层、和在所述第一方向上定位在所述第一层之后并且具有不同于所述第一本征电位水平的第二本征电位水平的第二层。

10.根据权利要求9所述的集成电路,其中,所述第一层具有第一掺杂剂浓度,所述第二层具有高于所述第一掺杂剂浓度的第二掺杂剂浓度。

11.根据权利要求10所述的集成电路,其中,所述光检测区还包括在所述第一方向上定位在所述第二层之后并且具有高于所述第二掺杂剂浓度的第三掺杂剂浓度的第三层。

12.根据权利要求8-11中任一项所述的集成电路,其中,所述光检测区包括具有三角形开口的掩模,其中所述三角形开口的基底在第二方向上定位在所述三角形开口的顶点之后,所述掩模被配置为在所述第二方向上引发从所述光检测区到所述一个或多个电荷存储区的第二本征电场。

13.根据权利要求8-12中任一项或任何其他前述权利要求所述的集成电路,其中,所述光检测区具有第一本征电位水平,并且所述一个或多个电荷存储区至少具有不同于所述第一本征电位水平的第二本征电位水平。

14.根据权利要求13所述的集成电路,其中,所述光检测区具有第一掺杂剂浓度,并且所述一个或多个电荷存储区至少具有高于所述第一掺杂剂浓度的第二掺杂剂浓度。

15.一种方法,其包括:

16.根据权利要求15所述的方法,其中,至少部分地由所述光检测区的具有第一本征电位水平的第一层和所述光检测区的在所述第一方向上定位在所述第一层之后并且具有不同于所述第一本征电位水平的第二本征电位水平的第二层引发所述第一本征电场。

17.根据权利要求16所述的方法,其中,至少部分地由所述第一层的第一掺杂剂浓度和所述第二层的高于所述第一掺杂剂浓度的第二掺杂剂浓度引发所述第一本征电场。

18.根据权利要求17所述的方法,其中,至少部分地由所述光检测区的在所述第一方向上定位在所述第二层之后并且具有高于所述第二掺杂剂浓度的第三掺杂剂浓度的第三层引发所述第一本征电场。

19.根据权利要求15-18中任一项所述的方法,其进一步包括:

20.根据权利要求15-19中任一项所述的方法,其进一步包括:

21.一种集成电路,其包括:

22.根据权利要求21所述的集成电路,其中,所述一个或多个带电和/或偏压区包括引发所述光检测区中的所述电荷载子耗尽的包括金属氧化物化合物的电荷层。

23.根据权利要求21或权利要求22所述的集成电路,其中,所述一个或多个带电和/或偏压区包括一个或多个金属区,所述一个或多个金属区被配置为在所述集成电路电耦合到电源时,从所述电源接收引发所述光检测区中的所述电荷载子耗尽的电压偏压。

24.根据权利要求21-23中任一项所述的集成电路,其中,所述一个或多个带电和/或偏压区包括:

25.根据权利要求21-24中任一项所述的集成电路,其中,所述一个或多个带电和/或偏压区在所述第一方向上在所述光检测区旁边伸长。

26.根据权利要求21至25中任一项所述的集成电路,其进一步包括被配置为控制电荷载子在所述光检测区与所述一个或多个电荷存储区之间和/或在所述一个或多个电荷存储区与读出区之间的转移的一个或多个转移门,其中,所述一个或多个转移门在所述第一方向上定位在所述光检测区和所述一个或多个电荷存储区之后。

27.根据权利要求21-26中任一项所述的集成电路,其进一步包括围绕所述一个或多个带电和/或偏压区定位的一个或多个掺杂障壁。

28.一种方法,其包括:

29.根据权利要求28所述的方法,其中,至少部分地由所述集成电路的包括具有金属氧化物化合物的电荷层的一个或多个带电区引发所述电荷载子耗尽。

30.根据权利要求28或权利要求29所述的方法,其中,至少部分地由接收电压偏压以引发所述光检测区中的所述电荷载子耗尽的一个或多个金属区引发所述电荷载子耗尽。

31.根据权利要求28-30中任一项所述的方法,其中,在所述光检测区的至少第一侧和所述光检测区的在垂直于所述第一方向的第二方向上与所述第一侧相对的第二侧上,在所述第一方向上从所述光检测区旁边引发所述电荷载子耗尽。

32.根据权利要求28-31中任一项所述的方法,其进一步包括使用一个或多个转移门控制电荷载子在所述光检测区与所述一个或多个电荷存储区之间和/或在所述一个或多个电荷存储区与读出区之间的转移,所述一个或多个转移门在所述第一方向上定位在所述光检测区和所述一个或多个电荷存储区之后。

33.根据权利要求28-32中任一项所述的方法,其进一步包括在所述光检测区处通过在所述第一方向上与所述光检测区的横向端对准的金属屏蔽件的开口接收所述入射光子,所述横向端在垂直于所述第一方向的第二方向上彼此分离。

34.一种集成电路,其包括:

35.根据权利要求34所述的集成电路,其中:

36.根据权利要求34或权利要求35所述的集成电路,其中,所述一个或多个带电和/或偏压区在所述第一方向上在所述第一光检测区旁边在所述光检测区的至少第一侧和所述光检测区的在垂直于所述第一方向的第二方向上与所述第一侧相对的第二侧上伸长。

37.根据权利要求34-36中任一项所述的集成电路,其中,所述一个或多个带电和/或偏压区包括被配置为引发所述第一光检测区中的电荷载子耗尽的包括金属氧化物化合物的电荷层。

38.根据权利要求34-37中任一项所述的集成电路,其中,所述一个或多个带电和/或偏压区包括一个或多个金属区,所述一个或多个金属区被配置为在所述集成电路电耦合到电源时,从所述电源接收引发所述第一光检测区中的所述电荷载子耗尽的电压偏压。

39.根据权利要求34-38中任一项所述的集成电路,其进一步包括被配置为控制电荷载子在所述第一光检测区与所述一个或多个电荷存储区之间和/或在所述一个或多个电荷存储区与读出区之间的转移的一个或多个转移门,其中,所述一个或多个转移门在所述第一方向上定位在所述第一光检测区和所述一个或多个电荷存储区之后。

40.根据权利要求39所述的集成电路,其进一步包括金属屏蔽件,所述金属屏蔽件在所述第一方向上定位在所述一个或多个带电和/或偏压区之前,并且包括在所述第一方向上与所述光检测区的横向端对准的开口,所述横向端在垂直于所述第一方向的方向上彼此分离。

41.一种制造集成电路的方法,所述方法包括:

42.根据权利要求41所述的方法,其中,形成所述光检测区包括:

43.根据权利要求42所述的方法,其中,形成所述光检测区包括:

44.根据权利要求43所述的方法,其中,形成所述光检测区进一步包括掺杂在所述第一方向上定位在所述第二层之后并且具有高于所述第二掺杂剂浓度的第三掺杂剂浓度的第三层。

45.根据权利要求41-44中任一项所述的方法,其进一步包括:

46.一种制造集成电路的方法,所述方法包括在第一像素的第一光检测区与第二像素的第二光检测区之间形成一个或多个带电和/或偏压区。

47.根据权利要求46所述的方法,其中,形成所述一个或多个带电和/或偏压区包括在所述一个或多个带电和/或偏压区中和/或上沉积包括金属氧化物化合物的电荷层,以引发所述第一光检测区中的电荷载子耗尽。

48.根据权利要求47所述的方法,其中,沉积所述电荷层包括:

49.根据权利要求46-48中任一项所述的方法,其中,形成所述一个或多个带电和/或偏压区包括:

50.根据权利要求46-49中任一项所述的方法,其进一步包括:

51.根据权利要求50所述的方法,其中,形成所述第一和第二光检测区包括掺杂所述集成电路的第一面,并且其中,所述一个或多个带电和/或偏压区由所述集成电路的在所述第一方向上与所述第一面相对的第二面形成。

52.根据权利要求50或权利要求51所述的方法,其中,形成所述一个或多个带电和/或偏压区包括:

53.根据权利要求50-52中任一项所述的方法,其中,形成所述一个或多个带电和/或偏压区包括蚀刻以形成至少一个沟槽,并在所述至少一个沟槽中沉积在所述第一方向上在所述第一光检测区旁边伸长的电荷层。

54.根据权利要求50-53中任一项所述的方法,其进一步包括将金属屏蔽件在所述第一方向上定位在所述一个或多个带电和/或偏压区之前,所述金属屏蔽件具有在所述第一方向上与所述光检测区的横向端对准的开口,所述横向端在垂直于所述第一方向的第二方向上彼此分离。

技术总结

本发明提供了用于改进在被配置为接收入射光子的集成电路内的电荷转移的速率和效率的技术。本发明的一些方面涉及被配置为引发一个或多个本征电场的集成电路,该一个或多个本征电场增加了集成电路内的电荷转移的速率和效率。本发明的一些方面涉及被配置为引发集成电路的一个或多个光检测区中的电荷载子耗尽的集成电路。在一些实施例中,一个或多个光检测区中的电荷载子耗尽可以是本征的,因为即使在不存在施加到集成电路的外部电场的情况下也引发耗尽。本发明的一些方面涉及用于操作和/或制造如本文中所述的集成器件的工艺。

技术研发人员:埃里克·A·G·韦伯斯特

受保护的技术使用者:宽腾矽公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!