芯片、芯片检测系统及检测方法与流程

本发明涉及芯片,尤其涉及一种芯片、芯片的检测系统及检测方法。

背景技术:

1、随着科学技术的发展,电子设备越来越多进入人们的生活,芯片作为电子设备的核心部件,其功能性及稳定性决定电子设备能否满足人们实际使用需求,对于芯片的研究越来越受关注。在制造过程中,多引脚芯片一般需要对其晶圆进行cp(chip probe)测试以及对封装后的芯片进行ft(final test)测试。cp测试通过测试夹具上的探针加信号激励给晶圆芯片的焊盘pad,然后测试芯片的功能及性能;ft测试通过将芯片放入测试夹具中并给芯片施加一定压力让芯片pin管脚跟测试夹具管脚接触良好,然后测试芯片的功能及性能。

2、在芯片的测试过程中,例如cp测试阶段,通常需要将晶圆芯片的焊盘pad与测试夹具上的测试管脚进行连接,以对焊盘pad施加激励信号,而焊盘pad与测试管脚之间不可避免的存在接触阻抗,容易对芯片的测试结果造成偏差,若能测量出该接触阻抗的大小,则可以降低这种偏差,提高芯片的测试结果的准确性,而现有的芯片结构中,各焊盘pad之间一般互不相连,相互独立,此种结构难以对焊盘pad和测试管脚之间的接触阻抗进行检测。

技术实现思路

1、本发明实施例提供一种芯片、芯片检测系统及检测方法,能够实现对焊盘pad和测试电路板的测试管脚之间的接触阻抗的大小检测,结构简单,操作便捷。

2、为了解决上述技术问题,第一方面,本发明提供一种芯片,所述芯片包括至少一个焊盘pad;

3、至少一个所述焊盘pad为待测pad,所述芯片还包括与所述待测pad电性连接的辅助pad,所述待测pad和所述辅助pad分别与测试电路板上的测试管脚一一对应电性连接,通过分别检测所述测试管脚的对地电压以计算得到所述待测pad和与所述待测pad电性连接的测试管脚之间的接触阻抗的电阻值。

4、第二方面,本发明还提供一种芯片检测系统,包括:

5、芯片,所述芯片包括至少一个焊盘pad;至少一个所述焊盘pad为待测pad,所述芯片还包括与所述待测pad电性连接的辅助pad;

6、测试电路板,所述测试电路板包括测试夹具、电压采样模块、第一下拉电阻和第一下拉开关,所述测试夹具上设置有与所述待测pad和所述辅助pad一一对应电性连接的测试管脚,所述第一下拉电阻和所述第一下拉开关串联形成第一串联支路,所述第一串联支路的一端与所述待测pad所连接的测试管脚电性连接,所述第一串联支路的另一端接地,所述电压采样模块与所述测试管脚电性连接;

7、控制器,所述控制器与所述芯片通信,并与所述第一下拉开关电性连接,以在测试时控制所述第一下拉开关闭合,从而所述电压采样模块分别检测所述测试管脚的对地电压。

8、第三方面,本发明还提供一种芯片的检测方法,所述芯片包括至少一个焊盘pad,至少一个所述焊盘pad为待测pad,所述芯片还包括与所述待测pad电性连接的辅助pad,所述检测方法包括:

9、将所述芯片上的待测pad和辅助pad分别与测试电路板的测试夹具上的测试管脚一一对应电性连接,其中所述待测pad所连接的测试管脚电性连接有串联的第一下拉电阻和第一下拉开关;

10、通过控制器与所述芯片进行通信,并通过所述控制器控制所述第一下拉开关闭合;

11、利用所述测试电路板的电压采样模块分别检测所述测试管脚的对地电压;

12、根据如下公式计算所述待测pad与所述待测pad所连接的测试管脚之间的接触阻抗:rt1=(v1-v2)/(v2/r1),其中,所述v1表示所述辅助pad所连接的测试管脚的对地电压,v2表示所述待测pad所连接的测试管脚的对地电压,r1表示所述第一下拉电阻的电阻值。

13、有益效果:本发明的芯片,所述芯片包括至少一个焊盘pad;其中至少一个所述焊盘pad为待测pad,所述芯片还包括与所述待测pad电性连接的辅助pad,所述待测pad和所述辅助pad分别与测试电路板的测试管脚一一对应电性连接,通过分别检测所述测试管脚的对地电压,由此根据所述测试管脚的对地电压可以计算出所述待测pad和与所述待测pad电性连接的测试管脚之间的接触阻抗的电阻值,本方案结构简单,操作便捷,且通过确定该接触阻抗的电阻值大小,可以为芯片的其他测试例如cp测试提供参考,以尽可能降低焊盘pad和测试管脚之间的接触阻抗带来的不良影响。

技术特征:

1.一种芯片,其特征在于,所述芯片包括至少一个焊盘pad;

2.根据权利要求1所述的芯片,其特征在于,所述待测pad和所述辅助pad一一对应电性连接;

3.根据权利要求2所述的芯片,其特征在于,当所述待测pad和所述辅助pad一一对应电性连接时,所述辅助pad与所述待测pad通过导线直接电性连接。

4.根据权利要求2所述的芯片,其特征在于,所述芯片还包括与所述待测pad一一对应的辅助开关,所述待测pad通过对应的所述辅助开关与所述辅助pad电性连接。

5.根据权利要求2所述的芯片,其特征在于,所述芯片还包括mfp模块和mfp功能模块,所述mfp模块包括mfp控制器、与所述待测pad电性连接的第一选择开关以及与所述辅助pad电性连接的第二选择开关,所述mfp功能模块有多个;

6.根据权利要求1所述的芯片,其特征在于,所述芯片还包括供电电路,所述供电电路包括上拉电阻和第一供电开关,所述上拉电阻的一端与电压源电性连接,所述上拉电阻的另一端通过所述第一供电开关与所述待测pad或者所述辅助pad电性连接。

7.一种芯片检测系统,其特征在于,包括:

8.根据权利要求7所述的芯片检测系统,其特征在于,所述辅助pad和所述待测pad一一对应电性连接;

9.根据权利要求8所述的芯片检测系统,其特征在于,当所述待测pad和所述辅助pad一一对应电性连接时,所述辅助pad与所述待测pad通过导线直接电性连接;

10.根据权利要求9所述的芯片检测系统,其特征在于,所述测试电路板还包括第二下拉电阻和第二下拉开关,所述第二下拉电阻和所述第二下拉开关串联形成第二串联支路,所述第二串联支路的一端与所述辅助pad所连接的测试管脚电性连接,所述第二串联支路的另一端接地。

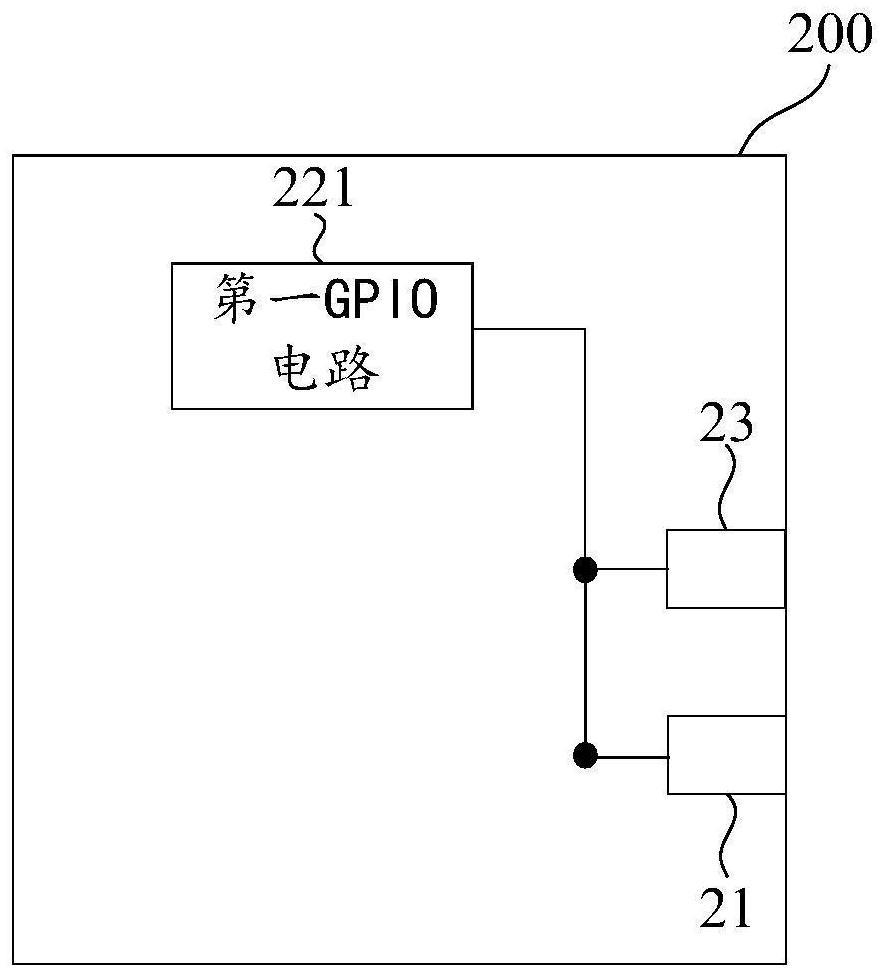

11.根据权利要求7所述的芯片检测系统,其特征在于,所述电压采样模块包括分别与所述测试管脚一一对应电性连接的多个电压采样电路;

12.根据权利要求7所述的芯片检测系统,其特征在于,所述芯片上还设置有供电电路,所述供电电路包括上拉电阻和第一供电开关,所述上拉电阻的一端与电压源电性连接,所述上拉电阻的另一端通过所述第一供电开关与所述待测pad或者所述辅助pad电性连接;

13.一种芯片的检测方法,其特征在于,所述芯片包括至少一个焊盘pad,至少一个所述焊盘pad为待测pad,所述芯片还包括与所述待测pad电性连接的辅助pad,所述检测方法包括:

技术总结

本发明实施例公开了一种芯片、芯片检测系统及检测方法,所述芯片包括至少一个焊盘PAD;其中至少一个所述焊盘PAD为待测PAD,所述芯片还包括与所述待测PAD电性连接的辅助PAD,所述待测PAD和所述辅助PAD分别与测试电路板的测试管脚一一对应电性连接,以通过分别检测所述测试管脚的对地电压,由此根据所述测试管脚的对地电压可以计算出所述待测PAD和与所述待测PAD电性连接的测试管脚之间的接触阻抗的电阻值。

技术研发人员:李刚,罗春艺

受保护的技术使用者:炬芯科技股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!