适用于多脚位芯片的脚位检测系统及其方法与流程

一种检测系统及其方法,尤其是指一种提供jtag连接端口、检测用芯片与待测试芯片夹具通过检测电路串接以构成jtag链路的芯片检测电路板,检测装置通过jtag控制器对芯片检测电路板的待检测芯片进行脚位检测的适用于多脚位芯片的脚位检测系统及其方法。

背景技术:

1、现有对于复杂的多脚位芯片的检测,除了对芯片的外观、锡球氧化……等对其进行品质确认之外,更需要对复杂的多脚位芯片进行功能检测,复杂的多脚位芯片进行功能检测一般是使用小批量打样方式以测算良率,现有的检测方式具有检测成本较高、检测周期较长以及检测方式复杂不便批量化检测的问题。

2、综上所述,可知现有技术中长期以来一直存在现有对于复杂的多脚位芯片检测具有检测成本较高、检测周期较长以及检测方式复杂不便批量化检测的问题,因此有必要提出改进的技术手段,来解决此问题。

技术实现思路

1、有鉴于现有技术存在现有对于复杂的多脚位芯片检测具有检测成本较高、检测周期较长以及检测方式复杂不便批量化检测的问题,本发明遂公开一种适用于多脚位芯片的脚位检测系统及其方法,其中:

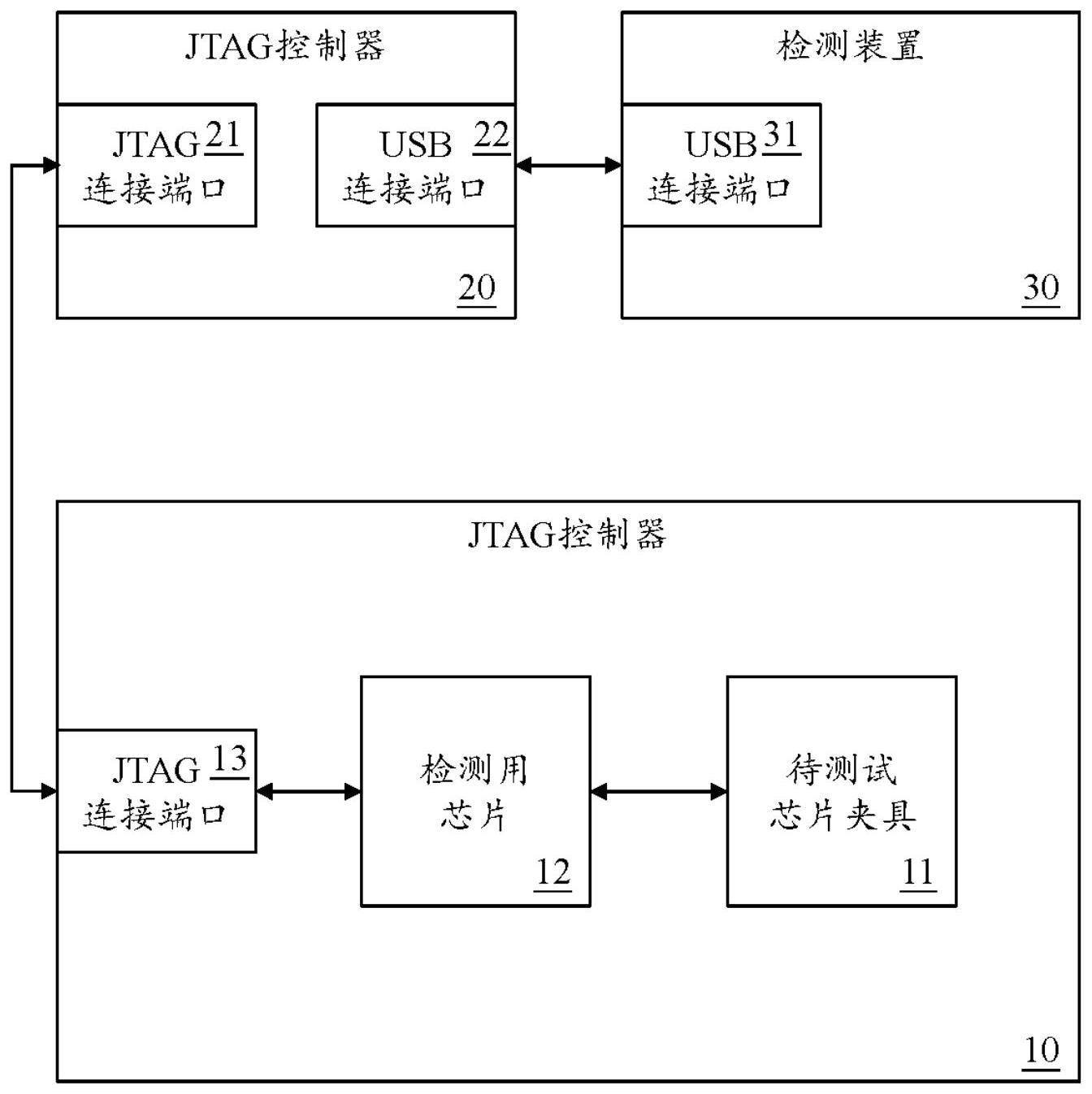

2、本发明所公开的适用于多脚位芯片的脚位检测系统,其包含:芯片检测电路板、联合测试工作群组(joint test action group,jtag)控制器以及检测装置,芯片检测电路板还包含:待测试芯片夹具、检测用芯片以及jtag连接端口。

3、芯片检测电路板具有检测电路,芯片检测电路板的待测试芯片夹具与检测电路形成电性连接,待测试芯片夹具提供待检测芯片夹持固定;检测用芯片与检测电路形成电性连接,检测用芯片的每一个脚位分别与待测试芯片夹具对应的每一个脚位通过检测电路彼此形成电性连接;其中,jtag连接端口、检测用芯片与待测试芯片夹具通过所述检测电路串接以构成jtag链路。

4、jtag控制器与jtag连接端口形成电性连接;检测装置与jtag控制器形成电性连接,检测装置生成检测信号;其中,检测装置发送检测信号至jtag控制器,jtag控制器发送检测信号至芯片检测电路板,芯片检测电路板依据检测信号对待检测芯片的每一个脚位分别进行检测并反馈检测结果回检测装置以完成待检测芯片脚位的检测。

5、本发明所公开的适用于多脚位芯片的脚位检测方法,其包含下列步骤:

6、首先,提供具有检测电路、待测试芯片夹具、检测用芯片以及jtag连接端口的芯片检测电路板;接着,待测试芯片夹具与检测电路形成电性连接,待测试芯片夹具提供待检测芯片夹持固定;接着,检测用芯片与检测电路形成电性连接,检测用芯片的每一个脚位分别与待测试芯片夹具对应的每一个脚位通过检测电路彼此形成电性连接;接着,jtag连接端口、检测用芯片与待测试芯片夹具通过检测电路串接以构成jtag链路;接着,jtag控制器与jtag连接端口形成电性连接;接着,检测装置与jtag控制器形成电性连接,检测装置生成检测信号;最后,检测装置发送检测信号至jtag控制器,jtag控制器发送检测信号至芯片检测电路板,芯片检测电路板依据检测信号对待检测芯片的每一个脚位分别进行检测并反馈检测结果回检测装置以完成待检测芯片脚位的检测。

7、本发明所公开的系统及方法如上,与现有技术之间的差异在于提供具有检测电路、待测试芯片夹具、检测用芯片以及jtag连接端口的芯片检测电路板,检测用芯片的每一个脚位分别与待测试芯片夹具对应的每一个脚位通过检测电路彼此形成电性连接,jtag连接端口、检测用芯片与待测试芯片夹具通过检测电路串接以构成jtag链路,检测装置、jtag控制器与芯片检测电路板形成串接,检测装置生成检测信号通过jtag控制器对芯片检测电路板的待检测芯片的每一个脚位分别进行检测并反馈检测结果回检测装置以完成待检测芯片脚位的检测。

8、通过上述的技术手段,本发明可以达成提供方便且快速对多脚位芯片的脚位进行功能检测的技术功效。

技术特征:

1.一种适用于多脚位芯片的脚位检测系统,其包含:

2.根据权利要求1所述的适用于多脚位芯片的脚位检测系统,其中所述检测装置比对提供待检测芯片该脚位的检测信号与待检测芯片该脚位反馈的检测结果相同时,待检测芯片该脚位为正常。

3.根据权利要求1所述的适用于多脚位芯片的脚位检测系统,其中所述检测装置比对提供待检测芯片该脚位的检测信号与待检测芯片该脚位反馈的检测结果不相同时,待检测芯片该脚位为开路异常。

4.根据权利要求1所述的适用于多脚位芯片的脚位检测系统,其中所述检测装置提供待检测芯片的两个脚位不相同的检测信号,待检测芯片的两个脚位反馈的检测结果为相同的检测结果,待检测芯片的两个脚位为短路异常。

5.根据权利要求1所述的适用于多脚位芯片的脚位检测系统,其中所述待测试芯片夹具、所述检测用芯片以及所述jtag连接端口分别定义有测试数据输入(test data input,tdi)脚位、测试数据输出(test data output,tdo)脚位、测试时钟(test clock,tck)脚位以及测试模式选择(test mode select,tms)脚位,所述待测试芯片夹具、所述检测用芯片以及所述jtag连接端口的tck脚位彼此相连,所述待测试芯片夹具、所述检测用芯片以及所述jtag连接端口的tms脚位彼此相连,所述jtag连接端口的tdi脚位与所述检测用芯片的tdi脚位相连,所述检测用芯片的tdo脚位与所述待测试芯片夹具的tdi脚位相连,所述待测试芯片夹具的tdo脚位与所述jtag连接端口的tdo脚位相连,使所述jtag连接端口、所述检测用芯片与所述待测试芯片夹具通过检测电路串接以构成jtag链路。

6.一种适用于多脚位芯片的脚位检测方法,其包含下列步骤:

7.根据权利要求6所述的适用于多脚位芯片的脚位检测方法,其中所述检测装置比对提供待检测芯片该脚位的检测信号与待检测芯片该脚位反馈的检测结果相同时,待检测芯片该脚位为正常。

8.根据权利要求6所述的适用于多脚位芯片的脚位检测方法,其中所述检测装置比对提供待检测芯片该脚位的检测信号与待检测芯片该脚位反馈的检测结果不相同时,待检测芯片该脚位为开路异常。

9.根据权利要求6所述的适用于多脚位芯片的脚位检测方法,其中所述检测装置提供待检测芯片的两个脚位不相同的检测信号,待检测芯片的两个脚位反馈的检测结果为相同的检测结果,待检测芯片的两个脚位为短路异常。

10.根据权利要求6所述的适用于多脚位芯片的脚位检测方法,其中所述待测试芯片夹具、所述检测用芯片以及所述jtag连接端口分别定义有tdi脚位、tdo脚位、tck脚位以及tms脚位,所述待测试芯片夹具、所述检测用芯片以及所述jtag连接端口的tck脚位彼此相连,所述待测试芯片夹具、所述检测用芯片以及所述jtag连接端口的tms脚位彼此相连,所述jtag连接端口的tdi脚位与所述检测用芯片的tdi脚位相连,所述检测用芯片的tdo脚位与所述待测试芯片夹具的tdi脚位相连,所述待测试芯片夹具的tdo脚位与所述jtag连接端口的tdo脚位相连,使所述jtag连接端口、所述检测用芯片与所述待测试芯片夹具通过检测电路串接以构成jtag链路。

技术总结

一种适用于多脚位芯片的脚位检测系统及其方法,提供具有检测电路、待测试芯片夹具、检测用芯片以及JTAG连接端口的芯片检测电路板,检测用芯片的每一个脚位分别与待测试芯片夹具对应的每一个脚位通过检测电路彼此形成电性连接,JTAG连接端口、检测用芯片与待测试芯片夹具通过检测电路串接以构成JTAG链路,检测装置、JTAG控制器与芯片检测电路板形成串接,检测装置生成检测信号通过JTAG控制器对芯片检测电路板的待检测芯片的每一个脚位分别进行检测并反馈检测结果回检测装置以完成待检测芯片脚位的检测,藉此可以达成提供方便且快速对多脚位芯片的脚位进行功能检测的技术功效。

技术研发人员:赵晋东

受保护的技术使用者:英业达科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!