用于快速对数字标准单元进行测试的电路及版图形成方法与流程

本发明涉及测试,具体涉及一种用于快速对数字标准单元进行测试的电路及版图形成方法。

背景技术:

1、在半导体设计中,标准单元是一种设计具有主要数字逻辑特征的专用集成电路(asic)的方法。标准单元是一组提供布尔逻辑功能(例如:与、或、异或、异或非、反相器)或存储功能(触发器或锁存器)的晶体管和互连结构。

2、标准单元设计的主要性能指标是频率和功耗,这两种参数结果也影响了最终芯片的频率和功耗结果。提升标准单元频率、功耗评估验证的准确性,使其能够更加接近于实际的制造测试数值,可以提升后续芯片设计的准确性,减少设计验证的偏差,提高设计到最终制造的芯片品质。

3、为此,在设计阶段,需要对标准单元的性能指标进行仿真测试。

4、然而,现有对标准单元的性能指标进行仿真测试的结果,与最终制造的标准单元所处的环境之间偏差较大,影响芯片的准确设计,最终影响芯片的品质。

技术实现思路

1、本发明要解决的问题是:提升对标准单元的性能指标测试的准确性,以提升最终芯片的品质。

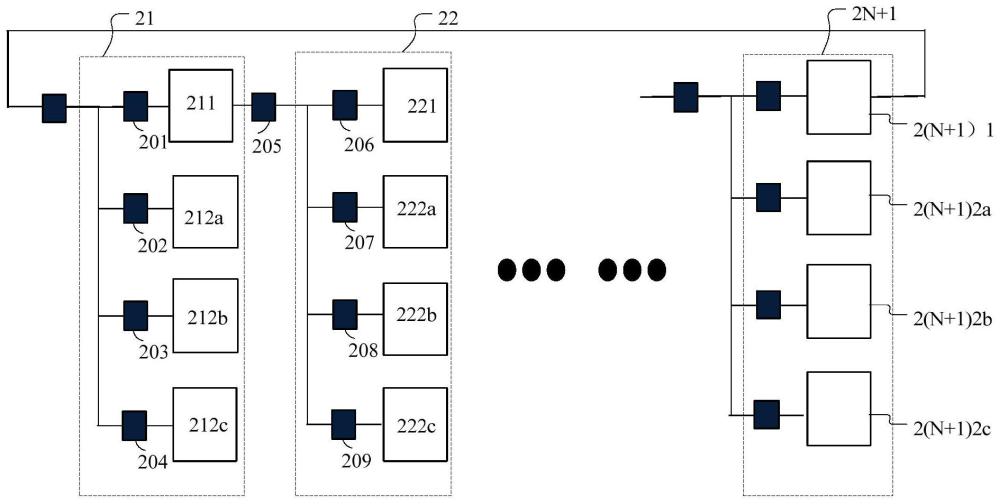

2、为解决上述问题,本发明实施例提供了一种用于快速对芯片中导线连接下的数字标准单元进行性能功耗测试的电路,包括:导线网络和被测试单元连接形成的闭合振荡回路;

3、被测试单元包括:主干震荡单元和负载单元,都是所需被测试的同一数字标准单元;

4、被测试单元之间通过导线网络进行连接,在主干震荡单元内产生震荡信号,负载单元根据需要选择挂载数目;

5、导线网络由导线单元组合而成;所述导线网络根据实际测试需要进行设定,根据测试数字标准单元在芯片中的导线连接形成;所述导线单元与被测试单元具有相同的芯片结构,包括所有工序中形成的导线层;所述导线单元包括一组不同规格的提供不同金属层和金属长度的导线单元库组,根据导线网络选取不同规格导线单元经过排布组合,形成与所述被测试单元在实际芯片中排布相同的导线布局结构。

6、可选地,相邻级所述被测试单元之间通过导线网络相互连接,形成闭环振荡电路。

7、可选地,每个所述负载单元及所述主干振荡单元,根据测试需求选取负载单元数量与主干震荡单元并联。

8、可选地,所述电路中,在相同的导线单元内的传输线排布结构相同。

9、可选地,每一级被测试单元间通过的导线网络相同,而单一导线网络中根据需要由不同导线单元排布连接形成。

10、可选地,所述电路中各所述被测试单元的结构均相同。

11、可选地,所述导线单元内,同一结构层的传输线呈几字型排布。

12、可选地,所述导线单元内,奇数结构层内传输线的延伸方向,与偶数结构层内传输线的延伸方向不同。

13、本发明实施例还提供了一种上述电路的版图形成方法,所述方法包括:

14、根据测试需求,获取被测标准单元在实际芯片中的导线网络信息;

15、根据所获取的导线网络信息形成导线单元,并将所述导线单元组成导线网络;

16、将被测试标准单元作为主干振荡单元,接入所述导线网络,形成不同级的被测试单元;不同级被测试单元之间通过由导线单元构成的导线网络进行连接,形成闭环振荡测试电路。

17、可选地,所述根据所获取的导线内传输线的排布信息形成导线单元,并按照所获取的导线网络信息将所述导线单元组成导线网络,包括:

18、根据所获取的导线网络信息,结合测试需求,形成对应不同测试需求的多种导线单元,并按照所获取的导线网络信息将所述每种导线单元组成对应的导线网络,以形成对应不同测试需求的多种振荡器测试电路。

19、与现有技术相比,本发明实施例的技术方案具有以下优点:

20、应用本发明的方案,被测试单元之间通过导线网络进行连接,导线网络由导线单元组合而成。所述导线网络根据实际测试需要进行设定,根据测试数字标准单元在芯片中的导线连接形成。其中,所述导线单元与被测试的标准单元具有相同的芯片结构,包括所有工序中形成的导线层;所述导线单元包括一组不同规格的提供不同金属层和金属长度的导线单元库组,根据导线网络选取不同规格导线单元经过排布组合,形成与所述被测试标准单元在实际芯片中排布相同的导线布局结构。通过导线单元的设置,可以更准确地模拟被测试单元在实际芯片中导线,由此可以减小与实际芯片中导线之间的偏差,从而可以更准确地获得标准单元的性能参数,最终改善芯片的品质。

技术特征:

1.一种用于快速对芯片中导线连接下的数字标准单元进行性能功耗测试的电路,其特征在于,包括:导线网络和被测试单元连接形成的闭合振荡回路;

2.如权利要求1所述的电路,其特征在于,相邻级所述被测试单元之间通过导线网络相互连接,形成闭环振荡电路。

3.如权利要求1所述的电路,其特征在于,每个所述负载单元及所述主干振荡单元,根据测试需求选取负载单元数量与主干震荡单元并联。

4.如权利要求1所述的电路,其特征在于,所述电路中,在相同的导线单元内的传输线排布结构相同。

5.如权利要求1所述的电路,其特征在于,每一级被测试单元间通过的导线网络相同,而单一导线网络中根据需要由不同导线单元排布连接形成。

6.如权利要求1所述的电路,其特征在于,所述电路中各所述被测试单元的结构均相同。

7.如权利要求1所述的电路,其特征在于,所述导线单元内,同一导线层的传输线呈几字型排布。

8.如权利要求1所述的电路,其特征在于,所述导线单元内,奇数导线层内传输线的延伸方向,与偶数导线层内传输线的延伸方向不同。

9.一种权利要求1至8任一项所述电路的版图形成方法,其特征在于,包括:

10.如权利要求9所述的版图形成方法,其特征在于,所述根据所获取的导线内传输线的排布信息形成导线单元,并按照所获取的导线网络信息将所述导线单元组成导线网络,包括:

技术总结

一种用于快速对芯片中导线连接下的数字标准单元进行性能功耗测试的电路及版图形成方法。所述测试电路包括:由导线单元网络和被测试单元形成的闭合振荡回路;其中被测试单元包括:主干振荡单元及负载单元;所述负载单元和主干震荡单元为同一种数字标准单元;导线网络由导线单元组合而成;所述导线网络根据实际测试需要进行设定,根据被测试单元在芯片中的导线连接形成;所述导线单元与被测试单元具有相同的芯片结构;所述导线单元包括一组不同规格的提供不同金属层和金属长度的导线单元库组,根据导线网络选取不同规格导线单元经过排布组合,形成与所述被测试单元在实际芯片中排布相同的导线布局结构。采用上述方案,可以提升最终芯片的品质。

技术研发人员:钱茂程,苏俊英,蔡燕飞,郁扬,于海洋

受保护的技术使用者:中芯国际集成电路制造(上海)有限公司

技术研发日:

技术公布日:2024/3/4

- 还没有人留言评论。精彩留言会获得点赞!