一种温度传感器电路

驱动,在φ1为高电平且φ2为低电平时,∑-δ模数转换器会用采样电容cs采集输入电压v

ptat

。在φ1为低电平且φ2为高电平时,∑-δ模数转换器会将采集到的电荷累积到∑-δ模数转换器的积分电容c

int

上,并将积分电容c

int

的电压与共模电压v

ref

相比较,积分电容c

int

的电压大于共模电压v

ref

则输出1,积分电容c

int

的电压小于等于共模电压v

ref

则输出0,比较器结果即为输出位码流信号bs,则:

13.所述校正调制器由一个数字累加器和一个数字比较器构成,其中,数字累加器内部寄存器上的值随着时钟周期不断自增,并在超过最大范围之后重置归零;数字比较器将数字累加器内的数值与设定的校正值比较大小,并依据比较结果控制所述前端感温电路中对应bjt管的v

be

作为前端感温电路的输出,其中,前端感温电路使用一对二极管接法的bjt:

14.在当前时钟周期内:若bs=1,校正调制器内的数字累加器在φ1的上升沿进行自加操作,并依据数字比较器的比较结果控制前端感温电路输出的v

be

作为∑-δ模数转换器的输入;若bs=0,校正调制器内的数字累加器暂停自加,输出结果保持不变,并把当前的v

be

作为∑-δ模数转换器的输入。

15.本发明提出基于cmos工艺的高精度、高分辨率温度传感器集成电路解决方案,通过动态元件匹配、校正与位码流控制等技术消除因元件失配和互调失真等现象产生的误差,显著提升温度检测精度和分辨率。

附图说明

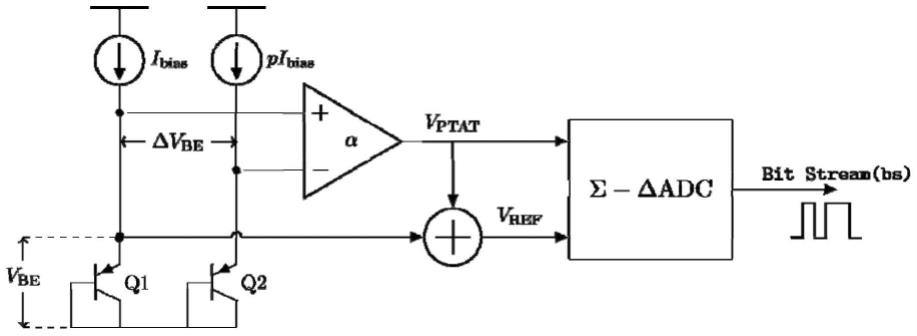

16.图1为本发明的原理图;

17.图2为动态元件匹配逻辑电路的原理图;

18.图3示意了动态元件匹配逻辑电路的切换原理。

具体实施方式

19.下面结合具体实施例,进一步阐述本发明。应理解,这些实施例仅用于说明本发明而不用于限制本发明的范围。此外应理解,在阅读了本发明讲授的内容之后,本领域技术人员可以对本发明作各种改动或修改,这些等价形式同样落于本申请所附权利要求书所限定的范围。

20.如图1所示,本实施例公开的一种温度传感器电路包括五部分,分别为偏置电流源、前端感温电路、二阶∑-δ模数转换器、动态元件匹配逻辑电路和校正调制器,其中,二阶∑-δ模数转换器、动态元件匹配逻辑电路和校正调制器均由同一外部振荡器驱动。

21.偏置电流源用于为前端感温电路提供大小为pi

bias

和i

bias

的偏置电流,其中,p表示偏置电流大小比值。

22.前端感温电路使用一对二极管接法的bjt(q1、q2),bjt接入偏置电流pi

bias

和i

bias

产生电压δv

be

和v

be

。由于δv

be

和v

be

分别具有与绝对温度成正比和随温度升高而降低的特性,故选用特定大小的增益倍率α使得(αδv

be

+v

be

)近似看成一个对温度不敏感的量,将这个量记为共模电压v

ref

,并且将αδv

be

记为输入电压v

ptat

。将共模电压v

ref

及输入电压v

ptat

同时输入∑-δ模数转换器,经由∑-δ模数转换器产生的位码流的占空比即为对应温度的数字读数。

23.因为在芯片制造过程中元件的实际尺寸与电学性质与预期值不符产生失配,所以

为了降低失配的影响,本实施例采用动态元件匹配的方式。本实施例采用动态元件匹配逻辑电路消除∑-δ模数转换器内元件工艺误差,并应用输出位码流控制技术消除互调失真。

24.结合图2,动态元件匹配逻辑电路会选择不同的元件组合接入电路之中,使得不同元件组合的等效误差远小于元件失配产生的误差。动态元件匹配逻辑电路本质上是一个受自身当前状态与外部输入控制的状态机。图2中以偏置电流源部分为例,动态元件匹配逻辑电路控制(p+1)个偏置电流源i

bias,0

,i

bias,1

,...,i

bias,p

分别与两个bjt相连并且保持bjt偏置电流大小之比约为1∶p。而φ1与φ2是驱动∑-δ模数转换器的两个频率相同相位相反的外部时钟信号(下同)。在φ1为高电平且φ2为低电平时,∑-δ模数转换器会用采样电容cs采集输入电压v

ptat

。在φ1为低电平且φ2为高电平时,∑-δ模数转换器会将采集到的电荷累积到∑-δ模数转换器的积分电容c

int

上,并将积分电容c

int

的电压与共模电压v

ref

相比较,积分电容c

int

的电压大于共模电压v

ref

则输出1,积分电容c

int

的电压小于等于共模电压v

ref

则输出0,比较器结果即为输出位码流信号bs。结合图3,在当前时钟周期内:若bs=0,动态元件匹配逻辑电路会在φ1的上升沿改变自身状态,并切换偏置电流源接入的组合;若bs=1,动态元件匹配逻辑电路则不会改变自身状态和偏置电流源接入的组合。

25.校正调制器可由一个自加器实现,满足校准精度需求,同样应用输出位码流控制技术消除互调失真。本实施例中,校正调制器本质上由一个数字累加器和一个数字比较器构成。数字累加器内部寄存器上的值会随着时钟周期不断自增,并在超过最大范围之后重置归零。数字比较器会将数字累加器内的数值与设定的校正值比较大小,并依据比较结果控制对应bjt管的v

be

作为前端感温电路的输出。在当前时钟周期内:若bs=1,校正调制器内的数字累加器会在φ1的上升沿进行自加操作,并依据数字比较器的比较结果控制前端感温电路输出的v

be

作为∑-δ模数转换器的输入;若bs=0,校正调制器内的数字累加器暂停自加,输出结果保持不变,并把当前的v

be

作为∑-δ模数转换器的输入。

26.本发明所采用的动态元件匹配技术元件通过取平均的方式消除了失配元件产生的一阶误差的影响。受位码流控制的动态元件匹配逻辑电路与校正调制器保证了输出位码流的频谱中不会存在相互抵消的波峰,从而避免了噪声影响低频谱段信号的质量。

技术特征:

1.一种温度传感器电路,包括:偏置电流源,用于为前端感温电路提供大小为pi

bias

和i

bias

的偏置电流;前端感温电路,接入偏置电流pi

bias

和i

bias

后产生电压δv

be

和v

be

,其中,电压δv

be

具有与绝对温度成正比的特性,电压v

be

具有随温度升高而降低的特性;∑-δ模数转换器,同时输入共模电压v

ref

及输入电压v

ptat

后,产生的位码流信号bs的占空比即为对应温度的数字读数,v

ref

=αδv

be

+v

be

,v

ptat

=αδv

be

,α为增益倍率,其特征在于,还包括:动态元件匹配逻辑电路,用于选择不同的元件组合接入温度传感器电路之中,使得不同元件组合的等效误差远小于元件失配产生的误差,从而消除∑-δ模数转换器内元件工艺误差;校正调制器,应用输出位码流控制技术消除互调失真。2.如权利要求1所述的一种温度传感器电路,其特征在于,所述∑-δ模数转换器由两个频率相同相位相反的外部时钟信号φ1与φ2驱动,在φ1为高电平且φ2为低电平时,∑-δ模数转换器会用采样电容c

s

采集输入电压v

ptat

。在φ1为低电平且φ2为高电平时,∑-δ模数转换器会将采集到的电荷累积到∑-δ模数转换器的积分电容c

int

上,并将积分电容c

int

的电压与共模电压v

ref

相比较,积分电容c

int

的电压大于共模电压v

ref

则输出1,积分电容c

int

的电压小于等于共模电压v

ref

则输出0,比较器结果即为输出位码流信号bs,则:所述动态元件匹配逻辑电路控制(p+1)个偏置电流源i

bias,0

,i

bias,1

,...,i

bias,p

分别与所述前端感温电路相连,并且保持所述前端感温电路的偏置电流大小之比为1∶p;在当前时钟周期内:若bs=0,动态元件匹配逻辑电路在φ1的上升沿改变自身状态,并切换偏置电流源接入的组合;若bs=1,动态元件匹配逻辑电路则不会改变自身状态和偏置电流源接入的组合。3.如权利要求1所述的一种温度传感器电路,其特征在于,所述∑-δ模数转换器由两个频率相同相位相反的外部时钟信号φ1与φ2驱动,在φ1为高电平且φ2为低电平时,∑-δ模数转换器会用采样电容c

s

采集输入电压v

ptat

。在φ1为低电平且φ2为高电平时,∑-δ模数转换器会将采集到的电荷累积到∑-δ模数转换器的积分电容c

int

上,并将积分电容c

int

的电压与共模电压v

ref

相比较,积分电容c

int

的电压大于共模电压v

ref

则输出1,积分电容c

int

的电压小于等于共模电压v

ref

则输出0,比较器结果即为输出位码流信号bs,则:所述校正调制器由一个数字累加器和一个数字比较器构成,其中,数字累加器内部寄存器上的值随着时钟周期不断自增,并在超过最大范围之后重置归零;数字比较器将数字累加器内的数值与设定的校正值比较大小,并依据比较结果控制所述前端感温电路中对应bjt管的v

be

作为前端感温电路的输出,其中,前端感温电路使用一对二极管接法的bjt:在当前时钟周期内:若bs=1,校正调制器内的数字累加器在φ1的上升沿进行自加操作,并依据数字比较器的比较结果控制前端感温电路输出的v

be

作为∑-δ模数转换器的输入;若bs=0,校正调制器内的数字累加器暂停自加,输出结果保持不变,并把当前的v

be

作为∑-δ模数转换器的输入。

技术总结

本发明公开了一种温度传感器电路,包括:偏置电流源;前端感温电路;Σ-Δ模数转换器,其特征在于,还包括:动态元件匹配逻辑电路,用于消除Σ-Δ模数转换器内元件工艺误差;校正调制器,应用输出位码流控制技术消除互调失真。本发明提出基于CMOS工艺的高精度、高分辨率温度传感器集成电路解决方案,通过动态元件匹配、校正与位码流控制等技术消除因元件失配和互调失真等现象产生的误差,显著提升温度检测精度和分辨率。测精度和分辨率。测精度和分辨率。

技术研发人员:吕宏鸣 周志宁

受保护的技术使用者:上海科技大学

技术研发日:2022.09.02

技术公布日:2022/12/9

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1