半导体管芯裂纹检测器的制作方法

本公开涉及一种用于检测半导体管芯的结构缺陷的组件。

背景技术:

1、用于晶粒(dice)的晶片分离工艺是一个敏感的制造步骤(特别是对于低k和超低k技术)。为了确保这一工艺,可以使用所谓的裂纹检测器来检测与晶粒密封环中的碎裂和裂纹相关的故障(在“生产线后端”,beol,制造阶段)。

2、参照图1,管芯10以顶部平面图示出,并且包括裂纹传感器或检测器1。在已知技术的一个示例性实施例中,裂纹传感器1由几个元件形成:

3、导线2(具有电阻),布置在管芯10的密封环区域4中或者布置在密封环4和切割槽6之间;

4、检测器单元8,布置在管芯10的i/o环7中;以及

5、测试逻辑(例如,测试电路)9,嵌入在管芯10的芯部5中,被配置为使用检测器单元8来测试电阻传感器1。

6、导线2基本上是在两个电节点e1、e2之间延伸的具有一定电阻的连续导电材料条。导线2可以由一个或两个子线形成;在两个子线的情况下,一个子线放置在密封环区域4和i/o环7之间,也称为“内部传感器”,另一个子线放置在密封环区域4内,也称为“外部传感器”。每个子线都实现为过孔链(见图2)。这种具有两个子线或子传感器的解决方案允许检测除裂纹之外的分层缺陷。考虑到外部传感器,为了不“破坏”密封环区域4的金属连续性,可以将n阱带插入传感器端子中。

7、在通过检测单元8的ews(电晶片分选”)和ft(“最终测试”)期间测量传感器1的电连续性,允许检测并筛选出密封环的具有裂纹的部分。将特定的仓(bin)和sbl影响到该测试将允许正确监测缺陷率,并在需要时采取适当的措施。

8、传感器1的使用提高了芯片产品的鲁棒性,能够在“时间零点”检测beol中的裂纹,这防止了在客户应用中(当热机械或湿度约束起主要作用时)成为故障部件的薄弱部件的交付。传感器1的使用对测试时间的影响可以忽略不计(它需要测试一个简单的电阻器),并且不会对rf产品的功能造成干扰。

9、如预期的,图2示出了根据已知技术的裂纹传感器1(的一部分)的实施例的横向剖视图。图2的裂纹传感器1可用于具有多于两个金属层的互连结构的芯片。基板导电段11布置在基板12中。基板导电段11的第一部分连接到m1金属化层中的第一导电段14。基板导电段11的第二部分连接到m1金属化层中的第二导电段15。第一导电段14通过多个层间连接件而连接到上金属化层中的多个另外的导电段16。类似地,第二导电段15通过多个相应的层间连接件而连接到上金属化层中的多个另外的导电段18。

10、层间连接件可以包括触点和/或插头/过孔。

11、图1和图2的结构可用于检测当管芯10与晶片分离(单独化)时可能形成的裂纹。如上所述,裂纹检测器是由具有两个电节点的金属线组成的电阻传感器。这种金属线被放置在靠近密封环的管芯周围。测量这根线的连续性可以检测裂纹。

12、为了测试管芯10的裂纹,在电节点e1、e2上施加电压。在向两个节点e1、e2施加电压期间,电流流动。如果电阻线2上没有(或几乎没有)电压降,则传感器是完整的,并且裂纹没有中断或断裂。如果在电阻线2上存在一些电压降,传感器可能部分断开,并且如果在电阻线2上存在完全或几乎完全的电压降,传感器可能被切断或严重损坏。

13、这种解决方案有一些限制。具体地,由于工艺变化,可能存在传感器电阻的大分散,因此难以设置可靠的限值;此外,测试需要很长时间才能完成(大约10毫秒);此外,测量需要片外布置。

14、作为替代解决方案,也可以进行数字测试。

15、图3显示了用于执行数字测试的电路设计。

16、在该示例中,将数字信号datain设置为裂纹传感器1的电节点e1的输入。信号datain从数字值“0”变为数字值“1”。提供输入缓冲级20以接收信号datain,整流信号datain,并通过节点e1正确地驱动裂纹传感器1。提供耦接到裂纹传感器1的输出电节点e2的输出缓冲级21,以接收通过裂纹传感器1传播的信号,整流该信号并在输出端提供数字信号sout。

17、在一个可行的实施方式中,信号datain由测试逻辑9产生,并且输入缓冲器级20是检测单元8的一部分,类似地,信号sout由测试逻辑9接收,并且输出缓冲器级21是检测单元8的一部分。

18、在不存在裂纹的情况下(即,电阻线2没有被裂纹中断),信号sout对应于信号datain,并且以一定的时间延迟被接收。相反,在电阻线2中断的情况下,没有接收到信号sout,或者信号sout与信号datain显著不同。因此,沿着电阻线2的裂纹或其他问题显露出来。

19、使用图3的解决方案会出现一些限制。

20、具体是,用户经历了传感器rc常数的大分散(由于制造工艺的变化),因此很难设置可靠的限值;此外,很难测量精确的过渡时间(因为采样窗口应该是固定的)。此外,这种测量需要片外布置。

技术实现思路

1、提供了一种用于检测半导体管芯中的结构缺陷的组件。

技术特征:

1.一种用于检测半导体管芯中结构缺陷的存在的组件,所述组件包括:

2.根据权利要求1所述的组件,其中所述多个电阻路径中的每个电阻路径包括环路,所述环路由从所述相应第一端延伸到中间连接点的第一子路径和从所述中间连接点延伸到所述相应第二端的第二子路径形成。

3.根据权利要求1所述的组件,其中所述半导体管芯包括:

4.根据权利要求1所述的组件,其中所述多个信号产生级的每个信号产生结构级包括:

5.根据权利要求4所述的组件,其中所述微控制器被配置为通过执行所述多个电阻路径的电阻值的差分测量来测试所述电阻路径的电特性。

6.根据权利要求5所述的组件,其中如果所述差分测量的结果在预定义的期望值范围之外,则所述结构缺陷被检测到。

7.根据权利要求1所述的组件,其中每个信号产生级包括:

8.根据权利要求1所述的组件,其中每个信号产生级包括:

9.根据权利要求7所述的组件,其中所述测试信号是具有振荡频率的振荡信号,所述微控制器被配置为通过对被测的所述电阻路径的测试信号的振荡频率进行分析来测试所述多个电阻路径的电特性。

10.根据权利要求9所述的组件,其中所述微控制器被配置为:

11.根据权利要求9所述的组件,其中所述微控制器被配置成:

12.根据权利要求11所述的组件,其中如果所述差分测量的结果在预定义的期望值范围之外,则所述结构缺陷被检测到。

13.根据权利要求9所述的组件,其中所述微控制器被配置为:

14.根据权利要求8所述的组件,其中所述微控制器被配置为通过以下方式测试一个电阻路径:

15.一种用于检测半导体管芯中结构缺陷的存在的方法,所述方法包括:

16.根据权利要求15所述的方法,其中所述多个电阻路径中的每个电阻路径包括环路,所述环路由从相应第一端延伸至中间连接点的第一子路径和从所述中间连接点延伸至相应第二端的第二子路径形成。

17.根据权利要求15所述的方法,其中所述半导体管芯包括环绕所述半导体管芯的内部部分的密封环,所述多个电阻路径中的每个电阻路径在所述密封环和所述半导体管芯的周边之间延伸,并且相应第一端和第二端穿过所述密封环朝向所述内部部分延伸。

18.根据权利要求15所述的方法,包括:

19.根据权利要求18所述的方法,包括:

20.根据权利要求19所述的方法,包括:

技术总结

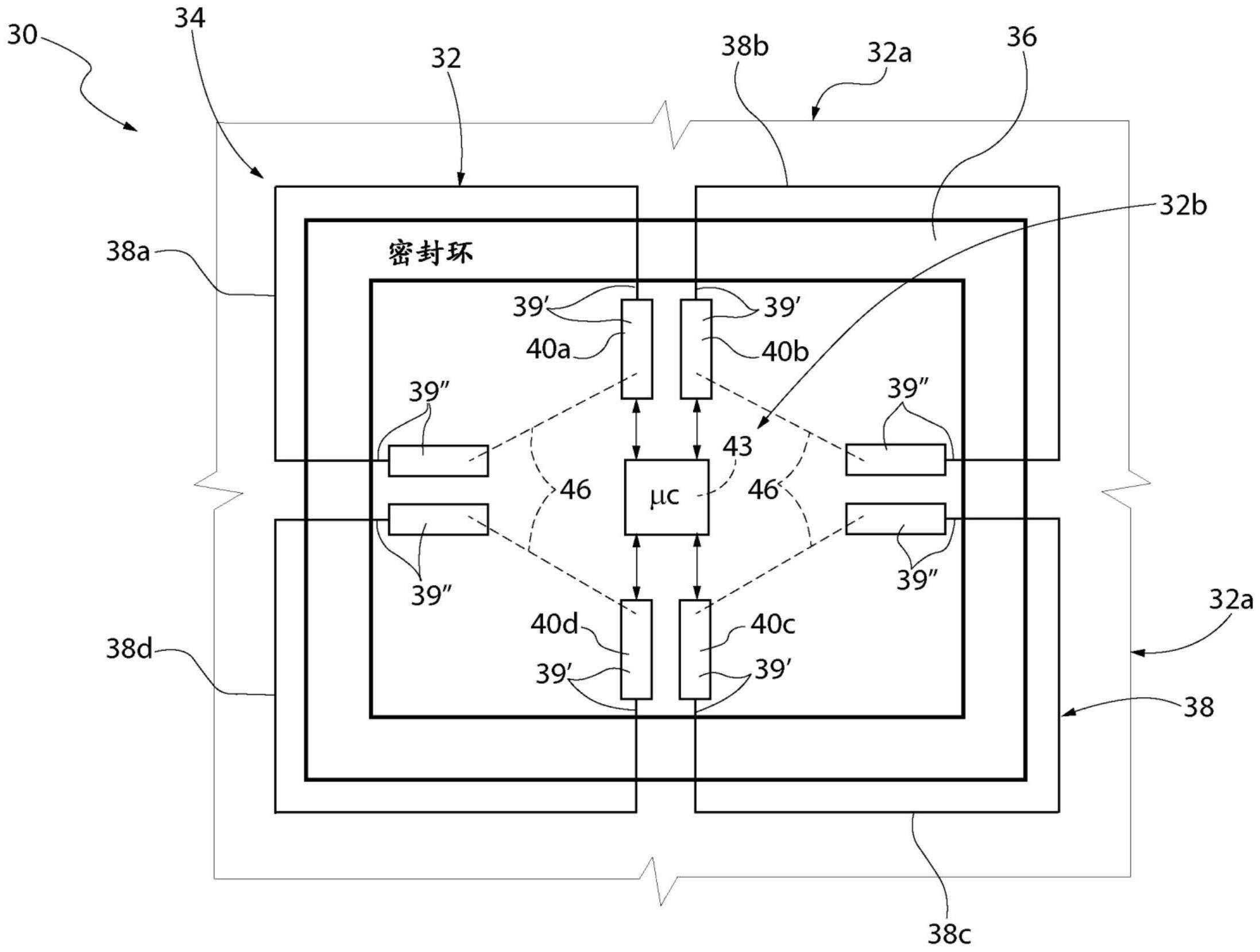

本公开涉及半导体管芯裂纹检测器。提供了一种用于检测半导体管芯中的结构缺陷的组件。该组件包括缺陷检测传感器和微控制器。缺陷检测传感器包括半导体管芯中导电材料的多个电阻路径,每个电阻路径具有第一端和第二端,并且靠近半导体管芯的周边延伸。缺陷检测传感器包括多个信号产生结构,每个信号产生结构耦接到相应的电阻路径,并被配置为向电阻路径提供测试信号。微控制器被配置成控制信号产生结构以生成测试信号,获取每个电阻路径中的测试信号,通过对所获取的测试信号执行分析来测试电阻路径的电特性,并基于所获取的测试信号的分析结果来检测半导体管芯中结构缺陷的存在。

技术研发人员:M·贾科米尼,F·E·C·迪塞格尼,R·纳尔沃,P·K·赛尼,M·哈雷什巴·尼兰贾尼

受保护的技术使用者:意法半导体股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!