电压监测电路和半导体存储器的制作方法

本公开涉及集成电路,具体而言,涉及一种电压监测电路和半导体存储器。

背景技术:

1、相关技术中,为了监测单个die(晶粒或芯片)中包括的全部参考电源和全部内部电源,需要将每一参考电源和每一内部电源依次选择输出至输出端,以供外部监测。由于任一参考电源或任一内部电源在传输至输出端的过程中,除正在传输中的电源之外的其它参考电源或其它内部电源可能会对输出端(传输中)的电源造成干扰,一旦干扰到输出端的电源,可能最终导致相关的低压差线性稳压器(low drop output,ldo)等电源调节电路输出错误的电源等级,因此,如何减小其它参考电源或其它内部电源对输出端的电源的干扰是亟待解决的问题。

2、需要说明的是,在上述背景技术部分公开的信息仅用于加强对本公开的背景的理解,因此可以包括不构成对本领域普通技术人员已知的现有技术的信息。

技术实现思路

1、本公开的目的在于提供一种电压监测电路和半导体存储器,能够在一定程度上减小或降低其它待监测电压源对待监测电压源的干扰。

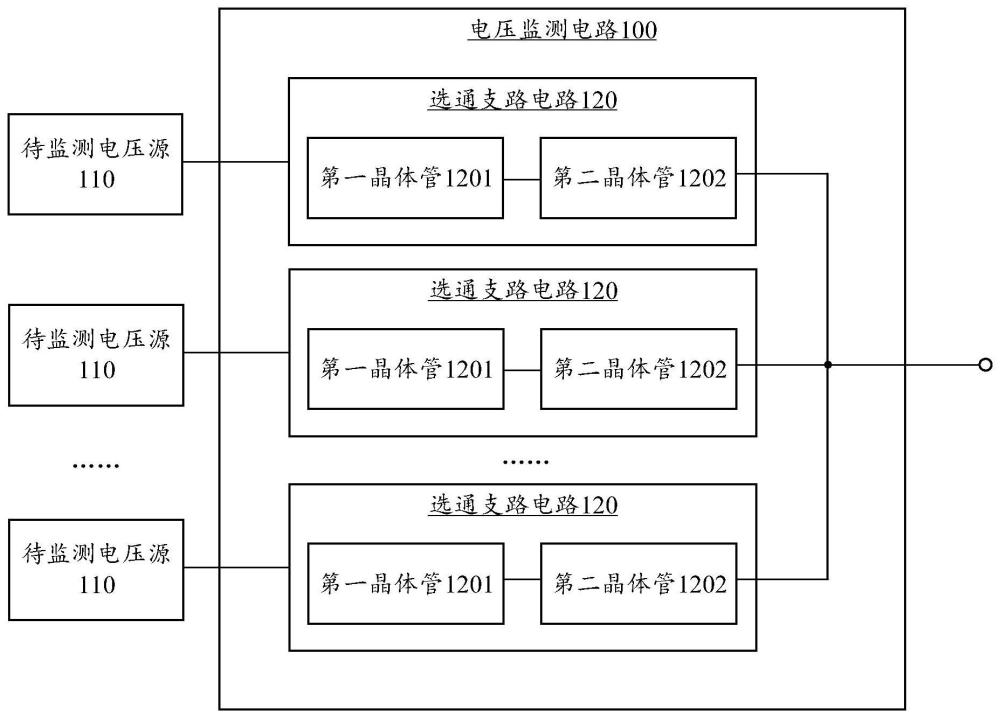

2、本公开实施例提供了一种电压监测电路,包括:

3、与多个待监测电压源一一对应的多个选通支路电路,各所述待监测电压源的电压不同;

4、各所述选通支路电路包括第一晶体管和第二晶体管;所述第一晶体管的控制端和所述第二晶体管的控制端用于接收控制信号,以同时导通或同时截止所述第一晶体管和所述第二晶体管;所述第一晶体管的第一极耦接所述选通支路电路对应的待监测电压源,所述第一晶体管的第二极与所述第二晶体管的第二极耦接,所述第二晶体管的第一极与所述电压监测电路的输出端耦接;

5、其中,所述第一晶体管和所述第二晶体管均为非对称晶体管,且所述第一晶体管和所述第二晶体管均处于截止状态时,所述第一晶体管和所述第二晶体管在所述第一极上的电压值大于所述第二极上的电压值δv时的第一漏电流小于所述第一晶体管和所述第二晶体管在所述第二极上的电压值大于所述第一极上的电压值δv时的第二漏电流。

6、本公开实施例提供了另一种电压监测电路,包括:

7、多个待监测电压源,各所述待监测电压源的电压不同;

8、与所述多个待监测电压源一一对应的多个选通支路电路;各所述选通支路电路包括第一晶体管和第二晶体管;所述第一晶体管的控制端和所述第二晶体管的控制端用于接收控制信号,以同时导通或同时截止所述第一晶体管和所述第二晶体管;所述第一晶体管的第一极耦接所述选通支路电路对应的待监测电压源,所述第一晶体管的第二极与所述第二晶体管的第二极耦接;

9、与所述多个选通支路电路一一对应的转换支路电路;各所述转换支路电路用于将对应的所述选通支路电路中的所述第一晶体管和所述第二晶体管的耦接模式从并联模式转换为串联模式,或者从串联模式转换为并联模式;

10、在所述串联模式下,所述第二晶体管的第一极耦接所述电压监测电路的输出端;

11、在所述并联模式下,所述第一晶体管的第一极耦接所述第二晶体管的第一极;所述第一晶体管的第二极和所述第二晶体管的第二极均耦接所述电压监测电路的输出端;

12、其中,所述第一晶体管和所述第二晶体管均为非对称晶体管,且所述第一晶体管和所述第二晶体管均处于截止状态时,所述第一晶体管和所述第二晶体管在所述第一极上的电压值大于所述第二极上的电压值δv时的第一漏电流小于所述第一晶体管和所述第二晶体管在所述第二极上的电压值大于所述第一极上的电压值δv时的第二漏电流。

13、本公开实施例提供了一种半导体存储器,包括:电源电路,用于产生多个待监测电压源,各所述待监测电压源的电压不同;如本公开任一实施例提供的电压监测电路。

14、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本公开。

技术特征:

1.一种电压监测电路,其特征在于,包括:

2.如权利要求1所述的电压监测电路,其特征在于,所述第一晶体管和所述第二晶体管均为nmos管;

3.如权利要求1所述的电压监测电路,其特征在于,所述第一晶体管和所述第二晶体管均为pmos管;

4.如权利要求1至3任一项所述的电压监测电路,其特征在于,还包括:

5.如权利要求4所述的电压监测电路,其特征在于,所述输出信号保护电路包括第三晶体管;

6.如权利要求5所述的电压监测电路,其特征在于,所述第三晶体管为对称晶体管。

7.一种电压监测电路,其特征在于,包括:

8.如权利要求7所述的电压监测电路,其特征在于,各所述转换支路电路包括第一切换开关,用于在所述串联模式下,断开所述第一晶体管的第一极与所述第二晶体管的第一极之间的耦接,使得所述第一晶体管和所述第二晶体管串联耦接;在所述并联模式下,闭合所述第一晶体管的第一极与所述第二晶体管的第一极之间的耦接,使得所述第一晶体管和所述第二晶体管并联耦接。

9.如权利要求8所述的电压监测电路,其特征在于,各所述转换支路电路还包括第二切换开关,用于在所述串联模式下,将所述信号监测电路的输出端耦接至所述第二晶体管的第一极;在所述并联模式下,将所述信号监测电路的输出端耦接至所述第一晶体管的第二极和所述第二晶体管的第二极。

10.如权利要求9所述的电压监测电路,其特征在于,所述第二切换开关为单刀双掷开关。

11.如权利要求7所述的电压监测电路,其特征在于,所述第一晶体管和所述第二晶体管均为nmos管;

12.如权利要求7所述的电压监测电路,其特征在于,所述第一晶体管和所述第二晶体管均为pmos管;

13.一种半导体存储器,其特征在于,包括:

技术总结

本公开提供一种电压监测电路,属于集成电路技术领域。该电压监测电路包括:与多个待监测电压源一一对应的多个选通支路电路,各待监测电压源的电压不同;各选通支路电路包括第一晶体管和第二晶体管;第一晶体管的控制端和第二晶体管的控制端用于接收控制信号,以同时导通或同时截止第一晶体管和第二晶体管;第一晶体管的第一极耦接选通支路电路对应的待监测电压源,第一晶体管的第二极与第二晶体管的第二极耦接,第二晶体管的第一极与电压监测电路的输出端耦接。通过本公开实施例提供的方案,能够减小其它待监测电源对输出端的电源的干扰。

技术研发人员:陈思嘉

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/7/15

- 还没有人留言评论。精彩留言会获得点赞!