一种高阶芯片的失效分析方法与流程

本发明涉及半导体器件分析,尤其涉及一种高阶芯片的失效分析方法。

背景技术:

1、半导体集成电路芯片需要经过非常多且复杂的工艺,将多晶硅、氧化硅、金属互联层等一层层地堆叠,进而形成器件,并将各个器件连接在一起,实现复杂的功能。

2、在半导体集成电路芯片设计及加工过程中,失效分析等工作显得十分重要。失效分析使得芯片设计者可对芯片作针对性的测试,以便更快更准确的验证设计方案。在高阶制程芯片的传统失效分析中,应用常规的电性分析手段仅能测试到芯片的晶粒级别,若需要对芯片内部的金属层等结构进行测试,需要进行多个实验步骤,耗时长。

3、目前,现有技术中没有合适的方法对芯片进行测试,以实现对多晶层的电性测试与失效分析。因此,如何实现高阶制程芯片的晶体管级别失效分析是目前尚待解决的问题。

技术实现思路

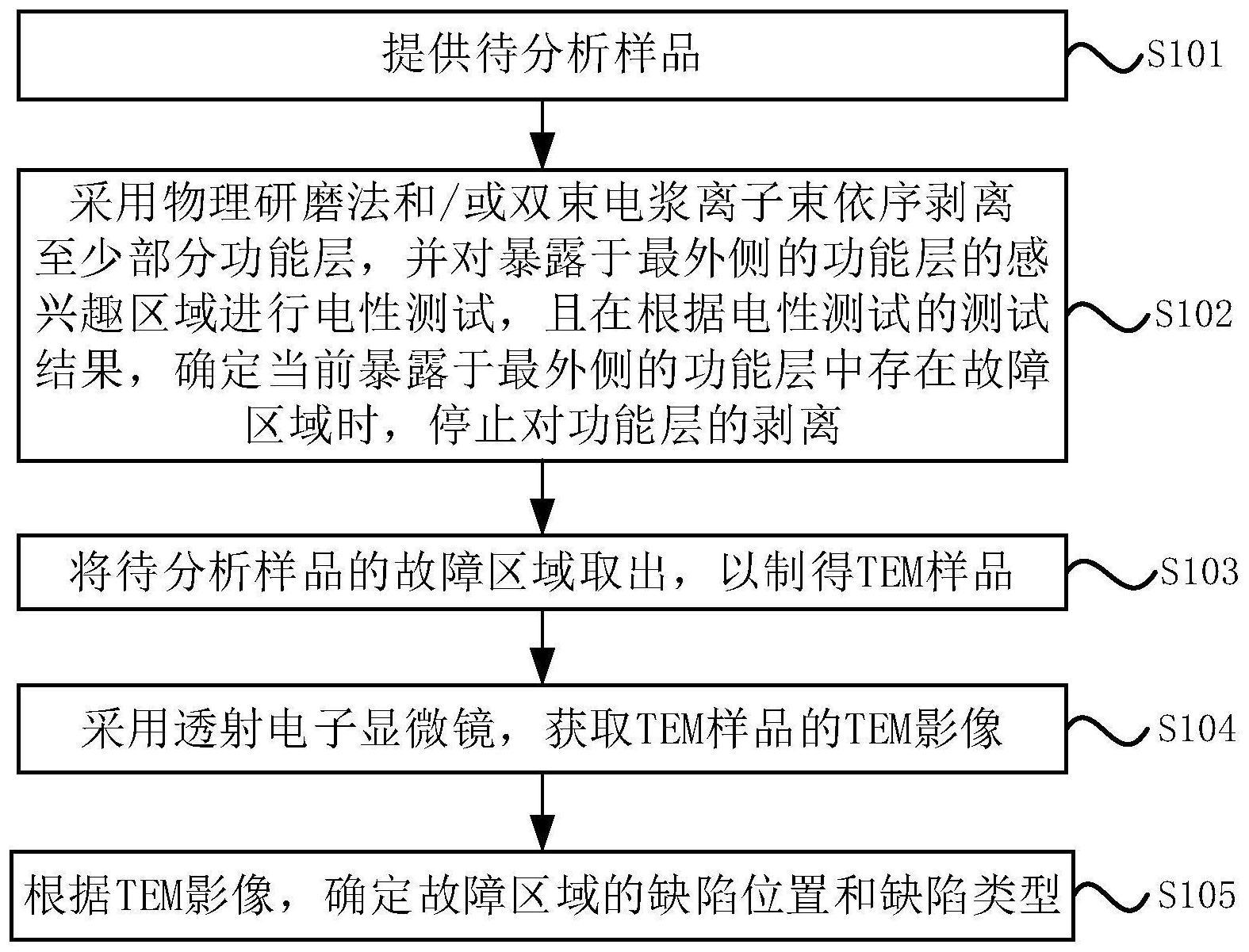

1、本发明提供一种高阶芯片的失效分析方法,以实现高阶芯片的晶体管级别的失效分析,提高分析质量和分析速率。

2、本发明提供了一种高阶芯片的失效分析方法,所述高阶芯片包括层叠设置的多层功能层和覆盖各所述功能层的封装层,其特征在于,包括:

3、提供待分析样品;所述待分析样品为已去除所述封装层的所述高阶芯片;所述待分析样品包括待分析的感兴趣区域;

4、采用物理研磨法和/或双束电浆离子束依序剥离至少部分所述功能层,并对暴露于最外侧的所述功能层的所述感兴趣区域进行电性测试,且在根据所述电性测试的测试结果,确定当前暴露于最外侧的所述功能层中存在故障区域时,停止对所述功能层的剥离;

5、将所述待分析样品的所述故障区域取出,以制得tem样品;

6、采用透射电子显微镜,获取所述tem样品的tem影像;

7、根据所述tem影像,确定所述故障区域的缺陷位置和缺陷类型。

8、可选的,在提供待分析样品之前,还包括:

9、提供待分析的所述高阶芯片;

10、去除所述高阶芯片的封装层,以制得所述待分析样品;

11、对所述待分析样品进行热成像分析,并根据所述热成像分析的结果,确定所述待分析样品中的感兴趣区域。

12、可选的,对所述待分析样品进行热成像分析,并根据所述热成像分析的结果,确定所述待分析样品中的感兴趣区域,包括:

13、采用激光束扫描所述待分析样品的表面,并获取热成像影像;

14、根据所述热成像影像,确定所述待分析样品中的感兴趣区域。

15、可选的,所述高阶芯片还包括位于相邻两层所述功能层之间的绝缘层;

16、采用物理研磨法和/或双束电浆离子束依序剥离至少部分所述功能层,包括:

17、在与暴露于最外侧的所述功能层最邻近的所述绝缘层的厚度小于或等于50nm时,采用所述双束电浆离子束剥离所述功能层;

18、在与暴露于最外侧的所述功能层最邻近的所述绝缘层的厚度大于50nm时,采用物理研磨法剥离所述功能层。

19、可选的,对暴露于最外侧的所述功能层的所述感兴趣区域进行电性测试,包括:

20、采用电子束照射暴露于最外侧的所述功能层的所述感兴趣区域;

21、在纳米探测器与暴露于最外侧的所述功能层的所述感兴趣区域内结构接触时,获取所述纳米探测器反馈的探测信号作为电性测试的测试结果;所述纳米探测器包括至少一个纳米探针。

22、可选的,将所述待分析样品的所述故障区域取出,以制得tem样品,包括:

23、将所述待分析样品放置于聚焦离子束设备中,在所述功能层的所述故障区域处形成第一导电层;

24、切割所述待分析样品,以将形成有所述第一导电层的所述功能层取出并作为二次分析样品;

25、对所述二次分析样品背离所述第一导电层的一侧进行减薄至预设厚度;

26、对减薄后的所述二次分析样品进行tem分析,并根据tem分析结果确定缺陷区域;

27、在减薄后的所述二次分析样品的缺陷区域形成第二导电层;

28、切割所述二次分析样品,以将形成所述第二导电层的缺陷区域取出并作为tem样品。

29、可选的,在切割所述待分析样品,以将形成有所述第一导电层的所述功能层取出并作为二次分析样品之前,还包括:

30、对形成所述第一导电层的所述待分析样品进行tem分析,并根据tem分析结果确定所述第一导电层是否形成于所述故障区域。

31、可选的,在切割所述二次分析样品,以将形成所述缺陷区域取出并作为tem样品之前,还包括:

32、对形成所述第二导电层的所述二次分析样品进行tem分析,并根据tem分析结果确定所述第二导电层是否形成于所述缺陷区域。

33、可选的,根据所述tem影像,确定所述故障区域的缺陷位置和缺陷类型,包括:

34、将所述tem影像与标准影像进行比对,并获取比对结果;

35、根据所述比对结果,确定所述故障区域的缺陷位置和缺陷类型。

36、本发明提供的技术方案,采用物理研磨法和/或双束电浆离子束依序剥离待分析样品中的至少部分功能层,可以提高剥层速率,缩短分析时间,提高分析效率,之后对暴露于最外侧的功能层的感兴趣区域进行电性测试,且在根据电性测试的测试结果,确定当前暴露于最外侧的功能层中存在故障区域时,停止对功能层的剥离,并将待分析样品的故障区域取出,以制得tem样品,获取并根据tem样品的tem影像,确定故障区域的缺陷位置和缺陷类型,如此,可以实现高阶芯片的晶体管级别的失效分析,提高分析质量和分析速率。

技术特征:

1.一种高阶芯片的失效分析方法,所述高阶芯片包括层叠设置的多层功能层和覆盖各所述功能层的封装层,其特征在于,包括:

2.根据权利要求1所述的高阶芯片的失效分析方法,其特征在于,在提供待分析样品之前,还包括:

3.根据权利要求2所述的高阶芯片的失效分析方法,其特征在于,对所述待分析样品进行热成像分析,并根据所述热成像分析的结果,确定所述待分析样品中的感兴趣区域,包括:

4.根据权利要求1所述的高阶芯片的失效分析方法,其特征在于,所述高阶芯片还包括位于相邻两层所述功能层之间的绝缘层;

5.根据权利要求1所述的高阶芯片的失效分析方法,其特征在于,对暴露于最外侧的所述功能层的所述感兴趣区域进行电性测试,包括:

6.根据权利要求1所述的高阶芯片的失效分析方法,其特征在于,将所述待分析样品的所述故障区域取出,以制得tem样品,包括:

7.根据权利要求6所述的高阶芯片的失效分析方法,其特征在于,在切割所述待分析样品,以将形成有所述第一导电层的所述功能层取出并作为二次分析样品之前,还包括:

8.根据权利要求6所述的高阶芯片的失效分析方法,其特征在于,在切割所述二次分析样品,以将形成所述缺陷区域取出并作为tem样品之前,还包括:

9.根据权利要求1所述的高阶芯片的失效分析方法,其特征在于,根据所述tem影像,确定所述故障区域的缺陷位置和缺陷类型,包括:

技术总结

本发明公开了一种高阶芯片的失效分析方法,该方法包括:提供待分析样品;待分析样品为已去除封装层的高阶芯片;待分析样品包括待分析的感兴趣区域;采用物理研磨法和/或双束电浆离子束依序剥离至少部分功能层,并对暴露于最外侧的功能层的感兴趣区域进行电性测试,且在根据电性测试的测试结果,确定当前暴露于最外侧的功能层中存在故障区域时,停止对功能层的剥离;将待分析样品的故障区域取出,以制得TEM样品;采用透射电子显微镜,获取TEM样品的TEM影像;根据TEM影像,确定故障区域的缺陷位置和缺陷类型。本发明的技术方案,可以实现高阶芯片的晶体管级别的失效分析,提高分析质量和分析速率。

技术研发人员:张林华,刘瑶,侯增,华佑南,李晓旻

受保护的技术使用者:胜科纳米(苏州)股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!