自动试验装置及其接口装置的制作方法

本发明涉及自动试验装置,特别是涉及测试头与dut的接口装置。

背景技术:

1、在存储器、cpu(central processing unit)等各种半导体器件的检査中使用自动试验装置(ate:automatic test equipment)。ate向试验对象的半导体器件(以下,称为被试验器件(dut))供给试验信号,测定dut对于试验信号的响应,判定dut的良好与否,或者确定不良部位。

2、图1是以往的ate10的框图。ate10具备测试器(也称为测试器主体)20、测试头30、接口装置40、处理器(handler)50。

3、测试器20集中地控制ate10。具体而言,测试器20执行测试程序,对测试头30、处理器50进行控制,收集测定结果。

4、测试头30具备产生向dut1应供给的试验信号、而且检测来自dut的信号(称为器件信号)的硬件。具体而言,测试头30具备引脚电子(pe)32、电源电路(未图示)等。pe32是包含驱动器及比较器(comparator)等的asic(application specific ic)。以往,pe32安装在称为pe板34的印制电路板上,收容于测试头30的内部。

5、接口装置40也称为hi-fix,对测试头30与dut1之间的电连接进行中继。接口装置40具备插座板42。在插座板42设有多个插座44,能够同时测定多个dut1。在进行晶圆(wafer)级试验的ate的情况下,取代插座板42而使用探针卡(probe card)。

6、通过处理器50向多个插座44载入多个dut1,向插座44压紧dut1。在试验结束后,处理器50将dut1卸载,根据需要,区分合格品与不合格品。

7、接口装置40具备将插座板42与测试头30连接的多个线缆46。pe32产生的试验信号经由线缆46向dut1传输,dut1产生的器件信号经由线缆46向pe32传输。

8、【在先技术文献】

9、【专利文献】

10、【专利文献1】日本特开2008-76308号公报

11、【专利文献2】国际公开wo2009-034641号公报

技术实现思路

1、【发明的概要】

2、【发明要解决的课题】

3、近年来,dram(dynamic random access memory)的高速化不断进展。在搭载于图形板的gddr(graphics double data rate)存储器中,在gddr6x标准下,通过nrz(nonreturn to zero)方式能达成21gbps的传输速度。

4、在下一代的gddr7中,采用pam4(pulse amplitude modulation 4),传输速度升高至40gbps。nrz方式也每年地高速化不断进展,在下一代中,高速化至28gbps左右。

5、当传输速度超过20gbps时,在沿用了以往的体系结构的存储器测试器中难以进行准确的测定。当前,能够准确地测定28gbps、40gbps的高速的存储器的ate还未市售。

6、本发明是在这样的状况下作出的发明,其例示性的目的之一在于提供一种能够将超过20gbps的高速器件高精度地进行试验的接口装置、及自动试验装置。

7、【用于解决课题的方案】

8、本发明的一个方案涉及设置在测试头与被试验器件(dut)之间的接口装置。接口装置具备将多个引脚电子ic(integrated circuit)进行模块化而成的前端(front end)模块。

9、需要说明的是,将以上的构成要素任意地组合的结构、以及将构成要素、表述在方法、装置等之间相互置换的结构,作为本发明的方案也有效。

10、【发明效果】

11、根据本发明的一个方案,能够对高速器件进行量产试验。

技术特征:

1.一种接口装置,其设置在测试头与被试验器件之间,其特征在于,

2.根据权利要求1所述的接口装置,其特征在于,

3.根据权利要求2所述的接口装置,其特征在于,

4.根据权利要求2或3所述的接口装置,其特征在于,

5.根据权利要求4所述的接口装置,其特征在于,

6.根据权利要求2或3所述的接口装置,其特征在于,

7.根据权利要求6所述的接口装置,其特征在于,

8.根据权利要求7所述的接口装置,其特征在于,

9.根据权利要求8所述的接口装置,其特征在于,

10.根据权利要求1~3中任一项所述的接口装置,其特征在于,

11.一种自动试验装置,其特征在于,具备:

技术总结

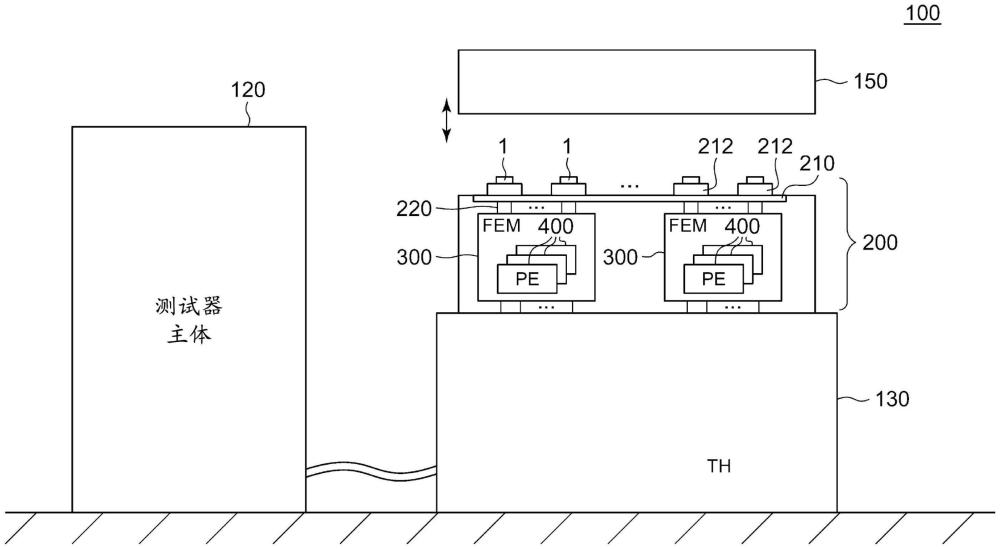

本发明提供一种能够将高速器件高精度地进行试验的接口装置。接口装置(200)设置在测试头(130)与DUT(1)之间。接口装置(200)具备将多个引脚电子IC(400)进行模块化而成的前端模块(300)。

技术研发人员:市川弘毅,须藤训,藤部亮

受保护的技术使用者:株式会社爱德万测试

技术研发日:

技术公布日:2024/1/25

- 还没有人留言评论。精彩留言会获得点赞!