一种参数化可重构FPGA数字波束形成装置的制作方法

本发明涉及雷达探测。

背景技术:

1、数字波束形成(dbf)使得阵列天线波束特性按照数字可编程的方式进行空间合成,是数字阵列雷达系统设计的一项关键技术。在数字相控阵雷达系统中,dbf属于数据密集型运算,由于其强实时性处理要求,工程上广泛将dbf功能部署于fpga。常见的fpga-dbf装置可配置软件参数包括:权系数、波束数目、加权类型等,在此基础上根据空域快拍数据率与fpga处理时钟频率之间的关系设计流水结构,可以减少dsp48e乘法器的消耗。但是对于不同型号的数字阵列雷达,天线阵元数目、空域快拍数据位宽、权系数数据位宽、空域快拍数据速率、fpga处理时钟频率等硬件参数不同,传统软件参数配置方式的fpga-dbf装置依然需要重新设计,无法在不同数字阵列雷达型号之间实现dbf处理器的快速重构。

2、专利cn114089282a公开了一种基于软件化雷达的数字波束处理方法,该方法支持使用软件直接修改fpga内部存储的权值信息,以增加dbf处理器的可扩展性,但是无法在天线阵元数目、空域快拍位宽、权系数数据位宽、空域快拍数据率、fpga处理时钟频率等硬件参数变化时实现波束形成器的自主重构。

技术实现思路

1、为解决fpga数字波束形成器在不同型号数字阵列雷达工程实现时的快速重构问题,本发明提出了一种参数化可重构fpga数字波束形成装置,通过合理配置参数,所重构的波束形成器能够在空域快拍数据率与fpga处理时钟不匹配时,基于流水复用大幅减少复数乘法器的资源消耗,适于数字阵列雷达dbf系统设计,支持在不同型号数字阵列雷达工程实现时的快速重构。

2、为实现上述技术目的,本发明的技术解决方案为:

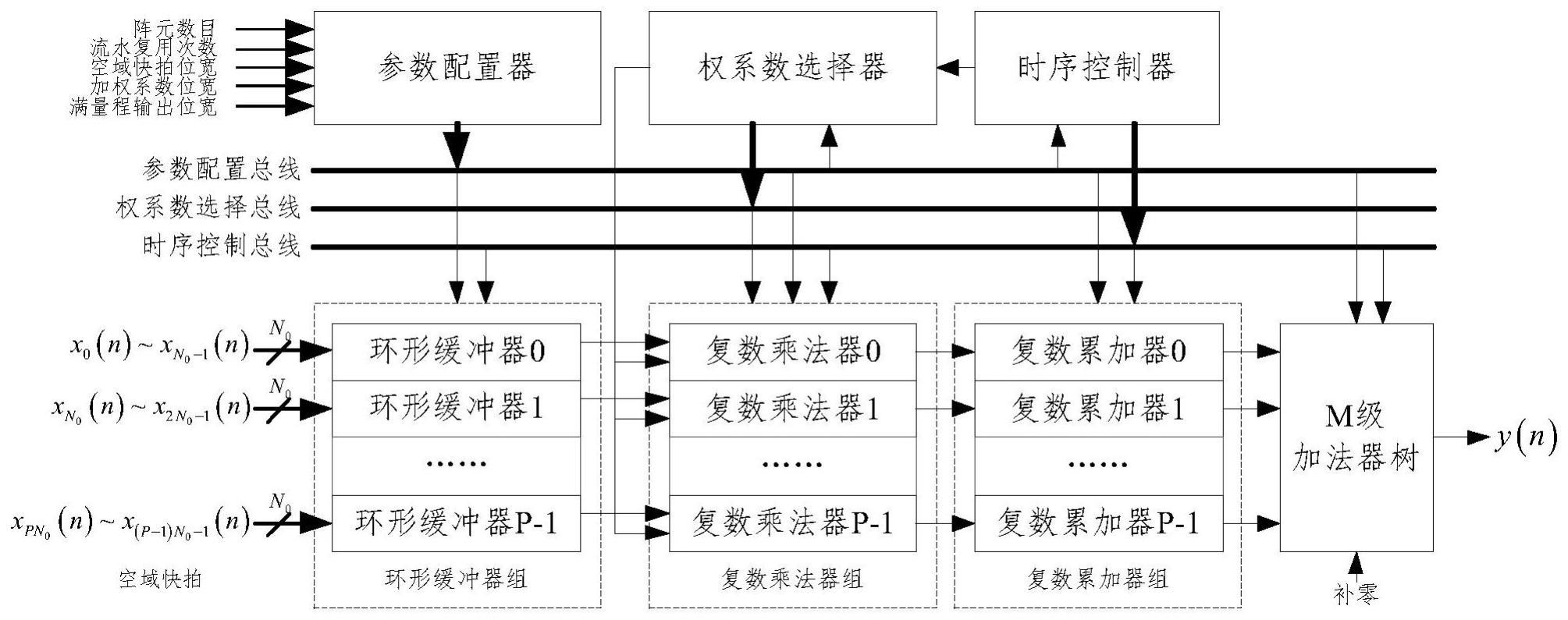

3、一种参数化可重构fpga数字波束形成装置,包括参数配置器、权系数选择器、时序控制器、环形缓冲器组、复数乘法器组、复数累加器组、加法器树,其中参数配置器通过参数配置总线将配置参数送至权系数选择器、时序控制器、环形缓冲器组、复数乘法器组、复数累加器组以及加法器树,实现波束形成装置的fpga运算重构;环形缓冲器组接收并行多通道空域快拍数据,并根据配置参数将多通道并行空域快拍数据串行流出至复数乘法器组;在串行空域快拍数据流入复数乘法器组的同时,权系数选择器在时序控制器控制下按特定时序将权系数送至复数乘法器组,在复数乘法器组内实现多通道并行流水复用加权处理;复数累加器组接收复数乘法器组输出的多通道加权空域数据,对各通道串行加权空域数据流进行累加得到多通道一级dbf数据;加法器树接收多通道一级dbf数据,并以树状结构对其进行合成得到最终的波束数字形成结果;时序控制器通过时序控制总线为整个系统提供精准控制时序。

4、优选地,所述参数配置器配置参数包括阵元数目n、流水复用次数n0、空域快拍数据位宽biq、加权系数位宽bcoe、满量程输出位宽bfull。

5、优选地,流水复用次数n0、满量程输出位宽bfull计算公式分别为:

6、

7、

8、式中,ffpga_clk为fpga处理时钟频率,fiq为空域快拍数据率,为向下取整运算,为向上取整运算。

9、优选地,所述环形缓冲器组中单个环形缓冲器输入端口数目与流水复用次数相同,输出端口数目为1,存储深度与流水复用次数相同。

10、优选地,环形缓冲器、复数乘法器、复数累加器总数目p为:

11、

12、复数累加器组中单个复数累加器的累加数据数目与流水复用次数相同。

13、优选地,加法器树层级m计算公式为:

14、

15、加法器树输入数据补零数d计算公式为:

16、

17、加法器树第m层加法器数目计算公式为:

18、nm=p/2m+1,m=0,1,...,m-1 (6);

19、加法器树第m层输出数据计算公式为:

20、am(i-p/2m)=am-1(i-p/2m)+am-1(i-p/2m+1),i=2p-p/2m~2p-p/2m+1-1 (7);

21、式中,a-1(i),i=0,1,...,p-1表示加法器树第0层的输入数据。

22、本发明与现有技术相比,其显著优点为:

23、(1)在不同型号数字阵列雷达天线阵元数目、空域快拍位宽、权系数数据位宽、空域快拍数据率、fpga处理时钟频率等硬件参数变化时,支持dbf处理器的快速重构;

24、(2)通过合理配置参数,所重构的波束形成器能够在空域快拍数据率与fpga处理时钟不匹配时,通过流水复用大幅减少复数乘法器的资源消耗。

25、下面结合附图对本发明做进一步详细的描述。

技术特征:

1.一种参数化可重构fpga数字波束形成装置,其特征在于:包括参数配置器、权系数选择器、时序控制器、环形缓冲器组、复数乘法器组、复数累加器组、加法器树,其中参数配置器通过参数配置总线将配置参数送至权系数选择器、时序控制器、环形缓冲器组、复数乘法器组、复数累加器组以及加法器树,实现波束形成装置的fpga运算重构;环形缓冲器组接收并行多通道空域快拍数据,并根据配置参数将多通道并行空域快拍数据串行流出至复数乘法器组;在串行空域快拍数据流入复数乘法器组的同时,权系数选择器在时序控制器控制下按特定时序将权系数送至复数乘法器组,在复数乘法器组内实现多通道并行流水复用加权处理;复数累加器组接收复数乘法器组输出的多通道加权空域数据,对各通道串行加权空域数据流进行累加得到多通道一级dbf数据;加法器树接收多通道一级dbf数据,并以树状结构对其进行合成得到最终的波束数字形成结果;时序控制器通过时序控制总线为整个系统提供精准控制时序。

2.根据权利要求1所述的一种参数化可重构fpga数字波束形成装置,其特征在于:所述参数配置器配置参数包括阵元数目n、流水复用次数n0、空域快拍数据位宽biq、加权系数位宽bcoe、满量程输出位宽bfull。

3.根据权利要求2所述的参数化可重构fpga数字波束形成装置,其特征在于:流水复用次数n0、满量程输出位宽bfull计算公式分别为:

4.根据权利要求2或权利要求3所述的参数化可重构fpga数字波束形成装置,其特征在于:所述环形缓冲器组中单个环形缓冲器输入端口数目与流水复用次数相同,输出端口数目为1,存储深度与流水复用次数相同。

5.根据权利要求2或权利要求3所述的参数化可重构fpga数字波束形成装置,其特征在于:环形缓冲器、复数乘法器、复数累加器总数目p为:

6.根据权利要求1所述的参数化可重构fpga数字波束形成装置,其特征在于:复数累加器组中单个复数累加器的累加数据数目与流水复用次数相同。

7.根据权利要求1所述的参数化可重构fpga数字波束形成装置,其特征在于:加法器树层级m计算公式为:

技术总结

本发明提出了一种参数化可重构FPGA数字波束形成装置,属于雷达探测技术领域,主要用于解决FPGA数字波束形成器在不同型号数字阵列雷达工程实现时的快速重构问题,通过合理配置参数,所重构的波束形成器能够在空域快拍数据率与FPGA处理时钟不匹配时,基于流水复用大幅减少复数乘法器的资源消耗。本发明采用参数配置器构建可重构的FPGA数字波束形成器,通过环形缓冲器组将输入的并行空域快拍数据转化为串行数据流,汇入复数乘法器组实现DBF加权处理的流水复用,进而通过复数累加器组和加法器树完成DBF处理。

技术研发人员:冷鹏飞,王博阳,周升国,吕卫祥

受保护的技术使用者:中国船舶集团有限公司第七二四研究所

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!