芯片内自检装置、方法、电子设备及存储介质与流程

本发明涉及数据处理,尤其涉及一种芯片内自检装置、方法、电子设备及存储介质。

背景技术:

1、芯片关键参数包括频率、电压、电流、温度等,其中大部分芯片设计中采用内置温度传感器方式实现了温度的自检;但是针对频率参数,特别是时钟频率参数,通常都是通过外部其他处理器共同来实现检测。

2、但是,随着对于芯片安全性和可靠性的要求日益提高,通过外部其它处理器来进行时钟频率的检测可能存在可靠性和安全性问题。

技术实现思路

1、本发明提供一种芯片内自检装置、方法、电子设备及存储介质,用以解决现有技术中通过外部其它处理器来进行时钟频率的检测可能存在可靠性和安全性问题的缺陷。

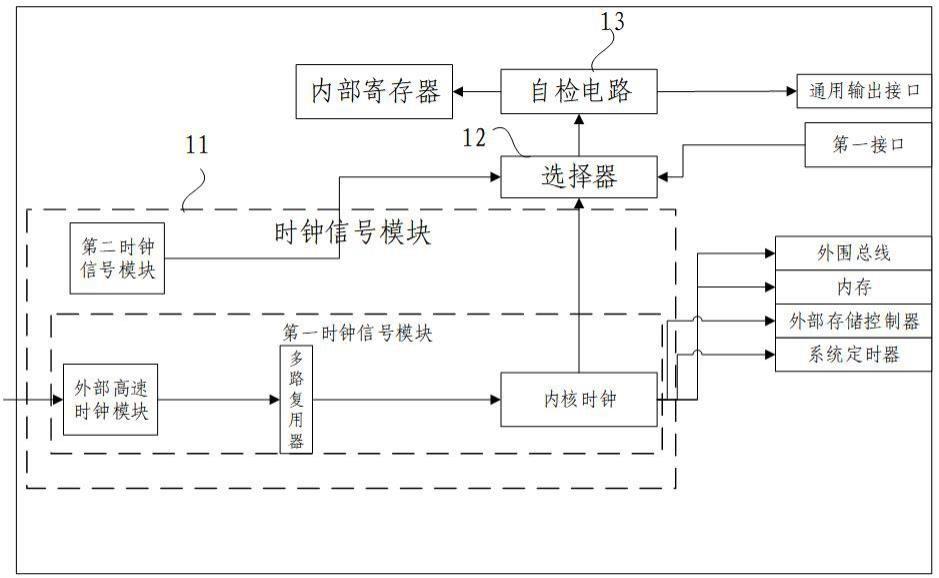

2、本发明提供一种芯片内自检装置,包括:时钟信号模块、选择器和自检电路,所述选择器分别与所述时钟信号模块和所述自检电路通信连接;

3、其中,所述时钟信号模块用于生成内部时钟信号,并接收外部输入的外部时钟信号,将所述内部时钟信号和所述外部时钟信号传输到所述选择器;

4、其中,所述选择器用于控制所述内部时钟信号和所述外部时钟信号交替输入到所述自检电路;

5、其中,所述自检电路用于对交替输入的所述内部时钟信号和所述外部时钟信号进行自检分析,得到检测结果。

6、根据本发明提供的一种芯片内自检装置,所述装置还包括:第一接口,所述第一接口与所述选择器通信连接;

7、其中,所述第一接口用于将时钟接入周期写入所述选择器,所述时钟接入周期用于为所述选择器配置所述内部时钟信号和所述外部时钟信号交替接入所述自检电路的周期。

8、根据本发明提供的一种芯片内自检装置,所述选择器,具体用于:

9、在一个所述时钟接入周期内,将m个内部时钟信号传输到所述自检电路中进行检测分析后,将n个外部时钟信号传输到所述自检电路中进行检测分析,其中,m与n均为与所述时钟接入周期关联的正整数。

10、根据本发明提供的一种芯片内自检装置,所述自检电路,具体用于:

11、在检测到所述内部时钟信号的时钟频率与第一时钟频率自检结果不一致的情况下,得到所述检测结果为自检电路故障;

12、其中,所述第一时钟频率自检结果是所述自检电路对所述内部时钟信号进行时钟频率自检分析得到的;

13、或,在检测到所述外部时钟信号的时钟频率与第二时钟频率自检结果不一致的情况下,得到所述检测结果为外部时钟信号错误;

14、其中,所述第二时钟频率自检结果是所述自检电路对所述外部时钟信号进行时钟频率自检分析得到的。

15、根据本发明提供的一种芯片内自检装置,所述装置还包括:第二接口,所述第二接口与所述自检电路通信连接;

16、其中,所述第二接口用于在接收到所述自检电路故障的情况下,输出自检电路故障预警,或在接收到所述外部时钟信号错误的情况下,输出外部时钟信号错误预警。

17、根据本发明提供的一种芯片内自检装置,所述时钟信号模块,具体包括:第一时钟信号模块和第二时钟信号模块,所述第一时钟信号模块和第二时钟信号模块分别与所述选择器通信连接;

18、其中,所述第一时钟信号模块用于接收并传输所述外部时钟信号;

19、其中,所述第二时钟信号模块为内部高速振荡器,用于生成所述内部时钟信号,其中,所述第二时钟信号模块设置于所述装置的内部。

20、根据本发明提供的一种芯片内自检装置,所述第一时钟信号模块,具体包括:外部高速时钟模块和倍频模块,所述倍频模块分别与所述外部高速时钟模块和所述自检电路通信连接;

21、其中,所述外部高速时钟模块用于生成外部时钟信号,所述倍频模块用于将所述外部时钟信号进行倍频处理后传输至所述选择器。

22、根据本发明提供的一种芯片内自检装置,所述装置还包括:内部寄存器,所述内部寄存器与所述自检电路通信连接;

23、其中,所述内部寄存器用于存储所述检测结果。

24、本发明还提供一种基于上述芯片内自检装置的芯片内自检方法,包括:

25、所述选择器按照时钟接入周期,控制所述内部时钟信号和所述外部时钟信号交替输入到所述自检电路,其中,所述内部时钟信号用于检测所述自检电路的状态,所述内部时钟信号由设置在所述装置内部的第一时钟信号模块生成;

26、所述自检电路会根据交替输入的所述内部时钟信号和所述外部时钟信号进行自检分析,得到检测结果。

27、根据本发明提供的一种芯片内自检方法,所述自检电路会根据交替输入的所述内部时钟信号和所述外部时钟信号进行自检分析,得到检测结果,具体包括:

28、所述自检电路对所述内部时钟信号进行时钟频率自检分析,得到第一时钟频率自检结果;

29、在所述第一时钟频率自检结果与所述内部时钟信号的时钟频率不一致的情况下,得到所述检测结果为自检电路故障。

30、根据本发明提供的一种芯片内自检方法,所述自检电路会根据交替输入的所述内部时钟信号和所述外部时钟信号进行自检分析,得到检测结果,具体包括:

31、所述自检电路对所述外部时钟信号进行时钟频率自检分析,得到第二时钟频率自检结果;

32、在所述外部时钟信号的时钟频率与第二时钟频率自检结果不一致的情况下,得到所述检测结果为外部时钟信号错误。

33、本发明还提供一种电子设备,包括存储器、处理器及存储在存储器上并可在处理器上运行的计算机程序,所述处理器执行所述程序时实现如上述任一种所述芯片内自检方法。

34、本发明还提供一种非暂态计算机可读存储介质,其上存储有计算机程序,该计算机程序被处理器执行时实现如上述任一种所述芯片内自检方法。

35、本发明还提供一种计算机程序产品,包括计算机程序,所述计算机程序被处理器执行时实现如上述任一种所述芯片内自检方法。

36、本发明提供的芯片内自检装置、方法、电子设备及存储介质,通过时钟信号模块,可以在芯片内部产生一个已知频率的内部时钟信号,进而通过内部时钟信号来对自检电路进行检测,然后通过将内部时钟信号和外部时钟信号交替输入到自检电路,能够在有效保证自检电路正常工作的情况下,准确的对外部时钟信号进行时钟频率检测,有效保证时钟频率检测的准确性,整个检测过程无需外部设备来进行辅助,通过芯片内部的芯片内自检装置既可以完成时钟信号频率的检测,有效保证了检测的安全性和可靠性。

技术特征:

1.一种芯片内自检装置,其特征在于,包括:时钟信号模块、选择器和自检电路,所述选择器分别与所述时钟信号模块和所述自检电路通信连接;

2.根据权利要求1所述的芯片内自检装置,其特征在于,所述装置还包括:第一接口,所述第一接口与所述选择器通信连接;

3.根据权利要求2所述的芯片内自检装置,其特征在于,所述选择器,具体用于:

4.根据权利要求1所述的芯片内自检装置,其特征在于,所述自检电路,具体用于:

5.根据权利要求4所述的芯片内自检装置,其特征在于,所述装置还包括:第二接口,所述第二接口与所述自检电路通信连接;

6.根据权利要求1所述的芯片内自检装置,其特征在于,所述时钟信号模块,具体包括:第一时钟信号模块和第二时钟信号模块,所述第一时钟信号模块和第二时钟信号模块分别与所述选择器通信连接;

7.根据权利要求6所述的芯片内自检装置,其特征在于,所述第一时钟信号模块,具体包括:外部高速时钟模块和倍频模块,所述倍频模块分别与所述外部高速时钟模块和所述自检电路通信连接;

8.根据权利要求1所述的芯片内自检装置,其特征在于,所述装置还包括:内部寄存器,所述内部寄存器与所述自检电路通信连接;

9.一种基于上述权利要求1-8任一项所述芯片内自检装置的芯片内自检方法,其特征在于,包括:

10.根据权利要求9所述的芯片内自检方法,其特征在于,所述自检电路会根据交替输入的所述内部时钟信号和所述外部时钟信号进行自检分析,得到检测结果,具体包括:

11.根据权利要求10所述的芯片内自检方法,其特征在于,所述自检电路会根据交替输入的所述内部时钟信号和所述外部时钟信号进行自检分析,得到检测结果,具体包括:

12.一种电子设备,包括存储器、处理器及存储在所述存储器上并可在所述处理器上运行的计算机程序,其特征在于,所述处理器执行所述程序时实现如权利要求9至11任一项所述芯片内自检方法。

13.一种非暂态计算机可读存储介质,其上存储有计算机程序,其特征在于,所述计算机程序被处理器执行时实现如权利要求9至11任一项所述芯片内自检方法。

技术总结

本发明提供一种芯片内自检装置、方法、电子设备及存储介质,涉及数据处理技术领域,包括:时钟信号模块、选择器和自检电路,选择器分别与时钟信号模块和自检电路通信连接;其中,时钟信号模块用于生成内部时钟信号,并接收外部输入的外部时钟信号,将内部时钟信号和外部时钟信号传输到选择器;其中,选择器用于控制内部时钟信号和外部时钟信号交替输入到自检电路;其中,自检电路用于对交替输入的内部时钟信号和外部时钟信号进行自检分析,得到检测结果。在芯片内部产生一个已知频率的内部时钟信号,进而通过内部时钟信号来对自检电路进行检测,在有效保证自检电路正常工作的情况下,准确的对外部时钟信号进行时钟频率检测。

技术研发人员:吴正中,张辉,唐才荣,刘强,邓能文,张祥彬,王晓东

受保护的技术使用者:北京城建智控科技股份有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!