具有老化检测功能的芯片的制作方法

本申请涉及电子设备,特别是涉及一种具有老化检测功能的芯片。

背景技术:

1、随着集成电路制造工艺的不断发展,尤其是在电路规格进入深亚微米阶段后,电路的老化效应对集成电路的性能、功耗、可靠性等指标的影响也越来越突出。其中,集成电路的老化效应包括:电迁移(electromigration,em)、负偏压温度不稳定性(negative biastemperature instability,nbti)、热载流子注入(hot carrier injection,hci)等。随着集成电路的使用时间的推移,芯片在上述老化效应的影响下,芯片电路的传输延迟可能逐渐增加,进而导致芯片的性能退化、甚至是功能故障。

2、目前为了应对集成电路的老化效应,对芯片的性能、功耗以及可靠性等指标的影响,通常采用预留设计裕量的处理方式。集成电路开发工程师在电路设计阶段预估电路老化效应可能对电路带来的影响。进而根据预估的影响情况在集成电路的设计阶段预留足够大的设计裕量,以避免电路老化效应对电路的影响。例如,针对电路老化效应可能带来的电路传输延迟的问题,集成电路开发工程师在设计阶段就以电路传输延迟较大为指标去处理电路时序,以使得电路上各器件在接收到上级器件延迟传输的数据时也可以按照设计的电路时序处理数据。

3、然而,采用预留设计裕量的处理方式处理电路老化效应对电路影响的有效性,较为依赖集成电路开发工程师对电路老化效应对电路影响的预估能力,导致对电路老化效应影响情况的分析可能存在准确较低的问题,影响芯片的工作性能。

技术实现思路

1、鉴于上述问题,提出了本申请实施例以便提供一种克服上述问题或者至少部分地解决上述问题的芯片,以解决目前针对电路老化效应对电路影响情况的分析准确性较低的问题。

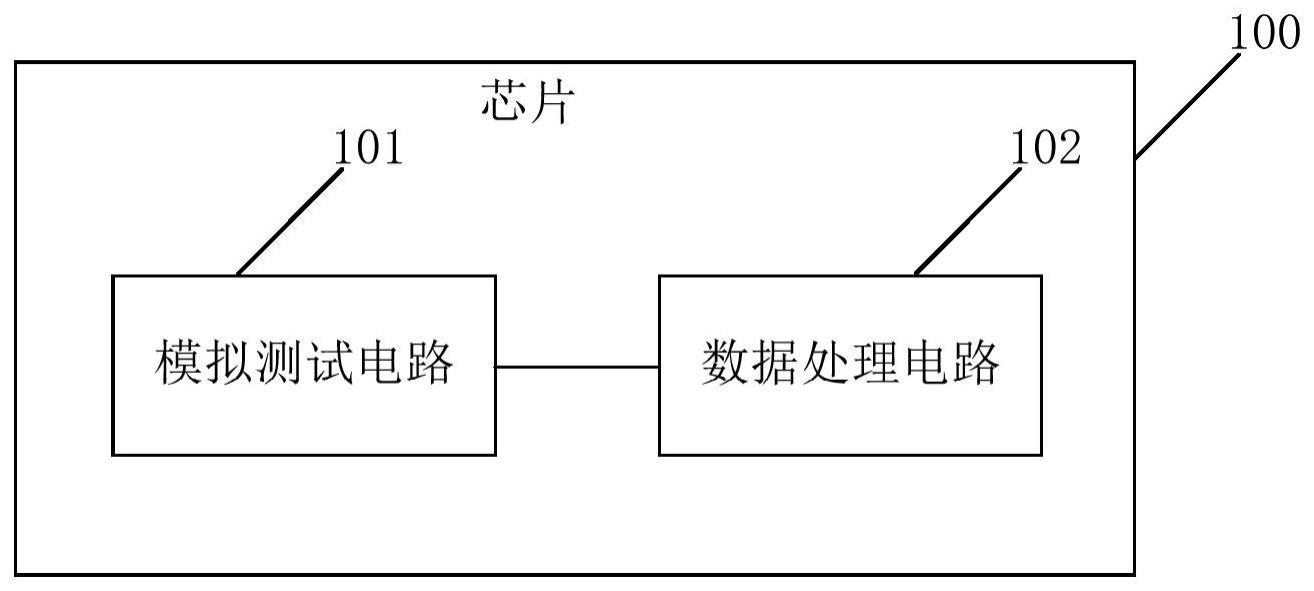

2、为了解决上述问题,本申请实施例公开了一种具有老化检测功能的芯片芯片,包括:

3、模拟测试电路、被测电路和数据处理电路,所述模拟测试电路包括的电路逻辑单元与构成所述被测电路的电路逻辑单元至少部分一致,且所述模拟测试电路的运行时期与所述被测电路的运行时期一致;

4、所述模拟测试电路与所述数据处理电路连接,所述模拟测试电路在运行时期向所述数据处理电路传输测试输出信号;

5、所述数据处理电路,根据所述模拟测试电路在芯片初始运行时期传输的测试输出信号,确定所述模拟测试电路的第一性能表征数据,所述第一性能表征数据用于表征所述被测电路在所述芯片初始运行时期的电路性能;以及接收有效的老化测试使能信号,根据所述模拟测试电路在老化测试时期传输的测试输出信号,确定所述模拟测试电路的第二性能表征数据,所述老化测试时期为所述老化测试使能信号连续有效的时期,所述第二性能表征数据用于表征所述被测电路在所述老化测试时期的电路性能;以及根据所述第一性能表征数据和所述第二性能表征数据计算所述被测电路的老化率。

6、本申请实施例还公开了一种电子设备,包括如前述第一方面任一所述的芯片。

7、本申请实施例包括以下优点:

8、在本申请实施例中,芯片包括模拟测试电路、被测电路和数据处理电路。其中,模拟测试电路在运行时期向数据处理电路传输测试输出信号。由于模拟测试电路包括的电路逻辑单元与构成被测电路的电路逻辑单元一致,且模拟测试电路的运行时期与被测电路的运行时期一致。因此,复刻有被测电路的电路逻辑单元的模拟测试电路,通过与被测电路同步运行于同一芯片上,使得模拟测试电路输出的测试输出信号可以较为真实地反映被测电路当前的电路逻辑单元的电路性能。因而,根据模拟测试电路在芯片初始运行时期传输的测试输出信号确定的第一性能表征数据,可以较为准确地表征被测电路在老化测试时期的电路性能。且根据模拟测试电路在老化测试时期传输的测试输出信号确定的第二性能表征数据,可以较为准确地表征被测电路在老化测试时期的电路性能。这样,第一性能表征数据和第二性能表征数据的差异可以较为准确地确定被测电路在芯片初始运行时期至老化测试时期内其电路逻辑单元受电路老化效应影响的程度。因而,根据第一性能表征数据和第二性能表征数据确定的老化率可以较为准确地表征被测电路受电路老化效应影响的程度,相较于相关技术,提升了针对电路老化效应对电路影响情况的分析准确性。

技术特征:

1.一种具有老化检测功能的芯片,其特征在于,所述芯片包括:模拟测试电路、被测电路和数据处理电路,所述模拟测试电路包括的电路逻辑单元与构成所述被测电路的电路逻辑单元至少部分一致,且所述模拟测试电路的运行时期与所述被测电路的运行时期一致;

2.根据权利要求1所述的芯片,其特征在于,所述芯片还包括:测试参考电路,所述测试参考电路与所述模拟测试电路的电路结构一致;

3.根据权利要求2所述的芯片,其特征在于,所述模拟测试电路和所述测试参考电路为环振数字电路,所述模拟测试电路在运行时期向所述数据处理电路传输具有变化周期的测试输出信号,所述测试参考电路在所述老化测试时期向所述数据处理电路传输具有变化周期的参考输出信号;

4.根据权利要求3所述的芯片,其特征在于,所述数据处理电路,计算所述第一跳变次数和所述第二跳变次数的比值,得到所述第一性能表征数据;以及计算所述第三跳变次数和所述第四跳变次数的比值,得到所述第二性能表征数据,计算所述第一性能表征数据与所述第二性能表征数据的比值,得到所述被测电路的老化率。

5.根据权利要求3或4所述的芯片,其特征在于,所述数据处理电路包括:老化环振计数器和参考环振计数器,

6.根据权利要求5所述的芯片,其特征在于,所述老化环振计数器,从接收所述有效的老化测试使能信号以及有效的计数清零信号开始,统计所述测试输出信号由所述第一信号值跳变为所述第二信号值的跳变次数,直至接收无效的所述老化测试使能信号,统计得到所述第三跳变次数;

7.根据权利要求6所述的芯片,其特征在于,所述芯片包括:测试控制器,所述测试控制器与所述数据处理电路连接,所述测试控制器在针对所述被测电路的老化测试开始时,向所述数据处理电路传输所述有效的老化测试使能信号和所述有效的计数清零信号,并持续向所述数据处理电路传输所述有效的老化测试使能信号,直至在针对所述被测电路的老化测试结束时,向所述数据处理电路传输所述无效的老化测试使能信号。

8.根据权利要求3所述的芯片,其特征在于,所述数据处理电路还包括:初值存储器和老化率计算器,所述初值存储器存储所述第一跳变次数和所述第二跳变次数;

9.根据权利要求1所述的芯片,其特征在于,所述模拟测试电路中与所述被测电路相同的多个电路逻辑单元之间的连接线路,与所述被测电路中对应电路逻辑单元之间的连接线路一致。

10.根据权利要求1所述的芯片,其特征在于,所述模拟测试电路包括的电路逻辑单元与构成所述被测电路的电路逻辑单元一致。

技术总结

本申请实施例提供了一种具有老化检测功能的芯片,涉及电子设备技术领域。芯片中,模拟测试电路包括的电路逻辑单元与构成被测电路的电路逻辑单元至少部分一致,且模拟测试电路的运行时期与被测电路的运行时期一致。模拟测试电路在运行时期向数据处理电路传输测试输出信号。数据处理电路根据模拟测试电路在芯片初始运行时期传输的测试输出信号,确定模拟测试电路的第一性能表征数据,接收有效的老化测试使能信号,根据模拟测试电路在老化测试时期传输的测试输出信号,确定模拟测试电路的第二性能表征数据,根据第一性能表征数据和第二性能表征数据计算被测电路的老化率。本申请提升了针对电路老化效应对电路影响情况的分析准确性。

技术研发人员:杨梁

受保护的技术使用者:龙芯中科技术股份有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!