一种多通道串口芯片的功能检测系统的制作方法

本申请芯片检测,尤其涉及一种多通道串口芯片的功能检测系统。

背景技术:

1、在工业控制领域,串口设备常常用于与其他设备进行通信。常见的串口通信协议包括全双工的rs-232和rs-422,以及半双工的rs-485。此外,调试人员也常利用串口进行程序调试。因此,如何确保串口芯片的质量,以及如何更高效地检测出功能异常的芯片,成为了芯片制造商必须面对的问题。

2、目前,检测串口芯片质量的主要方法包括人工检查芯片焊接接口、抽样检测,以及使用串口调试助手进行简单的收发功能测试。然而,这些方法不仅耗费大量的人力和时间,而且有时可能会出现漏检的情况,从而影响芯片的正常交付。

技术实现思路

1、本申请的目的在于克服现有技术中的缺陷,提供及一种多通道串口芯片的功能检测系统。

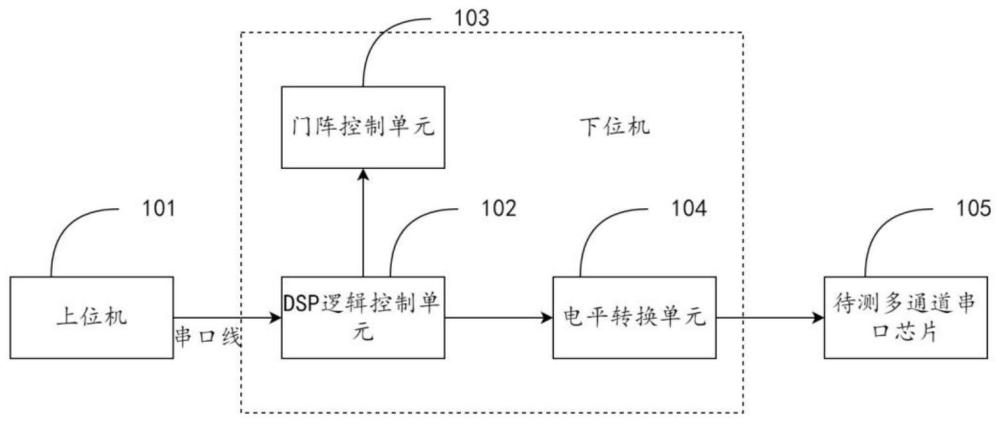

2、本申请提供的一种多通道串口芯片的功能检测系统,包括:上位机和下位机;所述上位机通过串口线连接下位机,所述下位机包括:dsp逻辑控制单元、门阵控制单元、电平转换单元、待测多通道串口芯片;

3、所述dsp逻辑控制单元经过所述电平转换单元与所述待测多通道串口芯片连接;所述门阵控制单元控制所述dsp逻辑控制单元的rx、tx引脚与待测多通道串口芯片的sdo-x、sdi-x引脚相连,进行芯片的功能测试。

4、可选地,所述进行芯片的功能测试,包括串口发送功能测试:

5、所述待测多通道串口芯片的待测通道通过所述sdo-x引脚向dsp逻辑控制单元发送258个字节的数据帧,包括2个帧头字节、1个数据长度字节、254个数据字节和1个校验和字节;

6、检测所述rx引脚是否可以接收到数据帧,并比对接收和发送的数据帧;

7、若比对结果一致,待测芯片的待测通道的串口发送功能正常;

8、若未收到任何数据帧或比对结果不一致,发送功能异常。

9、可选地,所述进行芯片的功能测试,包括串口接收功能测试:

10、dsp逻辑控制单元的tx引脚按照芯片规定的数据帧格式向待测芯片的待测通道发送258个字节的数据帧;

11、检测该通道的sdi-x引脚是否可以接收到数据帧,并比对接收和发送的数据帧;

12、若比对结果一致,待测芯片的待测通道的串口接收功能正常;

13、若未收到任何数据帧或对比结果不一致,接收功能异常。

14、可选地,所述进行芯片的功能测试,包括帧头错误检测功能:

15、dsp逻辑控制单元构造两个错误帧头字节,发送到所述待测多通道串口芯片;

16、检测芯片的帧头错误位是否被置1;

17、若所述帧头错误位为1,该通道的帧头错误检测功能正常,否则帧头错误检测功能异常。

18、可选地,所述进行芯片的功能测试,包括校验和错误检测功能:

19、dsp逻辑控制单元构造错误的校验和字节,发送到所述待测多通道串口芯片;

20、检测芯片的校验和错误位是否被置1;

21、若所述校验和错误位为1,该通道的校验和错误检测功能正常,否则校验和错误检测功能异常。

22、可选地,所述进行芯片的功能测试,包括超时错误检测功能:

23、dsp逻辑控制单元按照规定的数据帧格式向所述待测多通道串口芯片传输数据,但是每个字节间的时间被设置为大于芯片设定的超时时间;

24、检测芯片的超时错误位是否被置1;

25、若所述超时错误位为1,该通道的超时错误检测功能正常,否则超时错误功能异常。

26、可选地,所述进行芯片的功能测试,包括校验方式错误检测功能:

27、dsp逻辑控制单元构造的字节奇偶方式与芯片预设的不一致向所述待测多通道串口芯片传输数据;

28、检测芯片的校验方式错误位是否被置1;

29、若所述校验方式错误位为1,该通道的校验方式错误检测功能正常,否则校验方式错误检测功能异常。

30、可选地,所述进行芯片的功能测试,包括高度表功能:

31、门阵控制单元向芯片的pulse引脚发送周期为3.28us的脉冲信号,每发送800次,将芯片的close引脚置为高电平,芯片停止更新脉冲计数值;

32、预设时间后门阵重新将芯片的close引脚置为低电平来重新计数;

33、若dsp逻辑控制单元通过xintf总线读取所述计数值的结果不为800,高度表功能异常。

34、可选地,所述上位机,包括:

35、向下位机发送命令、接收功能测试结果、提供人机交互界面,以及在人机交互界面中,配置串口通信参数、选择测试模式和功能测试项;

36、根据下位机的测试结果实时更新“测试结果”界面的指示灯颜色,并记录出现错误时的芯片位置和通道号。

37、本申请的优点和有益效果:

38、本申请提供的一种多通道串口芯片的功能检测系统,包括:上位机和下位机;所述上位机通过串口线连接下位机,所述下位机包括:dsp逻辑控制单元、门阵控制单元、电平转换单元、待测多通道串口芯片;所述dsp逻辑控制单元经过所述电平转换单元与所述待测多通道串口芯片连接;所述门阵控制单元控制所述dsp逻辑控制单元的rx、tx引脚与待测多通道串口芯片的sdo-x、sdi-x引脚相连,进行芯片的功能测试。本申请通过自动化测试,减少了人工参与和检测时间,提高了检测效率和准确性。同时,该系统可以实现对待测多通道串口芯片的所有通道进行功能测试,提高了测试的全面性和准确性。

技术特征:

1.一种多通道串口芯片的功能检测系统,其特征在于,包括:上位机和下位机;所述上位机通过串口线连接下位机,所述下位机包括:dsp逻辑控制单元、门阵控制单元、电平转换单元、待测多通道串口芯片;

2.根据权利要求1所述多通道串口芯片的功能检测系统,其特征在于,所述进行芯片的功能测试,包括串口发送功能测试:

3.根据权利要求1所述多通道串口芯片的功能检测系统,其特征在于,所述进行芯片的功能测试,包括串口接收功能测试:

4.根据权利要求1所述多通道串口芯片的功能检测系统,其特征在于,所述进行芯片的功能测试,包括帧头错误检测功能:

5.根据权利要求1所述多通道串口芯片的功能检测系统,其特征在于,所述进行芯片的功能测试,包括校验和错误检测功能:

6.根据权利要求1所述多通道串口芯片的功能检测系统,其特征在于,所述进行芯片的功能测试,包括超时错误检测功能:

7.根据权利要求1所述多通道串口芯片的功能检测系统,其特征在于,所述进行芯片的功能测试,包括校验方式错误检测功能:

8.根据权利要求1所述多通道串口芯片的功能检测系统,其特征在于,所述进行芯片的功能测试,包括高度表功能:

9.根据权利要求1~8任一项所述多通道串口芯片的功能检测系统,其特征在于,所述上位机,包括:

技术总结

本申请提供的一种多通道串口芯片的功能检测系统,包括:上位机和下位机;所述上位机通过串口线连接下位机,所述下位机包括:DSP逻辑控制单元、门阵控制单元、电平转换单元、待测多通道串口芯片;所述DSP逻辑控制单元经过所述电平转换单元与所述待测多通道串口芯片连接;所述门阵控制单元控制所述DSP逻辑控制单元的Rx、Tx引脚与待测多通道串口芯片的SDO‑X、SDI‑X引脚相连,进行芯片的功能测试。本申请通过自动化测试,减少了人工参与和检测时间,提高了检测效率和准确性。同时,该系统可以实现对待测多通道串口芯片的所有通道进行功能测试,提高了测试的全面性和准确性。

技术研发人员:杨通达,杨杰,赵召平,王丽莉

受保护的技术使用者:天津市英贝特航天科技有限公司

技术研发日:

技术公布日:2024/2/21

- 还没有人留言评论。精彩留言会获得点赞!