芯片的测试装置的制作方法

本申请的实施例涉及电子电路,具体地,涉及一种芯片的测试装置。

背景技术:

1、在电源或开关控制芯片中,一般并联有多个开关支路,各个开关支路上具有约为10mω的mosfet,且mosfet具有球形管脚,当有大电流流过时,受测试板布线及接触阻抗的影响,每个球上流过的电流不相同,使得芯片内部采样得不到准确的电流值,增加了产品测试误差。

技术实现思路

1、本文中描述的实施例提供了一种芯片的测试装置。

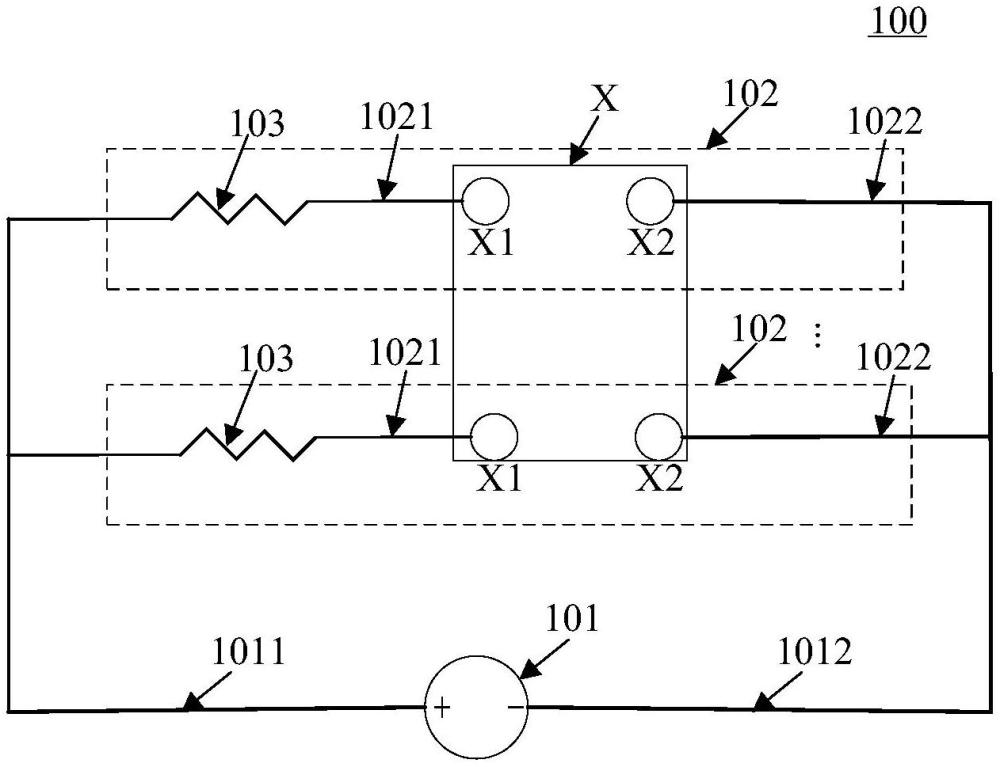

2、根据本申请的第一方面,提供了一种芯片的测试装置,芯片具有多个第一引脚和多个第二引脚,多个第一引脚为同名引脚,多个第二引脚为同名引脚,该测试装置包括测试信号源和多条测试支路;测试信号源具有用于提供测试信号的第一端和第二端;每条测试支路具有一第一电接入端以及一第二电接入端,第一电接入端与第一端连接且可电接触连接第一引脚,第二电接入端与第二端连接且可电接触连接第二引脚;每条测试支路上设置有均流电阻,均流电阻设置在第一电接入端与第一端之间和/或第二电接入端与第二端之间,且不同测试支路上,各个均流电阻的阻值相同。

3、在本申请的一些实施例中,均流电阻设置在一电路板上。

4、在本申请的一些实施例中,第一电接入端上均设置有可插接结构,以电接触连接第一引脚;第二电接入端上设置有可插接结构,以电接触连接第二引脚。

5、在本申请的一些实施例中,测试信号源包括一电源。

6、在本申请的一些实施例中,芯片为wlcsp芯片。

7、在本申请的一些实施例中,对于每条测试支路,其均流电阻的阻值为芯片内对应元件的电阻的设定倍数,设定倍数为10至100之间的值,测试支路的对应元件为设置在第一引脚与第二引脚之间,且可通过该测试支路的第一电接入端和第二电接入端接入该测试支路的元件。

8、在本申请的一些实施例中,上述对应元件包括:场效应晶体管,均流电阻包括:阻值相同的第一电阻和第二电阻;第一电阻设置在第一电接入端与第一端之间,第二电阻设置在第二电接入端与第二端之间,第一电阻和第二电阻的阻值之和是场效应晶体管的导通电阻的10倍至100倍。

9、在本申请的一些实施例中,上述对应元件包括:采样电阻,均流电阻包括:阻值相同的第四电阻和第五电阻;第四电阻设置在第一电接入端与第一端之间,第五电阻设置在第二电接入端与第二端之间,第四电阻和第五电阻的阻值之和是采样电阻的10倍至100倍。

10、在本申请的一些实施例中,上述对应元件的阻值为毫欧级别的电阻,均流电阻为欧姆级别功率电阻。

11、在本申请的一些实施例中,上述测试支路的数量为2条至4条之间的值。

12、本申请的实施例提供的芯片的测试装置,芯片具有多个第一引脚和多个第二引脚,多个第一引脚为同名引脚,多个第二引脚为同名引脚,测试装置包括测试信号源和多条测试支路;测试信号源具有用于提供测试信号的第一端和第二端;每条测试支路具有一第一电接入端以及一第二电接入端,第一电接入端与第一端连接且可电接触连接第一引脚,第二电接入端与第二端连接且可电接触连接第二引脚;每条测试支路上设置有均流电阻,均流电阻设置在第一电接入端与第一端之间和/或第二电接入端与第二端之间,且不同测试支路上,均流电阻的阻值相同,由于所有测试支路的均流电阻的阻值相同,可以保证所有测试支路的电流相同,不受支路其他因素的影响,提高了均流电流的均流效果,保证了待测芯片的测试效果。

技术特征:

1.一种芯片的测试装置,所述芯片具有多个第一引脚和多个第二引脚,所述多个第一引脚为同名引脚,所述多个第二引脚为同名引脚,其特征在于,所述测试装置包括测试信号源和多条测试支路;

2.根据权利要求1所述的测试装置,其特征在于,所述均流电阻设置在一电路板上。

3.根据权利要求1所述的测试装置,其特征在于,所述第一电接入端上均设置有可插接结构,以电接触连接所述第一引脚;所述第二电接入端上设置有可插接结构,以电接触连接所述第二引脚。

4.根据权利要求1所述的测试装置,其特征在于,所述测试信号源包括一电源。

5.根据权利要求1所述的测试装置,其特征在于,所述芯片为wlcsp芯片。

6.根据权利要求1所述的测试装置,其特征在于,对于每条测试支路,其均流电阻的阻值为所述芯片内对应元件的电阻的设定倍数,所述设定倍数为10至100之间的值,测试支路的对应元件为设置在所述第一引脚与所述第二引脚之间,且可通过该测试支路的第一电接入端和第二电接入端接入该测试支路的元件。

7.根据权利要求6所述的测试装置,其特征在于,所述对应元件包括场效应晶体管,所述均流电阻包括:阻值相同的第一电阻和第二电阻;所述第一电阻设置在所述第一电接入端与所述第一端之间,所述第二电阻设置在所述第二电接入端与所述第二端之间,所述第一电阻和所述第二电阻的阻值之和是所述场效应晶体管的导通电阻的10倍至100倍。

8.根据权利要求6所述的测试装置,其特征在于,所述对应元件包括采样电阻,所述均流电阻包括:阻值相同的第四电阻和第五电阻;所述第四电阻设置在所述第一电接入端与所述第一端之间,所述第五电阻设置在所述第二电接入端与所述第二端之间,所述第四电阻和所述第五电阻的阻值之和是所述采样电阻的10倍至100倍。

9.根据权利要求6所述的测试装置,其特征在于,所述对应元件的阻值为毫欧级别,所述均流电阻为欧姆级别功率电阻。

10.根据权利要求1所述的测试装置,其特征在于,所述测试支路的数量为2条至10条之间的值。

技术总结

本申请的实施例提供一种芯片的测试装置,芯片具有多个第一引脚和多个第二引脚,多个第一引脚为同名引脚,多个第二引脚为同名引脚,测试装置包括测试信号源和多条测试支路;测试信号源具有用于提供测试信号的第一端和第二端;每条测试支路具有一第一电接入端以及一第二电接入端,第一电接入端与第一端连接且可电接触连接第一引脚,第二电接入端与第二端连接且可电接触连接第二引脚;每条测试支路上设置有均流电阻,均流电阻设置在第一电接入端与第一端之间和/或第二电接入端与第二端之间,且不同测试支路上,均流电阻的阻值相同。通过本实施例提供的芯片的测试装置可以保证芯片的测试装置中流经各个测试支路的电流相同,减少了产品测试误差。

技术研发人员:孙守旭,王士江

受保护的技术使用者:圣邦微电子(北京)股份有限公司

技术研发日:20230920

技术公布日:2024/5/16

- 还没有人留言评论。精彩留言会获得点赞!