通用插座测试卡的制作方法

背景技术:

1、母板和主逻辑板(mlb)是与计算设备的主要部件耦接的印刷电路板(pcb)。主要部件的示例包括中央处理单元(cpu)、图形处理单元(gpu)、存储器等。为了实现与cpu的连接,母板/mlb包括cpu所附接的cpu插座。类似地,母板/mlb可以使用gpu插座来实现与gpu的连接。有各种测试插座的方法,比如但不限于upi(超路径互连)边界扫描互连(bsi)测试、结构测试增强(structural test plus,stp)测试等。

技术实现思路

技术特征:

1.一种测试卡,包括:

2.如权利要求1所述的测试卡,其中,所述测试部件是用模拟所述测试功能的所述逻辑编程的现场可编程门阵列(fpga)集成电路或复杂可编程逻辑器件(cpld)集成电路。

3.如权利要求2所述的测试卡,其中,所述fpga集成电路或所述cpld集成电路被编程为用作模拟ieee 1149.1/6边界扫描能力的虚拟cpu模块。

4.如权利要求1所述的测试卡,其中,所述测试功能是通用边界扫描(ubs)测试。

5.如权利要求1所述的测试卡,其中,所述测试功能是边界扫描互连(bsi)测试。

6.如权利要求5所述的测试卡,其中,所述测试部件包括与所述插座的联合测试行动组(jtag)引脚相对应的多个jtag端口。

7.如权利要求1所述的测试卡,其中,所述适配器pcb被配置为通过具有与所述对应插座类型的引脚配置相匹配的引脚配置来与所述对应插座类型连接。

8.如权利要求7所述的测试卡,其中,所述测试部件被配置为通过产生扫描信号并将所述扫描信号应用于所述适配器pcb的引脚配置来模拟所述测试功能,其中,所述适配器pcb被配置为将所述扫描信号应用于所述对应插座类型的引脚配置。

9.如权利要求7所述的测试卡,其中,所述测试部件被配置为通过以下操作来模拟所述测试功能:经由连接到所述对应插座类型的引脚配置的所述适配器pcb的引脚配置,从所述对应插座类型接收扫描信号。

10.如权利要求1所述的测试卡,其中,所述对应插座类型是cpu插座类型和gpu插座类型中的一种。

11.如权利要求1所述的测试卡,其中,所述测试部件是通用测试部件,在所述通用测试部件中,所述逻辑被编程为测试多个插座类型。

12.如权利要求1所述的测试卡,其中,所述测试部件是虚拟cpu模块,所述虚拟cpu模块被编程为模拟ieee 1149.1/6边界扫描能力。

13.一种方法,包括:

14.如权利要求13所述的方法,其中,所述测试部件是用模拟所述测试功能的所述逻辑编程的现场可编程门阵列(fpga)集成电路或复杂可编程逻辑器件(cpld)集成电路。

15.如权利要求13所述的方法,其中,所述测试功能是通用边界扫描(ubs)测试、边界扫描互连(bsi)测试和ieee 1149.1/6边界扫描能力中的一个。

16.如权利要求13所述的方法,其中,所述适配器pcb被配置为通过具有与所述对应插座类型的引脚配置相匹配的引脚配置来与所述对应插座类型连接。

17.如权利要求13所述的方法,其中,执行所述测试功能包括:

18.如权利要求13所述的方法,其中,执行所述测试功能包括:

19.如权利要求13所述的方法,进一步包括将所述测试部件中的所述逻辑编程为模拟所述测试功能。

20.一种中央处理单元(cpu)插座测试装置,包括:

技术总结

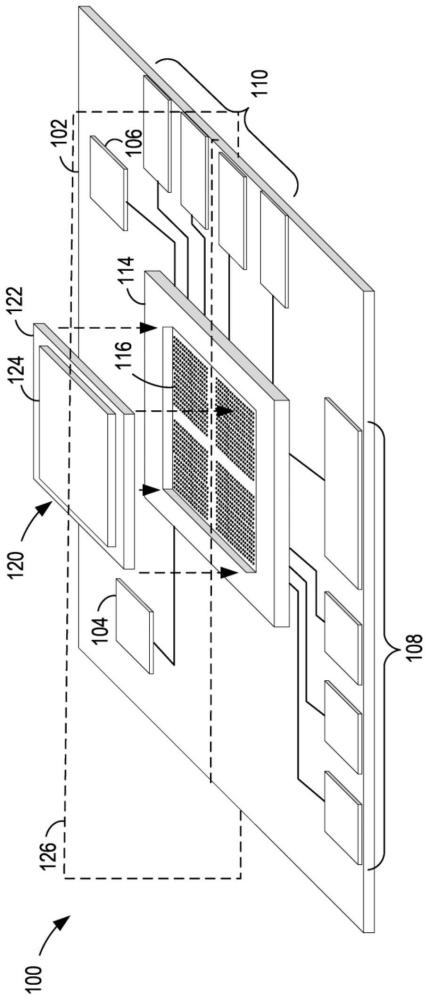

本公开涉及通用插座测试卡。提供了用于测试插座(比如但不限于CPU插座和GPU插座)的系统和方法。本文公开的系统和方法利用具有测试部件和适配器印刷电路板的测试卡。适配器印刷电路板(PCB)被配置为与母板上的对应插座类型连接,并用作测试部件与对应插座类型的插座之间的接口。测试部件包括模拟用于测试插座的测试功能的逻辑。通过使用适配器PCB将测试卡连接到插座,可以通过模拟测试卡上的测试功能来测试插座。

技术研发人员:吴旻晃,H·卡斯蒂略瓦莱斯

受保护的技术使用者:慧与发展有限责任合伙企业

技术研发日:

技术公布日:2025/2/20

- 还没有人留言评论。精彩留言会获得点赞!