一种用于测试集成电路的电路架构及集成电路测试方法与流程

本发明涉及集成电路测试,尤其是涉及一种用于测试集成电路的电路架构及集成电路测试方法。

背景技术:

1、目前在对集成电路进行测试时,通常在芯片的电源管脚或者ld。输出管脚连接电解电容作为旁路电容,以提高电压的稳定性。在进行开短路测试时,测试机向待测芯片发送测试电流,通过测量待测芯片上管脚接收到该电流或电压来确定测试结果是否合格。

2、然而,由于芯片外接电解电容,测试机发出电流或待机指令后会先给电解电容充电,需要一定延迟之后,才能获得测试结果,导致测试周期长,测试效率不理想。

技术实现思路

1、有鉴于此,本发明的目的在于提供一种用于测试集成电路的电路架构及集成电路测试方法。

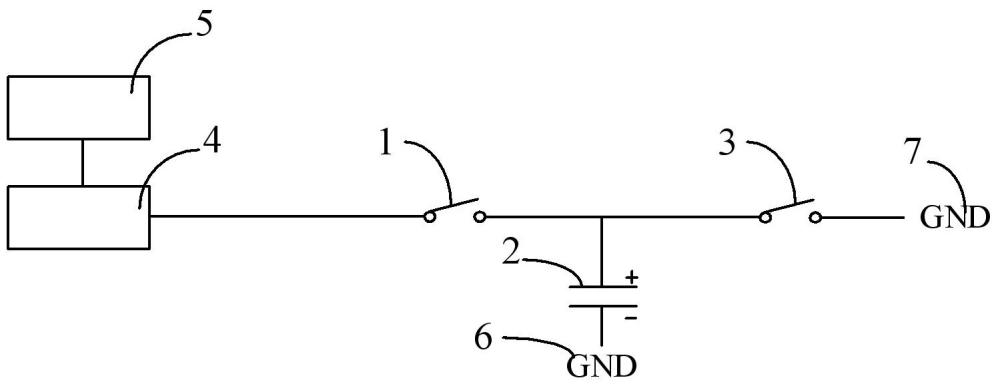

2、第一方面,本发明实施例提供了一种用于测试集成电路的电路架构,该电路架构包括:第一开关、电容和第二开关;

3、第一开关的第一端为电路架构的输入端,输入端与待测芯片和测试机电性连接;

4、第一开关的第二端与电容的正极端电性连接,电容的负极端与第一接地端电性连接;

5、电容的正极端还与第二开关的第一端连接,第二开关的第二端与第二接地端电性连接;

6、其中,第一开关与第二开关则一导通。

7、结合第一方面,第一开关断开且第二开关闭合时,测试机向待测芯片发送测试电流,形成待测芯片与测试机之间的开短路测试电路。

8、结合第一方面,第一开关闭合且第二开关断开时,待测芯片、第一开关、电容连通,形成功能测试电路。

9、结合第一方面,第一开关断开且第二开关闭合时,测试机向待测芯片发送待机指令,形成待测芯片与测试机之间的待机测试电路。

10、结合第一方面,测试机上具有多个点位,待测芯片具有多个管脚,多个点位与多个管脚一一对应电性连接。

11、结合第一方面,测试机、第一开关和第二开关分别与继电器控制板电性连接。

12、第二方面,本申请提供一种集成电路测试方法,应用于上述的用于测试集成电路的电路架构,该方法包括:

13、断开第一开关,并,闭合第二开关,以使测试机与待测芯片的管脚电性连接并阻断隔离外围电容;

14、控制测试机向待测芯片发送测试电流;

15、将管脚的当前电压确定为开短路测试结果。

16、结合第二方面,测试电流为100ua。

17、结合第二方面,将管脚的当前电压确定为开短路测试结果的步骤之后,还包括:

18、闭合第一开关,并,断开第二开关,导通芯片、电容和第一接地端的连接线路,以向电容充电;

19、针对芯片的每一项功能,通过测试机对芯片进行功能测试,得到功能对应的测试结果;

20、基于全部的测试结果确定待测芯片的功能测试结果。

21、结合第二方面,基于全部的测试结果确定芯片的功能测试结果的步骤之后,还包括:

22、闭合第二开关,并,断开第一开关,导通电容与第二开关、第二接地端的连接线路,以使电容放电;

23、控制测试机向待测芯片发送待机指令;

24、将待测芯片的当前电流确定为待测芯片的待机电流。

25、本发明实施例带来了以下有益效果:本申请提供的一种用于测试集成电路的电路架构及集成电路测试方法,该电路架构包括第一开关的第一端为电路架构的输入端,输入端与待测芯片和测试机电性连接;第一开关的第二端与电容的正极端电性连接,电容的负极端与第二接地端电性连接;电容的正极端还与第二开关的第一端连接,第二开关的第二端与第二接地端电性连接;其中,第一开关与第二开关则一导通。

26、本申请提供的于测试集成电路的电路架构,通过第一开关与第二开关则一导通的方式导通相应的电路,以在测试过程中,保持测试机和待测芯片中间没有其他外围器件,减小等待电容充放电时长,缩短集成电路的测试周期,进而提高集成电路的测试效率。

27、本发明的其他特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本发明而了解。本发明的目的和其他优点在说明书、权利要求书以及附图中所特别指出的结构来实现和获得。

28、为使本发明的上述目的、特征和优点能更明显易懂,下文特举较佳实施例,并配合所附附图,作详细说明如下。

技术特征:

1.一种用于测试集成电路的电路架构,其特征在于,所述电路架构包括:第一开关、电容和第二开关;

2.根据权利要求1所述的电路架构,其特征在于,所述第一开关断开且所述第二开关闭合时,所述测试机向所述待测芯片发送测试电流,形成所述待测芯片与所述测试机之间的开短路测试电路。

3.根据权利要求1所述的电路架构,其特征在于,所述第一开关闭合且所述第二开关断开时,所述待测芯片、所述第一开关、所述电容连通,形成功能测试电路。

4.根据权利要求1所述的电路架构,其特征在于,所述第一开关断开且所述第二开关闭合时,所述测试机向所述待测芯片发送待机指令,形成所述待测芯片与所述测试机之间的待机测试电路。

5.根据权利要求1所述的电路架构,其特征在于,所述测试机上具有多个点位,所述待测芯片具有多个管脚,多个所述点位与多个所述管脚一一对应电性连接。

6.根据权利要求1所述的电路架构,其特征在于,所述测试机、所述第一开关和所述第二开关分别与继电器控制板电性连接。

7.一种集成电路测试方法,其特征在于,应用于如权利要求1-6任一项所述的用于测试集成电路的电路架构,所述方法包括:

8.根据权利要求7所述的方法,其特征在于,所述测试电流为100ua。

9.根据权利要求7所述的方法,其特征在于,将所述管脚的当前电压确定为开短路测试结果的步骤之后,还包括:

10.根据权利要求7所述的方法,其特征在于,基于全部的所述测试结果确定所述芯片的功能测试结果的步骤之后,还包括:

技术总结

本发明涉及集成电路测试技术领域,尤其是涉及一种用于测试集成电路的电路架构及集成电路测试方法,该电路架构包括:第一开关、电容和第二开关;第一开关的第一端为电路架构的输入端,输入端与待测芯片和测试机电性连接;第一开关的第二端与电容的正极端电性连接,电容的负极端与第一接地端电性连接;电容的正极端还与第二开关的第一端连接,第二开关的第二端与第二接地端电性连接。本申请提供的于测试集成电路的电路架构,通过第一开关与第二开关则一导通的方式导通相应的电路,以在测试过程中,保持测试机和待测芯片中间没有其他外围器件,减小等待电容充放电时长,缩短集成电路的测试周期,进而提高集成电路的测试效率。

技术研发人员:丁盛峰,李志浩,阮辉

受保护的技术使用者:杭州芯云半导体技术有限公司

技术研发日:

技术公布日:2024/6/2

- 还没有人留言评论。精彩留言会获得点赞!