用于测试电路的系统和方法与流程

本公开总体上涉及电路,并且在具体的实施例中涉及用于测试电路的系统和方法。

背景技术:

1、锁相环(pll)是生成具有相应的相位的输出信号的控制系统,相应的相位与相应的输入信号的相位有关。存在多种类型的pll,其中最简单的pll是具有被一起耦合在反馈环中的可变频率振荡器和相位检测器的电路。施加的电压成比例地控制可变频率振荡器的频率和相位。因此,可变频率振荡器也被称为压控振荡器(vco)。振荡器产生具有特定频率的周期信号,并且相位检测器随后将周期信号的相位与输入的周期信号的相应的相位进行比较。这允许调整振荡器以维持输入的周期信号与输出的周期信号之间的相位匹配。

2、保持输入相位和输出相位同步也表示保持输入频率和输出频率相同。因此,除同步信号之外,锁相环可以追踪输入频率,或它可以生成等于输入频率的倍数的频率。这些特征被用于计算机时钟同步、解调以及频率合成。

3、锁相环被广泛地用于无线电、电信、计算机以及其他电子应用,诸如针对汽车应用的片上系统。它们可以被用于解调信号,从噪声通信信道恢复信号,以输入频率的倍数生成稳定频率(频率合成),或者在诸如微处理器之类的数字逻辑电路中分配精确定时的时钟脉冲。由于单一集成电路现在可以提供完整的锁相环构建块,因此该技术被广泛地用于现代电子设备,其中输出频率从一赫兹的一小部分直到许多吉赫兹。因此,期望用于测试锁相环的新的解决方案。

技术实现思路

1、根据一个实施例,一种用于测试电路的系统包括:锁相环;测试逻辑电路,测试逻辑电路被耦合到锁相环,测试逻辑电路被配置为使用参考时钟作为参考对锁相环的时钟周期的数目计数,参考时钟被耦合到测试逻辑电路;以及测试控制器,测试控制器被耦合到锁相环和测试逻辑电路,测试控制器被配置为利用从测试逻辑电路所接收的时钟周期的所计数的数目测量锁相环的时钟频率。

2、根据另一实施例,一种用于测试电路的系统包括:锁相环;测试逻辑电路,测试逻辑电路被耦合到锁相环,测试逻辑电路包括:锁定周期计数器,锁定周期计数器被配置为对锁相环的激活时间与锁相环的锁定状态时间之间的参考时钟的周期的数目计数,参考时钟被耦合到测试逻辑电路;以及快速周期计数器,快速周期计数器被配置为使用参考时钟作为参考对锁相环的快速时钟周期的数目计数;以及测试控制器,测试控制器被耦合到锁相环和测试逻辑电路,测试控制器被配置为从锁定周期计数器接收锁定周期计数信号并且从快速周期计数器接收快速周期计数信号。

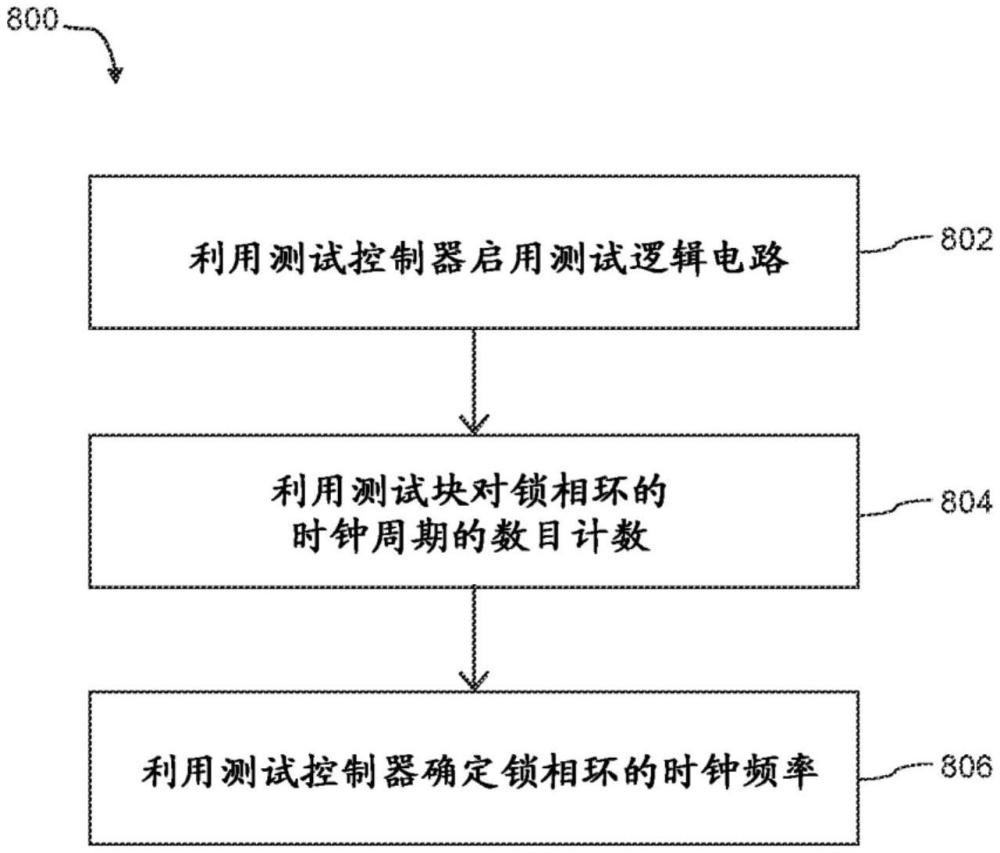

3、根据又一实施例,一种用于测试电路的方法包括:利用测试控制器启用测试逻辑电路,测试逻辑电路被耦合到锁相环和测试控制器;利用测试逻辑电路使用参考时钟作为参考对锁相环的时钟周期的数目计数,参考时钟被耦合到测试逻辑电路;以及利用测试控制器使用时钟周期的所计数的数目确定锁相环的时钟频率。

4、将要理解的是,上述总体的描述和下述详细的描述两者都仅是示例性且说明性的,并且不会限制本公开,正如要求的那样。

技术特征:

1.一种用于测试电路的系统,所述系统包括:

2.根据权利要求1所述的系统,其中所述测试逻辑电路还被配置为对所述锁相环的激活时间与所述锁相环的锁定状态时间之间的所述参考时钟的周期的数目计数。

3.根据权利要求2所述的系统,其中所述测试逻辑电路还被配置为基于所述锁相环的所述激活时间与所述锁相环的所述锁定状态时间之间的所述参考时钟的所述周期的所计数的所述数目,向所述测试控制器提供锁定状况信号。

4.根据权利要求2所述的系统,其中所述测试逻辑电路包括参考周期计数器,所述参考周期计数器被配置为设置窗口,在所述窗口上,所述锁相环的所述时钟周期的所述数目被计数。

5.根据权利要求4所述的系统,其中所述测试逻辑电路还包括延迟参考计数器,所述延迟参考计数器被配置为在延迟时间之后启用所述参考周期计数器。

6.根据权利要求1所述的系统,其中所述测试逻辑电路包括时钟门控单元,所述时钟门控单元被配置为门控来自所述锁相环的时钟信号。

7.根据权利要求1所述的系统,其中所述测试控制器使用高级外部设备总线接口被控制,所述高级外部设备总线接口通过桥被耦合到所述测试控制器。

8.根据权利要求1所述的系统,其中所述测试控制器还被配置为使用ieee 1149.1、ieee 1149.x、ieee 1500或者ieee 1687接口。

9.根据权利要求1所述的系统,其中所述测试控制器还被配置为运行内建自测试。

10.一种用于测试电路的系统,所述系统包括:

11.根据权利要求10所述的系统,其中所述锁定周期计数器还被配置为向所述测试控制器提供锁定状况信号。

12.根据权利要求10所述的系统,其中所述快速周期计数器还被配置为向所述测试控制器提供快速状况信号。

13.根据权利要求10所述的系统,其中所述测试逻辑电路还包括锁定比较器,所述锁定比较器被配置为执行来自所述锁定周期计数器的锁定周期的被测量的数目与锁定周期的预期最大数目之间的比较。

14.根据权利要求13所述的系统,其中所述锁定周期的所述预期最大数目从所述测试控制器被提供到所述锁定比较器。

15.根据权利要求10所述的系统,其中所述测试逻辑电路还包括快速周期比较器,所述快速周期比较器被配置为执行来自所述快速周期计数器的快速时钟周期的被测量的数目与快速时钟周期的预期数目之间的比较。

16.根据权利要求15所述的系统,其中所述快速周期比较器还被配置为使用范围执行来自所述快速周期计数器的所述快速时钟周期的被测量的所述数目与所述快速时钟周期的所述预期数目之间的比较,所述范围延伸到所述快速时钟周期的所述预期数目以上和以下达快速时钟范围。

17.根据权利要求16所述的系统,其中所述快速时钟周期的所述预期数目以及所述快速周期范围从所述测试控制器被提供到所述快速周期比较器。

18.一种用于测试电路的方法,所述方法包括:

19.根据权利要求18所述的方法,还包括:利用所述测试逻辑电路对所述锁相环的激活时间与所述锁相环的锁定状态时间之间的所述参考时钟的周期的数目计数。

20.根据权利要求18所述的方法,其中利用所述测试控制器确定所述锁相环的所述时钟频率发生在应用的运行时间期间,所述应用在装置上被运行,所述装置包括所述测试逻辑电路、所述测试控制器以及所述锁相环。

技术总结

本公开的实施例涉及用于测试电路的系统和方法。用于测试电路的系统包括锁相环、测试逻辑电路和测试控制器。测试逻辑电路被耦合到锁相环。测试逻辑电路被配置为使用参考时钟作为参考对锁相环的时钟周期的数目计数。参考时钟被耦合到测试逻辑电路。测试控制器被耦合到锁相环和测试逻辑电路。测试控制器被配置为利用从测试逻辑电路所接收的时钟周期的所计数的数目测量锁相环的时钟频率。

技术研发人员:M·卡萨尔萨

受保护的技术使用者:意法半导体国际公司

技术研发日:

技术公布日:2025/1/2

- 还没有人留言评论。精彩留言会获得点赞!