一种多通道集成芯片测试装置以及测试系统的制作方法

本申请涉及电子电路,特别是涉及一种多通道集成芯片测试装置以及测试系统。

背景技术:

1、随着微电子的发展,芯片尺寸的不断减小新的封装形式越来越多,新封装的发展方向是小型化,集成化,“短小轻薄”。诸如mini/microled显示、密集集成电路、微半导体等电子部件模组的制造工序中新型显示技术的快速发展。在产品和芯片制程小型化、精密化趋势下,往往需要进行导通检测和动作特性检查等过程。对多通道微小间距的参加输出检测功能的需求越来越多。

2、芯片测试装置是用于测试集成电路(芯片)功能、性能和质量的设备或系统。这些装置通常用于生产线上的芯片测试、质量控制和故障排除。芯片测试装置通常包括用于测试集成电路的自动化设备、用于测试芯片焊盘的连接质量和电气特性的焊盘测试机、用于测试芯片封装完整性的封装测试设备、用于测试芯片的功耗性能的功率测试仪以及用于测试射频集成电路的频率特性、增益、带宽等参数的射频测试设备等。

3、相关技术中,对电阻、电容等芯片元件的测量大多是单路测试,无法满足应用到各种线材等的电阻测试场景中去的测试需求。另一方面,即使有多路电阻测量,但是适配的测试设备也存在结构复杂且成本高昂的问题。

4、然而,申请人发现目前的芯片性能测试装置,存在如下的技术问题:

5、现有的测试装置存在测试效率较低以及设备适用率差的缺陷。

技术实现思路

1、基于此,有必要针对上述问题,提供一种能够对不同的待测模组进行快速对位检测,提高了对待测模组的测试效率的一种多通道集成芯片测试装置以及测试系统。

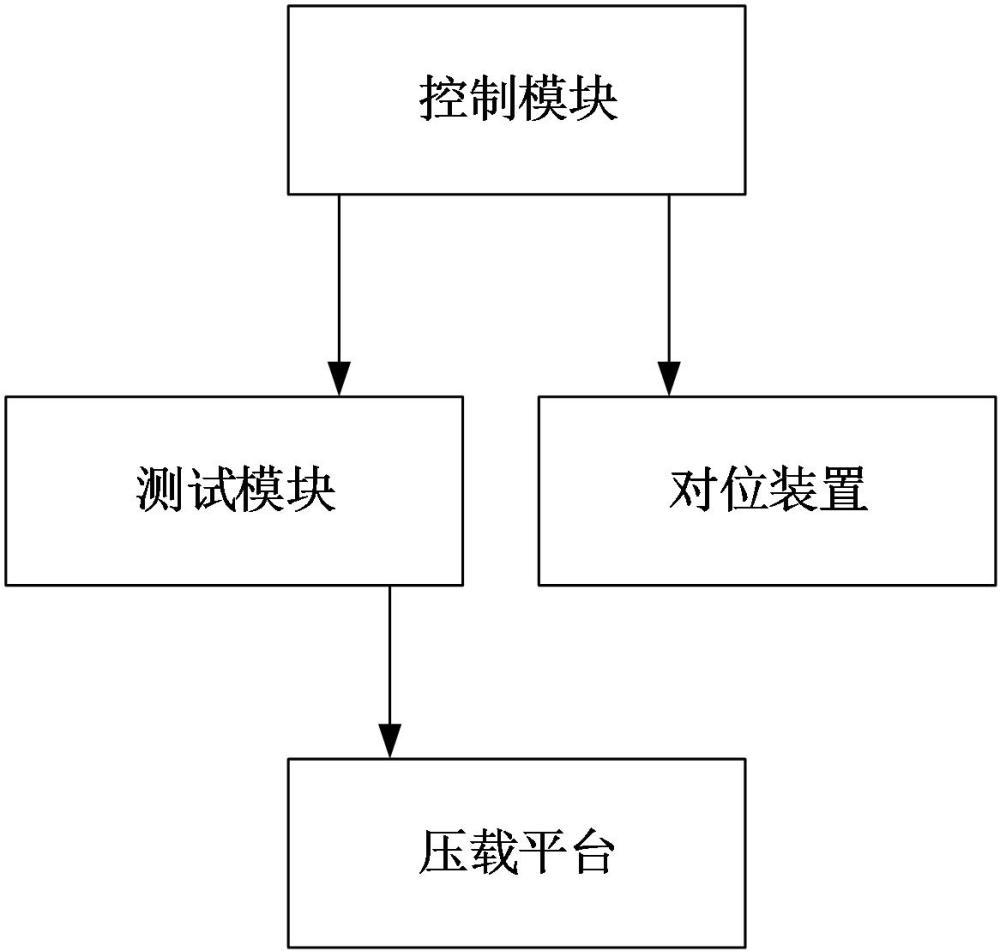

2、第一方面,本申请提供了一种多通道集成芯片测试装置,包括:

3、压载平台,用于承载及固定待测模组;

4、测试模块,用于与所述待测模组连接以实现测试信号的传输;

5、控制模块,用于实现测试信号的控制,所述控制模块与所述测试模块连接,并通过所述测试模块向所述待测模组传输所述测试信号,所述测试信号与所述待测模组的测试需求相对应;

6、对位装置,用于实现所述待测模组与所述测试模块的对位控制。

7、在其中一个实施例中,所述压载平台包括:

8、模组型腔,用于固定所述待测模组,所述模组型腔与所述待测模组相匹配;

9、模组盖板,用于固定所述待测模组,所述模组盖板与所述测试模块连接。

10、在其中一个实施例中,所述模组盖板包括:转接基板以及fpc测试板,所述fpc测试板在所述模组盖板压合时抵触于所述待测模组,以与所述待测模组连接。

11、在其中一个实施例中,所述压载平台包括:

12、对位移动平台,所述模组型腔固定于所述对位移动平台上,所述对位移动平台受控于所述控制模块,用于实现所述待测模组的对位连接;

13、所述对位移动平台包括水平调节单元、垂直调节单元以及旋转调节单元。

14、在其中一个实施例中,所述压载平台还包括:

15、输送单元,所述输送单元用于对所述待测模组进行输送。

16、在其中一个实施例中,所述测试模块包括:

17、通道选择单元,所述通道选择单元包括输入端口以及输出端口,所述输出端口多于所述输入端口。

18、在其中一个实施例中,所述测试模块包括若干个所述通道选择单元,若干个所述通道选择单元之间呈级联分布。

19、在其中一个实施例中,所述对位装置包括影像对位单元,所述影像对位单元用于基于所述待测模组的图像数据辅助所述待测模组进行对位连接。

20、在其中一个实施例中,所述对位装置包括位移单元,所述位移单元用于调节所述影像对位单元的拍摄位姿。

21、第二方面,本申请提供了一种测试系统,包括根据第一方面中任一项实施例所述的一种多通道集成芯片测试装置。

22、上述一种多通道集成芯片测试装置,通过权利要求中的技术特征进行推导,能够达到对应背景技术中提出的技术问题的如下的有益效果:

23、本申请提供的一种多通道集成芯片测试装置,包括压载平台、测试模块、控制模块以及对位装置。压载平台用于承载及固定待测模组,测试模块用于与待测模组连接以实现测试信号的传输,控制模块用于实现测试信号的控制,控制模块与测试模块连接,并通过测试模块向待测模组传输所述测试信号,测试信号与待测模组的测试需求相对应,对位装置用于实现待测模组与测试模块的对位控制。在实施中,待测模组放置在压载平台中后,由压载平台承载待测模组并被固定,此时测试模块与待测模组之间在对位装置的控制下,实现自动化地精准对位连接,连接实现后,控制模块根据客户测试需求检测待测模组各pin脚之间连接开路、短路、容抗及阻抗等特性是否符合设计要求,并向待测模组输送,实现自动化地待测模型上料、固定、对位、连接、测试以及下料的流程,有助于提高对待测模组测试的效率,另一方面通过控制模块适应性地输出测试信号,有助于提高测试装置的灵活性。

技术特征:

1.一种多通道集成芯片测试装置,其特征在于,包括:

2.根据权利要求1所述的多通道集成芯片测试装置,其特征在于,所述压载平台包括:

3.根据权利要求2所述的多通道集成芯片测试装置,其特征在于,所述模组盖板包括:转接基板以及fpc测试板,所述fpc测试板在所述模组盖板压合时抵触于所述待测模组,以与所述待测模组连接。

4.根据权利要求2所述的多通道集成芯片测试装置,其特征在于,所述压载平台包括:

5.根据权利要求2所述的多通道集成芯片测试装置,其特征在于,所述压载平台还包括:

6.根据权利要求1所述的多通道集成芯片测试装置,其特征在于,所述测试模块包括:

7.根据权利要求6所述的多通道集成芯片测试装置,其特征在于,所述测试模块包括若干个所述通道选择单元,若干个所述通道选择单元之间呈级联分布。

8.根据权利要求1所述的多通道集成芯片测试装置,其特征在于,所述对位装置包括影像对位单元,所述影像对位单元用于基于所述待测模组的图像数据辅助所述待测模组进行对位连接。

9.根据权利要求8所述的多通道集成芯片测试装置,其特征在于,所述对位装置包括位移单元,所述位移单元用于调节所述影像对位单元的拍摄位姿。

10.一种测试系统,其特征在于,包括根据权利要求1-9中任一项所述的一种多通道集成芯片测试装置。

技术总结

本申请涉及电子电路技术领域,特别是涉及一种多通道集成芯片测试装置以及测试系统。所述多通道集成芯片测试装置包括压载平台,用于承载及固定待测模组;测试模块,用于与所述待测模组连接以实现测试信号的传输;控制模块,用于实现测试信号的控制,所述控制模块与所述测试模块连接,并通过所述测试模块向所述待测模组传输所述测试信号,所述测试信号与所述待测模组的测试需求相对应;对位装置,用于实现所述待测模组与所述测试模块的对位控制。该测试装置能够对不同的待测模组进行快速对位检测,提高了对待测模组的测试效率。

技术研发人员:倪传周,曹振军,严吉新,王宙巍

受保护的技术使用者:苏州华兴源创科技股份有限公司

技术研发日:20240328

技术公布日:2025/3/13

- 还没有人留言评论。精彩留言会获得点赞!