一种微波雷达信号处理机加载与控制电路的制作方法

本发明涉及交会对接微波雷达,具体涉及一种微波雷达信号处理机加载与控制电路。

背景技术:

1、对程序和数据的加载与控制是微波雷达信号处理机的关键技术之一,具体是指通过对单粒子不敏感的反熔丝型fpga对不同处理单元的程序和数据进行加载与控制。在现有的微波雷达信号处理机中,不同处理单元的程序和数据加载与控制由不同的加载与控制芯片、不同的存储芯片分别控制,而这种方式所需硬件资源较多、功耗大、占用空间大、结构复杂,同时对技术状态控制较为复杂。

技术实现思路

1、本发明目的在于一种微波雷达信号处理机加载与控制电路,解决现有的微波雷达信号处理机中加载与控制所需硬件资源较多、功耗大、占用空间大、结构复杂以及对技术状态控制较为复杂等问题。

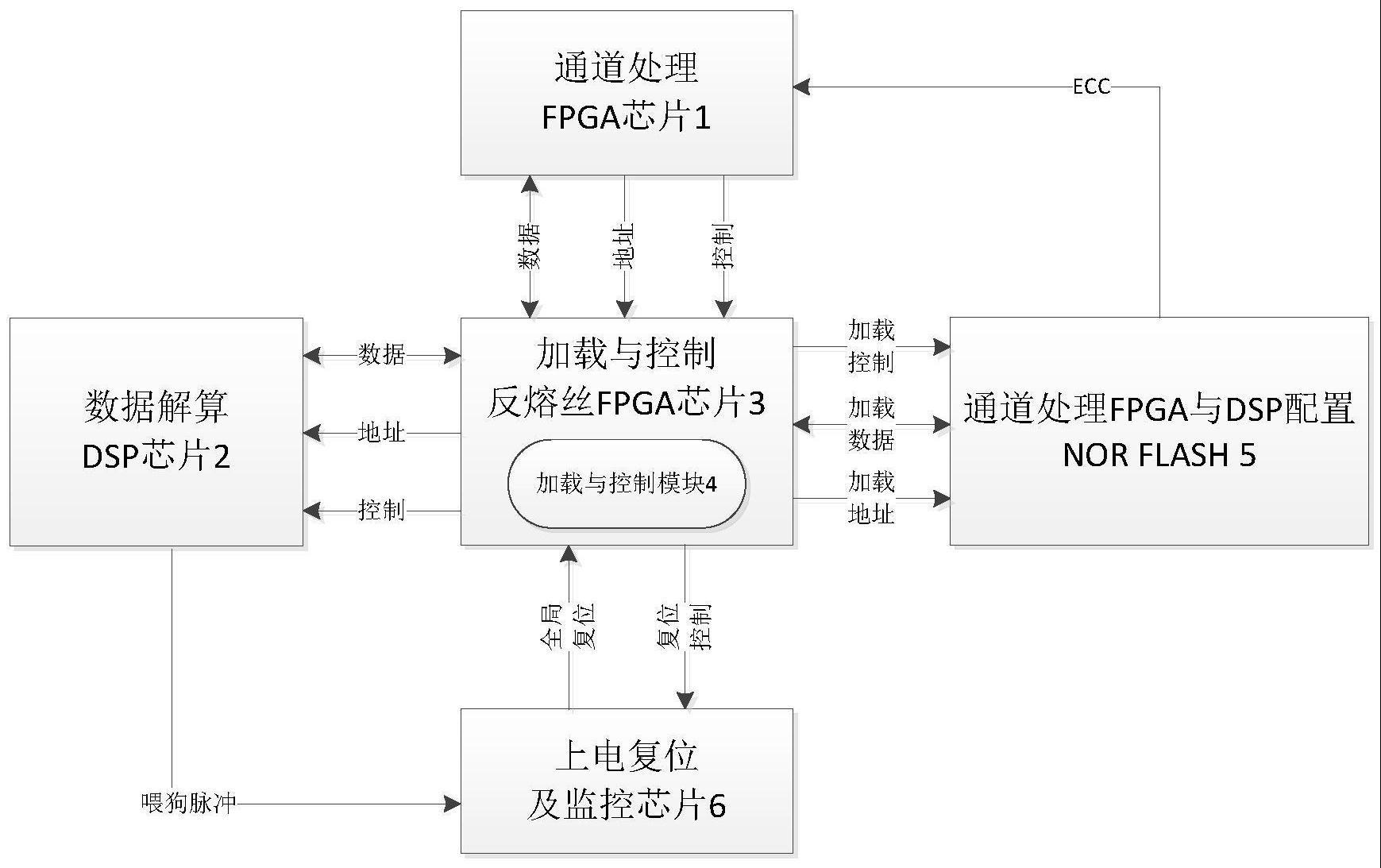

2、对此,本发明提出一种微波雷达信号处理机加载与控制电路,其包括:通道处理fpga芯片、数据解算dsp芯片、加载与控制反熔丝fpga芯片、加载与控制模块、通道处理fpga与数据解算dsp配置nor flash、上电复位及监控芯片。加载与控制模块的功能为:实现对通道处理fpga芯片和数据解算dsp芯片的完全加载控制和动态加载控制、实现对通道处理fpga芯片三通道跟踪数据的环路同步、实现全局复位控制;

3、通道处理fpga与数据解算dsp配置nor flash的加载控制总线输入端与加载与控制反熔丝fpga芯片加载控制总线输出端连接;通道处理fpga与数据解算dsp配置nor flash的加载地址总线输入端与加载与控制反熔丝fpga芯片加载地址总线输出端连接;通道处理fpga与数据解算dsp配置nor flash的加载数据总线输入输出端与加载与控制反熔丝fpga芯片的加载数据总线输出输入端连接;通道处理fpga与数据解算dsp配置nor flash的ecc信号输出端与通道处理fpga芯片的ecc信号输入端连接。

4、通道处理fpga芯片的数据总线输入输出端与加载与控制反熔丝fpga芯片的数据总线输出输入端连接;通道处理fpga芯片的地址总线输出端与加载与控制反熔丝fpga芯片的地址总线输入端连接;通道处理fpga芯片的控制总线输出端与加载与控制反熔丝fpga芯片的控制总线输入端连接。

5、数据解算dsp芯片的数据总线输入输出端与加载与控制反熔丝fpga芯片的数据总线输出输入端连接;数据解算dsp芯片的地址总线输入端与加载与控制反熔丝fpga芯片的地址总线输出端连接;数据解算dsp芯片的控制总线输入端与加载与控制反熔丝fpga芯片的控制总线输出端连接;数据解算dsp芯片的喂狗脉冲输出端与上电复位及监控芯片的喂狗脉冲输入端连接。

6、在一个具体实施方式中,上电复位及监控芯片的全局复位输出端与加载与控制反熔丝fpga芯片的全局复位输入端连接;上电复位及监控芯片的复位控制信号输入端与加载与控制反熔丝fpga芯片的复位控制输出端连接。

7、在一个具体实施方式中,上电后,加载与控制反熔丝fpga芯片开始运行,加载与控制模块开始工作。通道处理fpga芯片与数据解算dsp芯片的程序加载共用一套nor flash的数据总线,以分时复用的方式对这两个芯片进行加载配置。在完成对两个芯片的完全加载后,开始启动对两个芯片的动态加载控制,对通道处理fpga芯片的底层重要寄存器逻辑进行动态定时刷新,对数据解算dsp芯片的程序分区进行定时刷新。加载与控制模块还对通道处理fpga芯片和数据解算dsp芯片的刷新时刻进行逻辑判决,保证按正确的逻辑顺序进行动态刷新。

8、在一个具体实施方式中,加载与控制模块还对通道处理fpga芯片中的三通道跟踪数据进行环路同步,利用三模表决逻辑与出错判决逻辑,判断通道处理fpga芯片的三个跟踪环路状态的一致性。如果有某支路数据与其他两路不一致,加载与控制模块会在下一次动态刷新完成时,产生通道复位信号给通道处理fpga芯片,控制出错通道进行复位,同时产生对应该支路的持续至下一个基准同步脉冲到来的低脉冲给通道处理fpga芯片,由其对该路跟踪环路数据进行预置,以保证跟踪环路数据的可靠性。

9、在一个具体实施方式中,如果三通道跟踪环路数据两两不一致,加载与控制模块将产生通道处理fpga芯片异常标志输出给复位控制电路,由其产生全局复位信号对通道处理fpga芯片的完全重加载。

10、在一个具体实施方式中,当数据解算dsp芯片完全加载后向上电复位及监控芯片发出喂狗信号,用此信号监控数据解算dsp芯片工作是否正常。当数据解算dsp芯片的喂狗信号不正常时,上电复位及监控芯片会向加载与控制反熔丝fpga芯片发出复位信号,通过加载与控制模块实现全局复位。

11、本电路使用一片加载与控制反熔丝fpga芯片实现对通道处理fpga芯片和数据解算dsp芯片的加载与控制,在完全加载后对通道处理fpga芯片进行动态定时刷新,对数据解算dsp芯片进行分区定时刷新,对通道处理fpga芯片中的三通道跟踪数据进行环路同步,保证跟踪数据的可靠性和准确性,提出了一种微波雷达信号处理机加载与控制电路,解决现有的微波雷达信号处理机中加载与控制所需硬件资源较多、功耗大、占用空间大、结构复杂以及对技术状态控制较为复杂等问题。

技术特征:

1.一种微波雷达信号处理机加载与控制电路,其特征在于,所述电路包括:通道处理fpga芯片(1)、数据解算dsp芯片(2)、加载与控制反熔丝fpga芯片(3)、加载与控制模块(4)、通道处理fpga与数据解算dsp配置nor flash(5)以及上电复位及监控芯片(6);

2.根据权利要求1所述的微波雷达信号处理机加载与控制电路,其特征在于,所述上电复位及监控芯片(6)的全局复位输出端与加载与控制反熔丝fpga芯片(3)的全局复位输入端连接;上电复位及监控芯片(6)的复位控制信号输入端与加载与控制反熔丝fpga芯片(3)的复位控制输出端连接。

3.根据权利要求2所述的微波雷达信号处理机加载与控制电路,其特征在于,所述加载与控制模块(4)实现对通道处理fpga(1)和数据解算dsp芯片(2)的完全加载控制和动态加载控制、实现对通道处理fpga芯片(1)三通道跟踪数据的环路同步、实现全局复位控制。

4.根据权利要求3所述的微波雷达信号处理机加载与控制电路,其特征在于,上电后,加载与控制反熔丝fpga芯片(3)开始运行,加载与控制模块(4)开始工作;

5.根据权利要求4所述的微波雷达信号处理机加载与控制电路,其特征在于,所述加载与控制模块(4)还对通道处理fpga芯片(1)中的三通道跟踪数据进行环路同步,利用三模表决逻辑与出错判决逻辑,判断通道处理fpga芯片(1)的三个跟踪环路状态的一致性;如果有某支路数据与其他两路不一致,加载与控制模块(4)会在下一次动态刷新完成时,产生通道复位信号给通道处理fpga芯片(1),控制出错通道进行复位,同时产生对应该支路的持续至下一个基准同步脉冲到来的低脉冲给通道处理fpga芯片(1),由其对该路跟踪环路数据进行预置,以保证跟踪环路数据的可靠性。

6.根据权利要求5所述的微波雷达信号处理机加载与控制电路,其特征在于,如果三通道跟踪环路数据两两不一致,加载与控制模块(4)将产生通道处理fpga芯片(1)异常标志输出给复位控制电路,由其产生全局复位信号对通道处理fpga芯片(1)的完全重加载。

7.根据权利要求6所述的微波雷达信号处理机加载与控制电路,其特征在于,当数据解算dsp芯片(2)完全加载后向上电复位及监控芯片发出喂狗信号,用此信号监控数据解算dsp芯片(2)工作是否正常;当数据解算dsp芯片(2)的喂狗信号不正常时,上电复位及监控芯片(6)会向加载与控制反熔丝fpga芯片(3)发出复位信号,通过加载与控制模块(4)实现全局复位。

技术总结

本发明公开了一种微波雷达信号处理机加载与控制电路,其包括:通道处理FPGA芯片(1)、数据解算DSP芯片(2)、加载与控制反熔丝FPGA芯片(3)、加载与控制模块(4)、通道处理FPGA与数据解算DSP配置NOR FLASH(5)、上电复位及监控芯片(6)。本发明将通道处理FPGA芯片(1)与数据解算DSP芯片(2)的加载与数据流控制用一个模块单元统一协同处理,结合全局复位的方式,提出了一种微波雷达信号处理机加载与控制电路,改进了信号处理机的硬件架构,降低了硬件连接的复杂度和设备功耗,解决了不同处理芯片的协同控制加载问题。

技术研发人员:刘博铭,孙武,黄宜虎,贺中琴,李珍珍,王怡,杨姿蒴

受保护的技术使用者:北京遥感设备研究所

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!