基于射频直采芯片的加速器低电平控制系统数字化方法与流程

本发明涉及粒子回旋加速器的低电平控制系统领域,特别是指一种基于射频直采芯片的加速器低电平控制系统数字化方法。

背景技术:

1、在当前粒子回旋加速器的低电平控制系统中,经常采用射频正弦信号作为加速器系统中的驱动源信号。源信号工作频率较低时(几十mhz以下),可直接采用adc、dac与fpga等芯片进行数字化设计。对于源信号工作频率较高(超过80mhz以上)的低电平控制系统,当前fpga可稳定工作的最高频率受限,可以使用模拟信号或部分数字信号进行混频后实现部分数字化设计,但模拟实现带来了设备复杂、成本高、可靠性差、可维修性差、可生产性差等缺点。此外,现有技术中还有一些采用采样时钟的固定分频作为工作频率的方法,进而实现低电平控制的数字化,但该方式带来了工作频率调整麻烦、适应性差的弊端。

技术实现思路

1、有鉴于此,本发明提出了一种基于射频直采芯片的加速器低电平控制系统数字化方法,该方法利用射频直采芯片实现加速器低电平控制系统的方法,可满足多数加速器低电平控制系统的数字化需求。

2、为了实现上述目的,本发明提供的技术方案是:

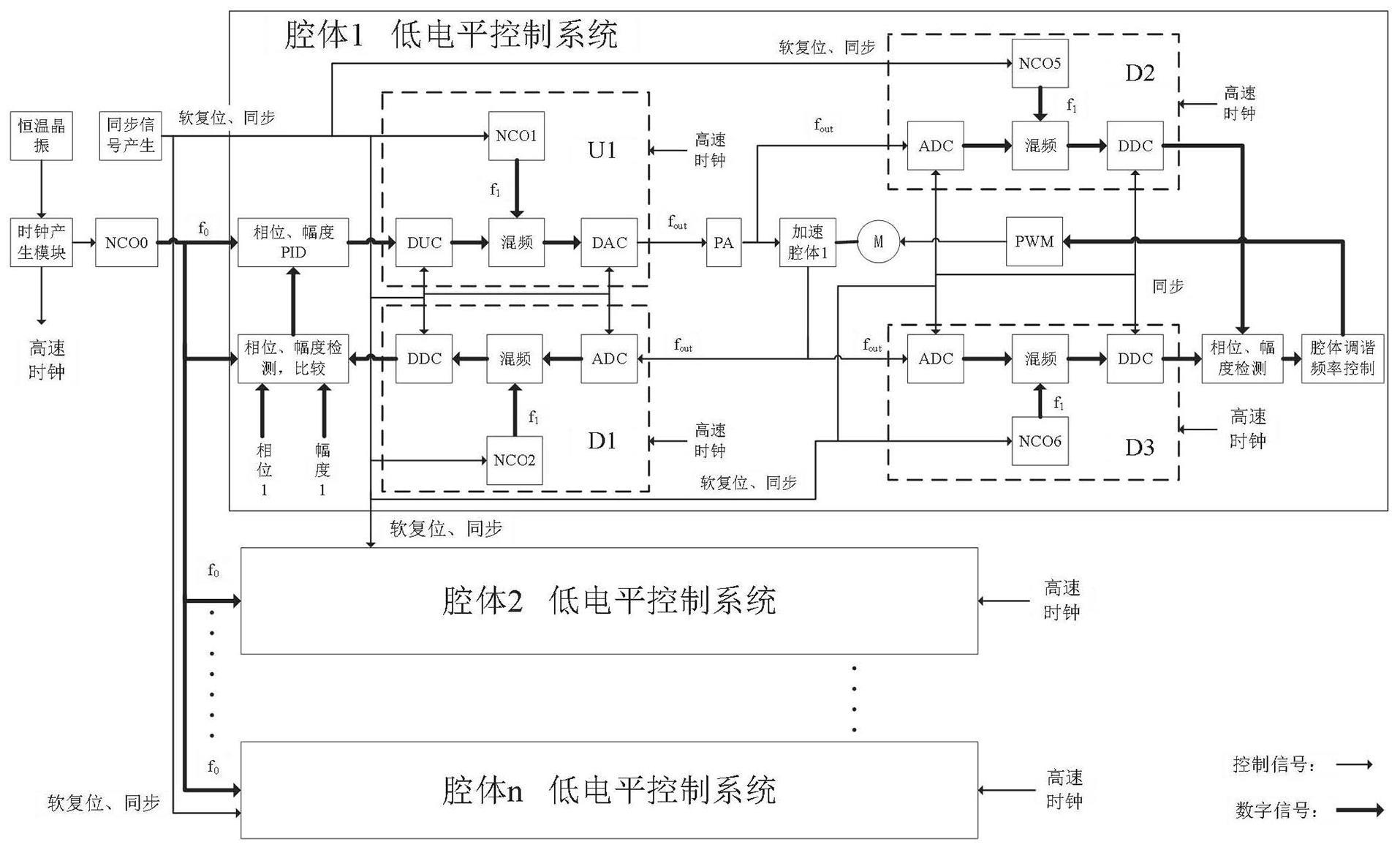

3、一种基于射频直采芯片的加速器低电平控制系统数字化方法,包括以下步骤:

4、(1)恒温晶振驱动时钟模块产生频率与相位关系确定的参考时钟信号与高速时钟信号,参考时钟信号作为各个fpga芯片的系统时钟,高速时钟信号作为射频直采芯片的驱动时钟;各fpga芯片的参考时钟信号频率相同,保持固定的相差;各个射频直采芯片的高速时钟信号频率相同,保持固定的相差;其中高速时钟信号的频率是参考时钟信号频率的整数倍;

5、(2)在fpga内部,参考时钟信号驱动数字控制振荡器产生频率为f0的正交正弦信号,作为各腔体低电平控制系统的fpga内部模块的基准信号;

6、(3)从射频功放或腔体采集的各个频率为fout的采集信号,经过调理后进入射频直采芯片的射频模数转换模块,采集信号由模块内高速模数转换模块直接采样为数字信号;射频模数转换模块内的本振数字控制振荡器产生频率为f1的正交数字本振信号,本振信号与数字采集信号由混频器下混频出频率为f0的正交采集信号,正交采集信号经过降采样后进入fpga;在fpga内部正交采集信号与基准信号进行相位与幅度检测,检测值与相位预置和幅度预置比较后,驱动数字pid控制,输出经过幅相调整的基准控制信号到射频直采芯片;在fpga内部同一路功放与加速器腔体的正交采集信号进行相位与幅度的检测,检测值与预置值比较后计算出腔体调谐频率的控制量,通过pwm功放驱动电机完成腔体调谐频率的调整;

7、(4)在射频直采芯片内的射频数模转换模块内,经过幅相调整的基准控制信号进行数字升采样,射频数模转换模块内的本振数字控制振荡器产生频率为f1的正交本振信号,本振信号与基准控制信号由混频器进行上混频,得到频率为fout的数字控制信号,数字控制信号被高速数模转换模块转换为模拟控制信号,模拟控制信号经过调理后送到射频功放;

8、(5)在fpga内部设计同步模块,在每次启动、复位或工作频率发生变化时,先产生软复位信号再产生同步脉冲信号;在软复位信号后,所有模块的寄存器被复位到确定的状态;在同步脉冲信号后,所有的模块按照预设值开始工作。

9、进一步地,各个射频直采芯片的功能模块的实现方式包括:

10、(1)各个功能模块由软复位信号、同步信号与相差固定的高速时钟信号驱动;

11、(2)所有射频直采芯片内的本振数字控制振荡器产生的正交信号是频率为f1且相差固定的信号;

12、(3)所有降采样倍数与升采样倍数相同,并且保持相位同步;

13、(4)所有射频模数转换模块与射频数模转换模块需要相差固定的高速时钟信号,并同步更新转换的数据。

14、从上面的叙述可以看出,本发明的有益效果在于:

15、1、本发明可采用国产化的射频直采芯片,能够实现工作频率1.2ghz以下的加速器射频低电平控制系统的数字化,可在射频频率几十mhz~1.2ghz范围内的任意频点可靠工作。在此基础上可以构建软件无线电平台,为实现各种模式的低电平控制系统提供基础。

16、2、本发明使用了源信号与低电平控制系统的一体化设计,不需要单独的信号源设计,可以减少模块的数量,降低设备的成本,提高系统的可靠性。

17、3、本发明采用混频法实现射频信号,以频率较低的基准信号在fpga内实现低电平控制,以射频直采芯片内混频实现射频的工作频率,既兼顾了fpga的最高时钟限制,又实现了低电平控制系统的工作频率需求,以此原理制造的设备具有集成化程度高、可生产性好、可靠性高、容易升级等优点。

技术特征:

1.一种基于射频直采芯片的加速器低电平控制系统数字化方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的基于射频直采芯片的加速器低电平控制系统数字化方法,其特征在于,各个射频直采芯片的功能模块的实现方式包括:

技术总结

本发明公开了一种基于射频直采芯片的加速器低电平控制系统数字化方法,属于粒子回旋加速器的低电平控制系统的技术领域。本发明基于FPGA芯片与射频直采芯片实现加速器低电平控制系统数字化,在FPGA芯片内产生较低频率的基准信号,依靠基准信号在FPGA内完成低电平控制系统的相位、幅度与调谐频率的检测与控制,使用射频直采芯片完成基准信号频率与射频工作频率间的搬移,工作频率与时钟不需要固定的倍率关系。本发明能够在射频频率几十MHz~1.2GHz范围内任意频点可靠的工作,可满足多数射频加速器低电平控制系统的数字化需求,是对现有技术的一种重要改进。

技术研发人员:李强,慈国辉,申昱东,杨锁强

受保护的技术使用者:中国电子科技集团公司第五十四研究所

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!