反射内存网络结点与电信号接口转换微秒级时延控制方法

本发明涉及反射内存网络,特别是反射内存网络结点与电信号接口转换的微秒级时延控制方法。

背景技术:

1、随着计算机技术的发展,计算机仿真模型的规模和复杂度越来越大,在成本有限的情况下,使用传统的集中式架构系统进行仿真,资源匮乏、响应速度慢以及服务不完善,尤其是在时间和空间不一致的仿真任务中,集中式架构系统的单一结点通讯以及计算能力有限,难以实现高实时性的仿真效果,不能很好的完成复杂的仿真任务。为了解决上述问题,分布式仿真技术架构应运而生,它将集中式架构的计算和通讯等任务分成一个个互联的独立模块,每个仿真节点可以分布于不同的位置,既可以交互运行也可以独立运行,在降低成本的同时又满足复杂仿真任务对于高实时性的需要,同时还具备高度的灵活性和并发性,每个仿真节点可以自由的参与系统工作和退出系统。

2、反射内存网络广泛应用于半实物分布式仿真技术中,经过多年发展,已经很成熟,具有很多优点:整个传输机制由硬件自动实现,无需软件开发人员理解复杂的数据传输过程,只要对本机内存进行读写操作即可;与设备的操作系统和处理器无关;数据传输稳定且实时性较高等优点。

3、然而,随着仿真技术的广泛应用,半实物分布式仿真系统在实际应用中也遇到两个显著问题:

4、往往分布在不同空间位置中,甚至仿真节点相距可达10公里,这时数据传输延迟会严重影响仿真系统性能;半实物仿真模型和仿真节点设备的通讯接口各式各样,例如数字io、lvds、arinc429、rs422、rs232等通讯接口。传统的综合多种通讯接口的方法为采用计算机接收各通讯接口的数据,再将数据通过软件调度的方式写进内存中,或者将反射内存网络中的数据通过计算机软件调度的方式发送到各通讯接口。在现有计算机性能的基础上,传统的通讯接口综合方法延时较高,系统实时性下降,不能满足强实时性的需求,且节点设备系统的运行状况直接影响到整个仿真系统的稳定性,具有较高的风险性。

5、上述两个问题严重影响了反射内存网络在半实物仿真系统的发展,为了进一步适应新的需要,需要设计新的方法解决上述问题。

技术实现思路

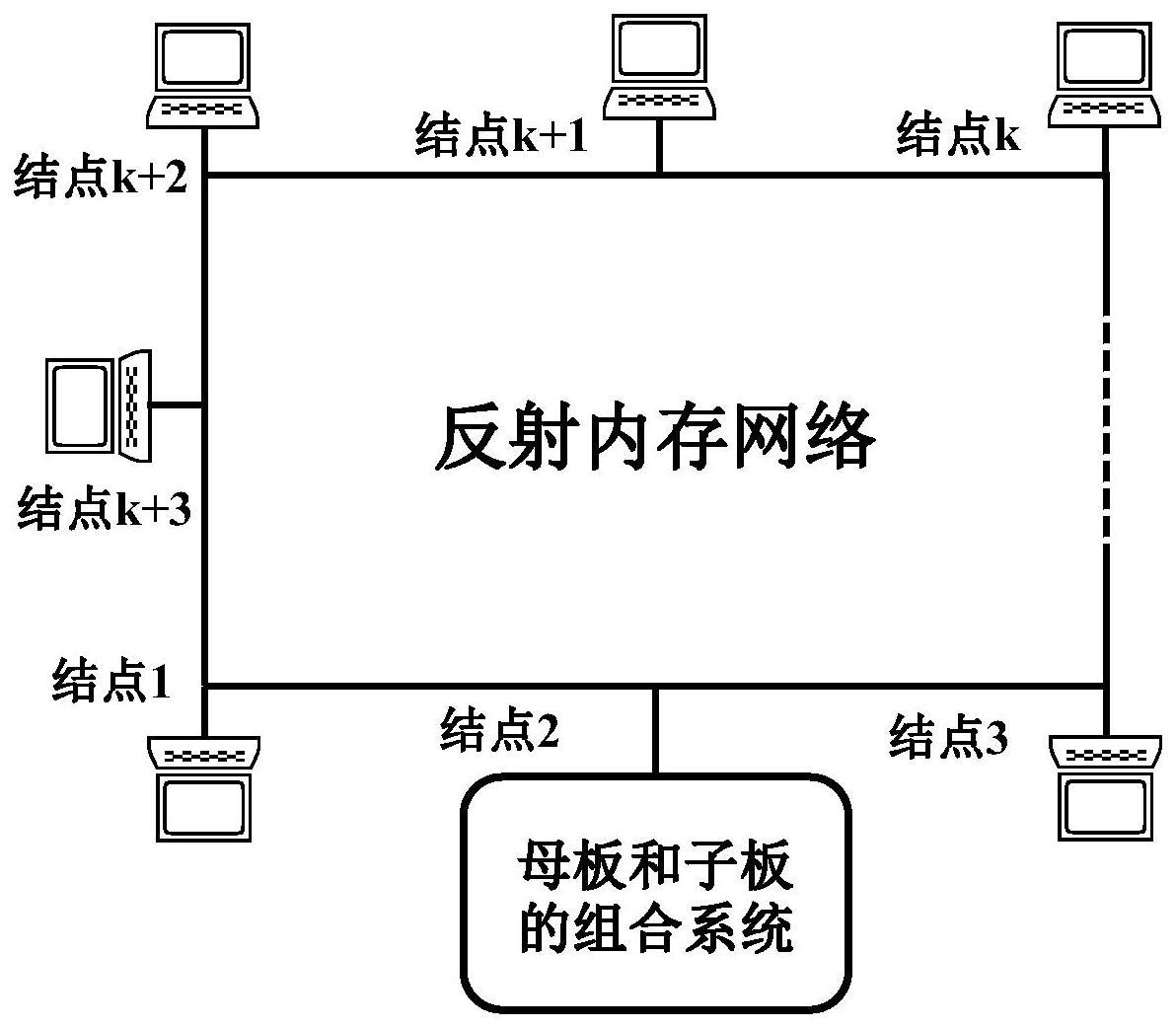

1、针对上述技术问题,本发明提出一种反射内存网络结点与电信号接口转换的微秒级时延控制方法,来解决半实物仿真系统的数据远距离传输和综合多种电信号接口的实时性问题。

2、本发明提供的反射内存网络结点与电信号接口转换的微秒级时延控制方法如下:

3、(s1)以fpga为控制核心平台,构建母板与多种子板组合的硬件系统;其中,整个系统为反射内存网络的一个结点,母板负责反射内存网络协议的解析、对本地数据帧的处理以及与子板的通信;子板包括lvds子板、arinc429子板、rs422子板、rs232子板、1553b子板、a/d采集和d\a输出子板、数字io子板,用于实现各个电信号通道的收发控制与母板通信,子板和母板之间通过xmc接口进行物理连接,选用基于gtx的aurora高速串行总线进行通信。

4、(s2)系统上电后完成初始化:母板各通道进入有限状态机的初始状态,各子板完成基本配置并开启数据收发通道,开始等待数据。

5、(s3)数据接收:当子板通道接收到的数据长度满足预设值后,将收到的数据转化为gtx帧,通过gtx将数据发送到母板的fpga中,将其编码为反射内存网络数据后,通过光纤接口发送到反射内存网络中。

6、(s4)数据发送:反射内存网络向子板的指定通道发送数据,母板fpga对数据进行判定后,将其写入母板fpga对应通道的发送fifo内,当数据长度达到预设值后,母板fpga将该数据转化为gtx帧,通过gtx通道将数据发送到对应子板,子板再将数据进行处理后发送出去。

7、优选地,多通道指多种电信号通道,包括数字io、lvds、arinc429、rs422、rs232、1553b、a/d采集接口和d\a输出接口,各子板选取fpga芯片作数据收发接口的运算处理平台,采用verilog hdl作为编程语言。

8、优选地,母板与子板的物理通道采用1对gtx信号线、2对备用lvds信号线和9个单端信号线,9个单端信号线包括2个状态指示信号线、1个复位信号线和6个备用单端信号线。子母板进行通讯时,先通过状态信号线读取对方状态,当为空闲时,进行通讯;反之,则等待。

9、优选地,母板的运行状态基于有限状态机实现,当没有数据收发时,整个硬件系统处于初始状态,等待数据到来;当有数据进行收发时,母板根据需求和优先级高低进入数据接收状态或者数据发送状态;当数据接收或者数据发送完成时,回到初始状态,继续等待数据。

10、优选地,母板与子板通信的gtx帧为固定格式,当格式不符合时,丢弃该帧;母板对子板每发送一个gtx帧时,子板都要返回一个gtx返回帧。

11、优选地,计算系统时延时,从一个子板的电信号通道完全接收到一个数据包为起始,到通过反射内存网络接口完全发送为终止。

12、优选地,当某个通道同时有数据接收和数据发送时,母板根据需求预先设定的优先级进入优先级高的状态,即如果数据接收优先级高于数据发送优先级,则先进入数据接收状态,完成后进入数据发送状态;反之,则先进入数据发送状态,完成后进入数据接收状态。

13、优选地,固定格式的gtx帧第一位为固定的32bit帧头;第二位为16bit的cmd命令字;第三位为16bit数据长度帧;第四位为由数据长度帧决定其长度的data帧;第五位为32bit的校验位;第六位为固定的32bit帧尾。

14、优选地,gtx返回帧的cmd命令字包括操作命令和操作的寄存器地址两个部分。

15、优选地,gtx帧的cmd命令字包含读写命令、数据无效位数和命令操作的寄存器地址三部分信息。

16、与现有技术相比,本发明的有益效果是:将反射内存网络与电信号接口转换系统嵌入反射内存网络结点中,直接使用光纤进行数据传输,传输距离可达10km;通过硬件的方式实现反射内存网络结点与电信号接口的通讯,具有较强的实时性,最低时延在微秒级;通过verilog hdl语言对fpga编程实现,具有高度的灵活性:在满足强实时性的基础上,可以根据不同应用场合的不同需求对各子板电信号接口的协议进行定制;自定义的gtx帧协议,在尽可能降低时延的基础上,实现子母板通信的高可靠性;采用子母板拼接的方式构成整个硬件架构,在物理结构上具有高度的可拓展性。

技术特征:

1.一种反射内存网络结点与电信号接口转换微秒级时延控制方法,其特征在于,包括如下步骤:

2.根据权利要求1所述的一种反射内存网络结点与电信号接口转换微秒级时延控制方法,其特征在于:多通道指多种电信号通道,包括数字io、lvds、arinc429、rs422、rs232、1553b、a/d采集接口和d\a输出接口,各子板选取fpga芯片作数据收发接口的运算处理平台,采用verilog hdl作为编程语言。

3.根据权利要求1所述的一种反射内存网络结点与电信号接口转换微秒级时延控制方法,其特征在于:母板与子板的物理通道采用1对gtx信号线、2对备用lvds信号线和9个单端信号线,9个单端信号线包括2个状态指示信号线、1个复位信号线和6个备用单端信号线;子母板进行通讯时,先通过状态信号线读取对方状态,当为空闲时,进行通讯;反之,则等待。

4.根据权利要求1或3所述的一种反射内存网络结点与电信号接口转换微秒级时延控制方法,其特征在于:母板的运行状态基于有限状态机实现,当没有数据收发时,整个硬件系统处于初始状态,等待数据到来;当有数据进行收发时,母板根据需求和优先级高低进入数据接收状态或者数据发送状态;当数据接收或者数据发送完成时,回到初始状态,继续等待数据。

5.根据权利要求4所述的一种反射内存网络结点与电信号接口转换微秒级时延控制方法,其特征在于:母板与子板通信的gtx帧为固定格式,当格式不符合时,丢弃该帧;母板对子板每发送一个gtx帧时,子板都要返回一个gtx返回帧。

6.根据权利要求1或5所述的一种反射内存网络结点与电信号接口转换微秒级时延控制方法,其特征在于:计算系统时延时,从一个子板的电信号通道完全接收到一个数据包为起始,到通过反射内存网络接口完全发送为终止。

7.根据权利要求6所述的一种反射内存网络结点与电信号接口转换微秒级时延控制方法,其特征在于:当某个通道同时有数据接收和数据发送时,母板根据需求预先设定的优先级进入优先级高的状态,即如果数据接收优先级高于数据发送优先级,则先进入数据接收状态,完成后进入数据发送状态;反之,则先进入数据发送状态,完成后进入数据接收状态。

8.根据权利要求1所述的一种反射内存网络结点与电信号接口转换微秒级时延控制方法,其特征在于:固定格式的gtx帧第一位为固定的32bit帧头;第二位为16bit的cmd命令字;第三位为16bit数据长度帧;第四位为由数据长度帧决定其长度的data帧;第五位为32bit的校验位;第六位为固定的32bit帧尾。

9.根据权利要求5所述的一种反射内存网络结点与电信号接口转换微秒级时延控制方法,其特征在于:gtx返回帧的cmd命令字包括操作命令和操作的寄存器地址两个部分。

10.根据权利要求1或8所述的一种反射内存网络结点与电信号接口转换微秒级时延控制方法,其特征在于:gtx帧的cmd命令字包含读写命令、数据无效位数和命令操作的寄存器地址三部分信息。

技术总结

本发明提出一种反射内存网络结点与电信号接口转换微秒级时延控制方法,包括如下步骤:步骤一:以FPGA为控制核心平台,构建母板与多种子板组合的硬件系统;步骤二:母板各通道进入有限状态机的初始状态,各子板完成基本配置并开启数据收发通道,开始等待数据;步骤三:当子板通道接收到的数据长度满足预设值后,将收到的数据转化为GTX帧,通过GTX将数据发送到母板的FPGA中,将其编码为反射内存网络数据后,通过光纤接口发送到反射内存网络中;步骤四:反射内存网络向子板的指定通道发送数据,母板FPGA对数据进行判定后,将其写入母板FPGA对应通道的发送FIFO内。本发明能解决半实物仿真系统的数据远距离传输和综合多种电信号接口的实时性问题。

技术研发人员:周强

受保护的技术使用者:北京航空航天大学

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!