电压源电路的制作方法

本发明涉及一种半导体集成电路,特别是涉及一种电压源电路。

背景技术:

1、如图1所示,是现有电压源电路电路图,电流源提供的电流i1,电流源连接电源电压vcc,电流i1流经nmos管nm100、pmos管pm100、nmos管nm102并接地vss,其中nmos管nm100为本征(native)nmos管,在节点ndr处产生的钳位(clamp)电压为vgs_n+vgs_p+vgs_nz。

2、其中,vgs_n表示二极管连接的nmos管nm102的栅源电压,vgs_p表示二极管连接的pmos管pm100的栅源电压,vgs_n表示二极管连接的本征的nmos管nm100的栅源电压。

3、native nmos管组成的nmos管nm101为驱动管,通常其尺寸会很大,nmos管nm103的栅极连接到nmos管nm102的栅极即节点nbias,nmos管nm103会镜像nmos管nm102的电流作为nmos管nm101的内部负载电流,产生的输出电压vdd为vgs_n+vgs_p+vgs_nz-vgs_nzp,vgs_nzp表示二极管连接的本征的nmos管nm101的栅源电压。

4、图1所示的电压源为开环结构,当输出电压vdd上重载时即连接外部负载的负载电流较大时,钳位电压作为驱动电压用以驱动nmos管nm101。由于节点ndr处的驱动电压不变,负载电流较大时,nmos管nm101需要更大的vgs,所以输出电压vdd会被拉低。

技术实现思路

1、本发明所要解决的技术问题是提供一种电压源电路,能防止输出电压随负载电流增加而降低。

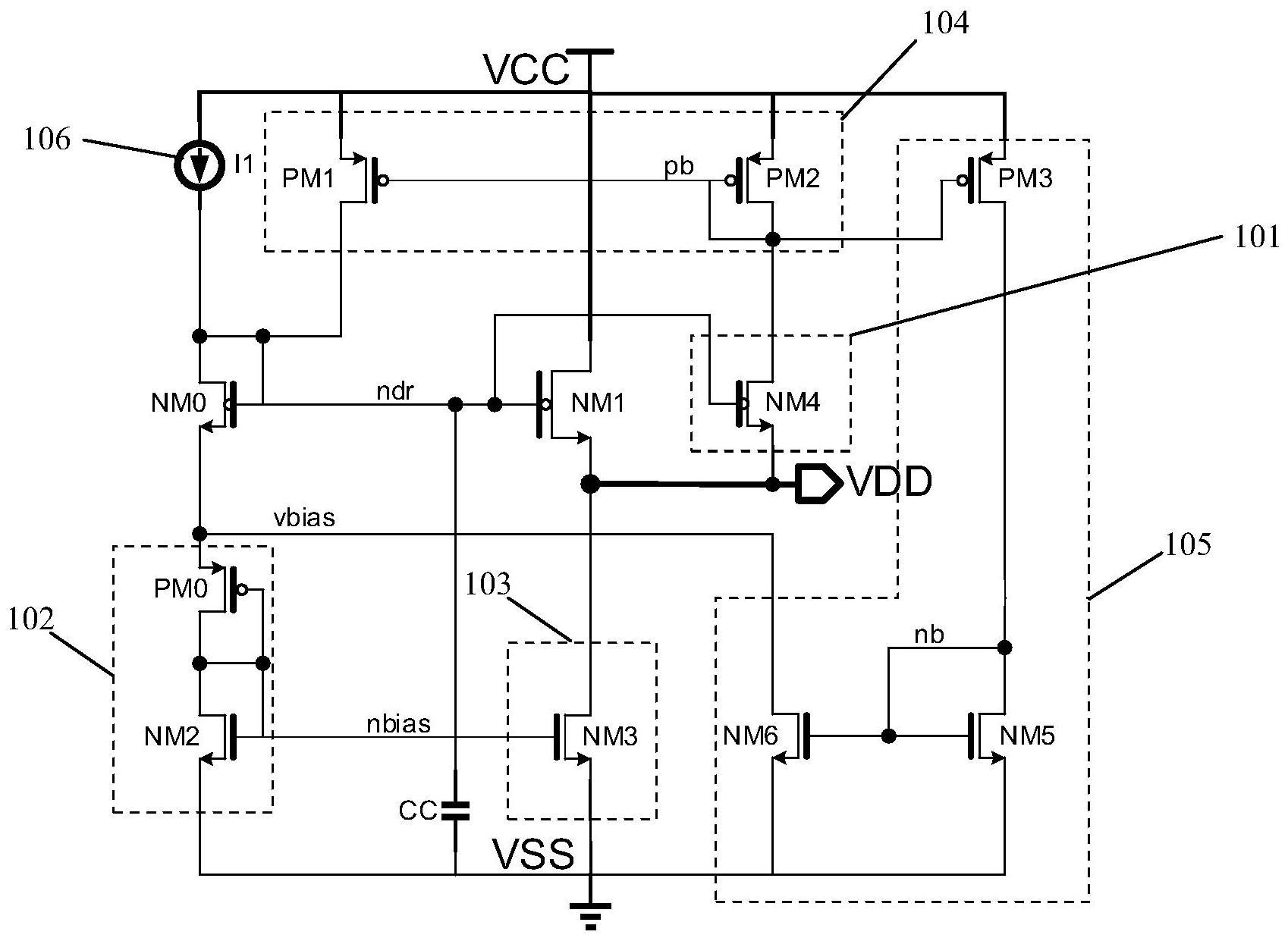

2、为解决上述技术问题,本发明提供的电压源电路包括:

3、第一nmos管,所述第一nmos管的源极和地之间连接有第一下拉路径,所述第一nmos管的栅极输出驱动电压。

4、所述第一下拉路径具有多个二极管连接的mos晶体管;所述第一nmos管的栅极连接漏极,所述第一nmos管的漏极连接第一电流源,所述第一电流源提供固定大小的第一输入电流。

5、由第二nmos管组成的驱动管,所述驱动管的栅极连接所述驱动电压,所述驱动管的源极为输出电压的输出端;所述驱动管的漏极连接电源电压;所述驱动管的源极和地之间连接有第二下拉路径,所述第二下拉路径和所述第一下拉路径互为镜像;所述输出电压用于提供外部负载,所述驱动管的源漏电流随负载电流的增加而增加。

6、负反馈路径,包括:

7、采样管,所述采样管的源漏电流为采样电流,所述采样电流为所述驱动管的源漏电流的镜像电流。

8、第一镜像电路,所述第一镜像电路提供第二输入电流,所述第二输入电流为所述采样电流的镜像电流,所述第二输入电流输入到所述第一nmos管的漏极;

9、所述第一nmos管的源漏电流由所述第一输入电流和所述第二输入电流叠加而成;当所述负载电流增加时,所述第二输入电流也增加,使所述第一nmos管的源漏电流也增加并从而使所述第一nmos管的栅源电压增加,从而提升所述第一nmos管的栅极输出的所述驱动电压,从而提高所述驱动管的驱动能力,防止所述输出电压随所述负载电流增加而降低。

10、进一步的改进是,所述负反馈路径还包括第二镜像电路;所述第二镜像电路提供第三抽取电流,所述第三抽取电流为所述采样电流的镜像电流,所述第三抽取电流连接到所述第一nmos管的源极。

11、进一步的改进是,所述第一下拉路径包括第四nmos管和第一pmos管。

12、所述第四nmos管的源极接地,所述第一pmos管的源极连接所述第一nmos管的源极。

13、所述第四nmos管的栅极和漏极连接所述第一pmos管的栅极和漏极。

14、进一步的改进是,所述第二下拉路径包括第五nmos管,所述第五nmos管的源极接地,所述第五nmos管的漏极连接所述第二nmos管的源极;

15、所述第五nmos管的栅极连接所述第四nmos管的栅极。

16、进一步的改进是,所述采样管包括第三nmos管;

17、所述第三nmos管的源极连接所述第二nmos管的源极;

18、所述第三nmos管的栅极连接所述第二nmos管的栅极。

19、进一步的改进是,所述第一镜像电路包括第二pmos管和第三pmos管。

20、所述第二pmos管的漏极和栅极以及所述第三pmos管的栅极都连接所述第三nmos管的漏极。

21、所述第二pmos管的源极和所述第三pmos管的源极都连接电源电压。

22、所述第三pmos管的源极连接所述第一nmos管的漏极。

23、所述第二pmos管的源漏电流等于所述采样电流,所述第三pmos管的源漏电流为所述第二输入电流。

24、进一步的改进是,所述第二镜像电路包括第四pmos管、第六nmos管和第七nmos管。

25、所述第四pmos管的栅极连接所述第二pmos管的栅极。

26、所述第四pmos管的源极连接电源电压。

27、所述第四pmos管的漏极、所述第六nmos管的漏极和栅极以及所述第七nmos管的栅极连接在一起。

28、所述第六nmos管的源极和所述第七nmos管的源极都接地。

29、所述第七nmos管的漏极连接所述第一nmos管的源极。

30、所述第四pmos管的源漏电流为所述采样电流的镜像电流且等于所述第六nmos管的源漏电流。

31、所述第七nmos管的源漏电流为所述第三抽取电流且为所述第六nmos管的源漏电流的镜像电流。

32、进一步的改进是,所述第三抽取电流的大小设置为小于等于所述第二输入电流,使所述第一下拉路径的电流大于等于所述第一输入电流。

33、进一步的改进是,在所述第二nmos管的栅极和地之间连接有补偿电容。

34、进一步的改进是,所述第二nmos管采用本征nmos管。

35、进一步的改进是,所述第一nmos管采用本征nmos管。

36、进一步的改进是,所述第二nmos管的沟道尺寸大于所述第一nmos管的沟道尺寸。

37、进一步的改进是,所述输出电压为数v以下。

38、进一步的改进是,所述负载电流的最大值达数百微安。

39、本发明通过设置采样管采样驱动管的源漏电流从而能实时采用负载电流,通过得到的采样电流进行反馈能使驱动管的驱动电压增加,驱动电压增加后,由于驱动管的源漏电流是由栅极连接的驱动电压和源极输出的输出电压的差即栅源电压决定,故当驱动电压增加后,能使输出电压不降低的条件下使驱动管的栅源电压增加,从而能实现在负载电流增加使驱动管的源漏电流增加时使输出电压不降低,所以,本发明能防止输出电压随负载电流增加而降低,提高了对大负载电流的驱动能力。

技术特征:

1.一种电压源电路,其特征在于,包括:

2.如权利要求1所述的电压源电路,其特征在于:所述负反馈路径还包括第二镜像电路;所述第二镜像电路提供第三抽取电流,所述第三抽取电流为所述采样电流的镜像电流,所述第三抽取电流连接到所述第一nmos管的源极。

3.如权利要求2所述的电压源电路,其特征在于:所述第一下拉路径包括第四nmos管和第一pmos管;

4.如权利要求3所述的电压源电路,其特征在于:所述第二下拉路径包括第五nmos管,所述第五nmos管的源极接地,所述第五nmos管的漏极连接所述第二nmos管的源极;

5.如权利要求2所述的电压源电路,其特征在于:所述采样管包括第三nmos管;

6.如权利要求5所述的电压源电路,其特征在于:所述第一镜像电路包括第二pmos管和第三pmos管;

7.如权利要求6所述的电压源电路,其特征在于:所述第二镜像电路包括第四pmos管、第六nmos管和第七nmos管;

8.如权利要求2或7所述的电压源电路,其特征在于:所述第三抽取电流的大小设置为小于等于所述第二输入电流,使所述第一下拉路径的电流大于等于所述第一输入电流。

9.如权利要求2或7所述的电压源电路,其特征在于:在所述第二nmos管的栅极和地之间连接有补偿电容。

10.如权利要求1所述的电压源电路,其特征在于:所述第二nmos管采用本征nmos管。

11.如权利要求10所述的电压源电路,其特征在于:所述第一nmos管采用本征nmos管。

12.如权利要求11所述的电压源电路,其特征在于:所述第二nmos管的沟道尺寸大于所述第一nmos管的沟道尺寸。

13.如权利要求1所述的电压源电路,其特征在于:所述输出电压为数v以下。

14.如权利要求1所述的电压源电路,其特征在于:所述负载电流的最大值达数百微安。

技术总结

本发明公开了一种电压源电路,包括:第一NMOS管,源极和地之间连接有第一下拉路径,栅极输出驱动电压,第一下拉路径具有多个二极管连接的MOS晶体管;第一NMOS管的栅极连接漏极并连接第一电流源;由第二NMOS管组成的驱动管,栅极连接所述驱动电压,源极为输出电压的输出端,源极和地之间连接有和第一下拉电路镜像的第二下拉路径。负反馈路径,包括:采样管,采样驱动管的源漏电流;第一镜像电路,提供第二输入电流输入到第一NMOS管的漏极;所述第一NMOS管的源漏电流由所述第一输入电流和所述第二输入电流叠加而成,当负载电流增加时,第二输入电流也增加并使驱动电压增加,防止输出电压降低。本发明能防止输出电压随负载电流增加而降低。

技术研发人员:周宁,陈涛

受保护的技术使用者:普冉半导体(上海)股份有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!