带隙基准电路正常工作检测的标识电路的制作方法

本申请涉及集成电路,特别涉及一种带隙基准电路正常工作检测的标识电路。

背景技术:

1、随着cmos工艺的进步,集成电路已经发展到系统级芯片(system on chip,soc)的阶段,由于cmos电路的低成本,低功耗以及工作速度的不断提高,cmos电路设计技术得到不断的进步,已经被证明是实现soc的最好选择。带隙基准电路作为其中不可或缺的一个模块,一直以来是研究的热点,基准源是与电源、工艺、温度的关系很小,其精度及稳定性对系统有较大的影响。因此,需要对带隙基准电路做出监测,如果遇到极端条件,使得带隙基准电路精度受到影响时,需要及时发出指示信号,告知系统。

技术实现思路

1、本申请的目的在于提供一种带隙基准电路正常工作检测的标识电路,能自适应温度和电源电压对带隙基准电路中的输入对管和三极管的变化,从而给出准确的标识信号。

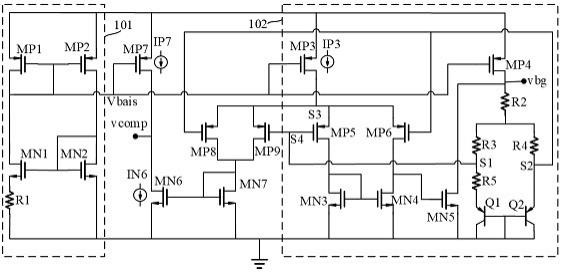

2、本申请公开了一种带隙基准电路正常工作检测的标识电路,包括:偏置电流源、带隙基准电路、第七pmos晶体管、第七pmos晶体管、第九pmos晶体管、以及第六nmos晶体管和第七nmos晶体管,所述带隙基准电路包括第三pmos晶体管、第四pmos晶体管、第五pmos晶体管、第六pmos晶体管、第三nmos晶体管、第四nmos晶体管、第五nmos晶体管、第二电阻、第三电阻、第四电阻、第五电阻、以及第一三极管和第二三极管;其中,

3、所述第三pmos晶体管、第四pmos晶体管和第七pmos晶体管的源极均耦合到电源,栅极均耦合到所述偏置电流源输出的偏置电压,所述第四pmos晶体管的漏极耦合到所述第二电阻的一端和所述第五nmos晶体管的漏极,所述第二电阻的另一端同时耦合到所述第三电阻和第四电阻的一端,所述第三电阻的另一端经由第五电阻耦合到所述第一三极管的发射极,所述第一三极管和第二三极管的基极和集电极均相连并耦合到地端,所述第五nmos晶体管的栅极耦合到所述第四nmos晶体管的漏极和第六pmos晶体管的漏极,所述第四电阻的另一端耦合到所述第二三极管的发射极和所述第八pmos晶体管的栅极,所述第五pmos晶体管、第六pmos晶体管、第八pmos晶体管和第九pmos晶体管的源极均耦合到所述第三pmos晶体管的漏极,所述第五pmos晶体管的漏极耦合到所述第三nmos晶体管的漏极和栅极以及所述第四nmos晶体管栅极,所述第三电阻和第五电阻之间的节点耦合到所述第五pmos晶体管和第九pmos晶体管的栅极,所述第八pmos晶体管和第九pmos晶体管的漏极均耦合到所述第七nmos晶体管的漏极和栅极以及所述第六nmos晶体管的栅极,所述第六nmos晶体管的漏极耦合到所述第七pmos晶体管的漏极,所述第三nmos晶体管、第四nmos晶体管、第五nmos晶体管、第六nmos晶体管和第七nmos晶体管的源极均耦合到地端。

4、在一个优选例中,所述偏置电流源包括第一pmos晶体管和第二pmos晶体管、第一nmos晶体管和第二nmos晶体管、以及第一电阻,其中,所述第一pmos晶体管和第二pmos晶体管的源极耦合到电源,所述第一pmos晶体管的漏极和栅极、第二pmos晶体管的栅极、以及所述第一nmos晶体管的漏极相连并输出所述偏置电压,所述第一nmos晶体管的栅极、所述第一pmos晶体管的漏极、以及所述第二nmos晶体管的漏极和栅极相连,所述第一nmos晶体管的源极经由所述第一电阻耦合到地端,所述第二nmos晶体管的源极耦合到地端。

5、在一个优选例中,当所述电源的电压低于所述带隙基准电路的最小工作电压时,所述第三pmos晶体管的电流减小,使得所述第三pmos晶体管的电流通过所述第八pmos晶体管和第九pmos晶体管以及第七nmos晶体管镜像到所述第六nmos晶体管的电流减小,所述第六nmos晶体管的漏极电流低于所述第七pmos晶体管的漏极电流,使得所述第六nmos晶体管的漏极和所述第七pmos晶体管的漏极输出指示信号。

6、在一个优选例中,所述带隙基准电路的最小工作电压为vbe_q2+vgs_mp6+vds_mp3,其中vbe_q2为所述第二三极管的发射极和基极之间的电压差,vgs_mp6为所述第六pmos晶体管的栅源电压,vds_mp3为所述第三pmos晶体管的漏极和源极之间的电压差。

7、在一个优选例中,所述偏置电流源的最小工作电压低于所述带隙基准电路的最小工作电压。

8、在一个优选例中,所述偏置电流源的最小工作电压为vgs_mp1+vds_mn1+vr1或者vgs_mn2+vds_mp2,其中,vgs_mp1为所述第一pmos晶体管的栅源电压,vds_mn1为所述第一nmos晶体管的漏极和源极之间的电压差,vr1为所述第一电阻两端的电压差,vgs_mn2为所述第二nmos晶体管的栅源电压,vds_mp2为所述第二pmos晶体管的漏极和源极之间的电压差。

9、在一个优选例中,所述第一三极管和第二三极管为pnp三极管。

10、本申请实施方式中,当温度降低,带隙基准电路中三级管的发射极和基极之间的电压差增加,而电源电压又较低,不能满足带隙基准电路所要求的最低电源电压时,使得第三pmos晶体管的电流通过第八pmos晶体管和第九pmos晶体管以及第七nmos晶体管镜像到第六nmos晶体管的电流减小,将第六nmos晶体管的漏极和第七pmos晶体管的漏极电压比较从而能够给出准确的标识信号,告知系统此时的基准电压已经不能满足精度要求。本申请能够能自适应温度和电源电压对输入对管和三极管的变化,从而给出准确的标识信号。

11、本申请的说明书中记载了大量的技术特征,分布在各个技术方案中,如果要罗列出本申请所有可能的技术特征的组合(即技术方案)的话,会使得说明书过于冗长。为了避免这个问题,本申请上述

技术实现要素:

中公开的各个技术特征、在下文各个实施方式和例子中公开的各技术特征、以及附图中公开的各个技术特征,都可以自由地互相组合,从而构成各种新的技术方案(这些技术方案均应该视为在本说明书中已经记载),除非这种技术特征的组合在技术上是不可行的。例如,在一个例子中公开了特征a+b+c,在另一个例子中公开了特征a+b+d+e,而特征c和d是起到相同作用的等同技术手段,技术上只要择一使用即可,不可能同时采用,特征e技术上可以与特征c相组合,则,a+b+c+d的方案因技术不可行而应当不被视为已经记载,而a+b+c+e的方案应当视为已经被记载。

技术特征:

1.一种带隙基准电路正常工作检测的标识电路,其特征在于,包括:偏置电流源、带隙基准电路、第七pmos晶体管、第八pmos晶体管、第九pmos晶体管、以及第六nmos晶体管和第七nmos晶体管,所述带隙基准电路包括第三pmos晶体管、第四pmos晶体管、第五pmos晶体管、第六pmos晶体管、第三nmos晶体管、第四nmos晶体管、第五nmos晶体管、第二电阻、第三电阻、第四电阻、第五电阻、以及第一三极管和第二三极管;其中,

2.如权利要求1所述的带隙基准电路正常工作检测的标识电路,其特征在于,所述偏置电流源包括第一pmos晶体管和第二pmos晶体管、第一nmos晶体管和第二nmos晶体管、以及第一电阻,其中,所述第一pmos晶体管和第二pmos晶体管的源极耦合到电源,所述第一pmos晶体管的漏极和栅极、第二pmos晶体管的栅极、以及所述第一nmos晶体管的漏极相连并输出所述偏置电压,所述第一nmos晶体管的栅极、所述第一pmos晶体管的漏极、以及所述第二nmos晶体管的漏极和栅极相连,所述第一nmos晶体管的源极经由所述第一电阻耦合到地端,所述第二nmos晶体管的源极耦合到地端。

3.如权利要求2所述的带隙基准电路正常工作检测的标识电路,其特征在于,当所述电源的电压低于所述带隙基准电路的最小工作电压时,所述第三pmos晶体管的电流减小,使得所述第三pmos晶体管的电流通过所述第八pmos晶体管和第九pmos晶体管以及第七nmos晶体管镜像到所述第六nmos晶体管的电流减小,所述第六nmos晶体管的漏极电流低于所述第七pmos晶体管的漏极电流,使得所述第六nmos晶体管的漏极和所述第七pmos晶体管的漏极输出指示信号。

4.如权利要求3所述的带隙基准电路正常工作检测的标识电路,其特征在于,所述带隙基准电路的最小工作电压为vbe_q2+vgs_mp6+vds_mp3,其中vbe_q2为所述第二三极管的发射极和基极之间的电压差,vgs_mp6为所述第六pmos晶体管的栅源电压,vds_mp3为所述第三pmos晶体管的漏极和源极之间的电压差。

5.如权利要求4所述的带隙基准电路正常工作检测的标识电路,其特征在于,所述偏置电流源的最小工作电压低于所述带隙基准电路的最小工作电压。

6.如权利要求5所述的带隙基准电路正常工作检测的标识电路,其特征在于,所述偏置电流源的最小工作电压为vgs_mp1+vds_mn1+vr1或者vgs_mn2+vds_mp2,其中,vgs_mp1为所述第一pmos晶体管的栅源电压,vds_mn1为所述第一nmos晶体管的漏极和源极之间的电压差,vr1为所述第一电阻两端的电压差,vgs_mn2为所述第二nmos晶体管的栅源电压,vds_mp2为所述第二pmos晶体管的漏极和源极之间的电压差。

7.如权利要求1所述的带隙基准电路正常工作检测的标识电路,其特征在于,所述第一三极管和第二三极管为pnp三极管。

技术总结

本申请公开了一种带隙基准电路正常工作检测的标识电路,包括:偏置电流源、带隙基准电路、第七至第九PMOS晶体管、以及第六和第七NMOS晶体管,带隙基准电路包括第三至第六PMOS晶体管、第三至第五NMOS晶体管、第二至第五电阻、以及第一和第二三极管。当电源电压低于基准电路的最低工作电压时,第三PMOS晶体管的电流减少,导致第六NMOS晶体管的漏极电流低于第七PMOS晶体管,输出指示信号通知系统。本申请能自适应温度和电源电压对输入对管和三极管的变化,从而给出准确的标识信号。

技术研发人员:请求不公布姓名

受保护的技术使用者:上海灵动微电子股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!