具有灵活可配置逻辑模块的微控制器的制作方法

本申请涉及微控制器(mcu),特别涉及一种具有灵活可配置逻辑模块的微控制器。

背景技术:

1、本部分旨在为权利要求书中陈述的本申请的实施方式提供背景或上下文。此处的描述不因为包括在本部分中就承认是已被公开的现有技术。

2、在光通讯领域中,光通信模块作为基础设备,数以亿计(只)的需求承载着巨大的市场,其内部信号按速度划分分为:

3、a:高速信号(1000mbps, 10gbps, 25gbps, 100gbps或者更高);

4、b:准高速信号(rx los, tx fault, tx disable, rssi trigger, 50gbps tiarate select等),响应时间需要几纳秒到数十纳秒不等;

5、c:低速信号(微控制器(mcu)串行执行,例如ddm(数字诊断监控):电源电压,温度,发射光功率,接收光功率,ld偏置电流监控),响应时间要求优于50毫秒即可。

6、其中,低速信号处理目前全部由光通信模块厂家选择不同厂家、不同种类的mcu实现;高速信号由专用收发器实现;准高速信号处理电路目前大多由分离器件搭建而成。

7、对于ftth、fttb、fttc应用,由于技术发展不断提速,已经由1.25gbps,2.5gbps,10gbps,25gbps提升到目前最高的50gbps,但是考虑到全面升级的成本压力不符合多样化的供需关系,通常是在一条pon光网络上高低速率共存且时分复用和波分复用。

8、对于25gbps和10gbps pon系统,上行存在1290nm 25gbps数据和1270nm 10gbps数据,即25gspon olt端需要时分复用和波分复用多节点onu端25gbps或10gbps数据,对于25gspon olt端光通信模块由于可能接收不同的速率,需要选择不同apd pin tia跨阻增益来满足光网络的最佳接收灵敏度性能,通过交换机给定的reset和rate select信号,实现高速3电平信号给到跨阻放大器。

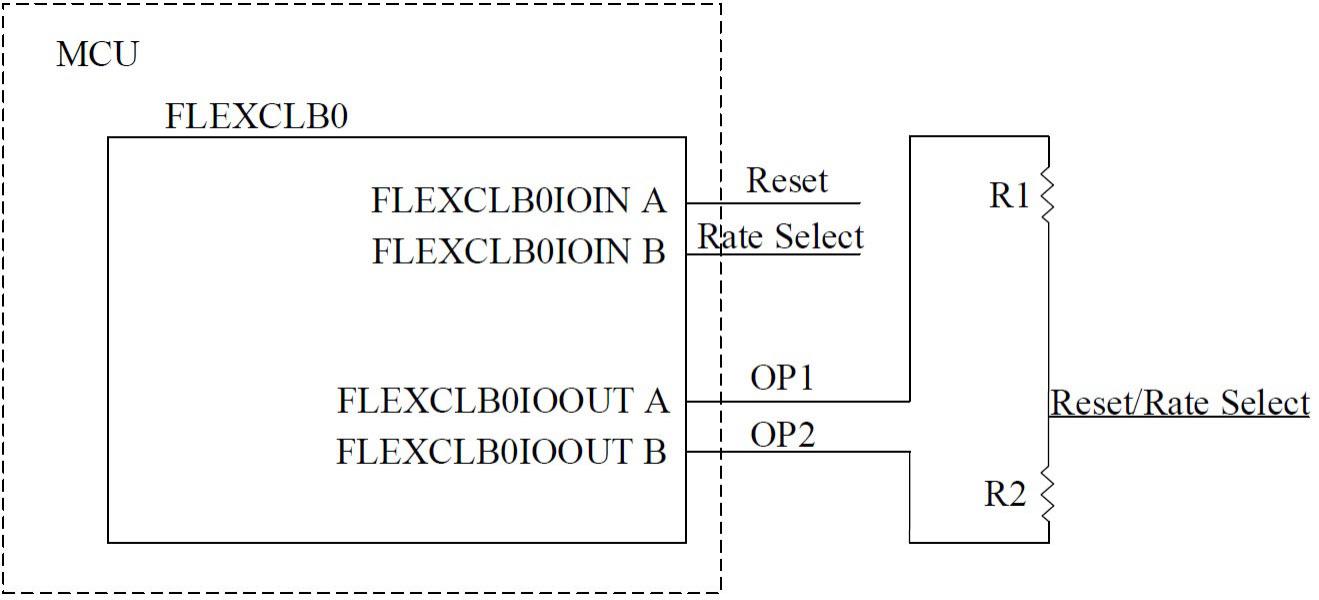

9、传统的实现高速3电平信号方案如图1所示,mcu需要额外的2颗74aup1g97逻辑芯片和两颗滤波电容,压缩了pcb使用面积。

技术实现思路

1、本申请的目的在于提供一种具有灵活可配置逻辑模块(flexclb)的微控制器(mcu),在mcu内部嵌入可配置逻辑模块,提高mcu灵活性,满足mcu高速通讯应用场景。

2、本申请公开了一种具有灵活可配置逻辑模块的微控制器,包括:

3、多个可配置逻辑模块,其中每个可配置逻辑模块具有两个查找表,每个可配置逻辑模块具有一个来自寄存器的输入端口、两个来自mcu输入引脚的输入端口、两个来自其他可配置逻辑模块的输入端口(级联)、以及两个输出端口,所述可配置逻辑模块根据输入端口的值在所述查找表中获得输出端口对应的值并输出;

4、多个输入复用器,其中两个输入复用器分别接收来自所述mcu输入引脚的输出并选择性输出到所述两个可配置逻辑模块,其中两个输入复用器分别接收来自其他可配置逻辑模块的输出并选择性输出到所述两个可配置逻辑模块;

5、两个触发器,所述两个触发器的数据端口各自接收所述两个输出端口的输出值,并且所述两个触发器的时钟端口各自接收微控制器的内部时钟或外部模块输入的时钟;

6、两个输出复用器,所述两个输出复用器各自接收所述两个查找表的直接输出和两个触发器的输出值,实现异步或同步输出;

7、两个解复用器,所述两个解复用器各自接收所述两个输出复用器的输出值并输出到相应mcu输出引脚。

8、在一个优选例中,所述可配置逻辑模块根据两个来自mcu输入引脚输入端口的值分别在所述两个查找表中获得两个输出端口对应的值并输出,其中,所述两个查找表各自通过5比特寄存器配置。

9、在一个优选例中,还包括:第一电阻和第二电阻,所述第一电阻的一端耦合到其中一个输出端口,所述第二电阻的一端耦合到另一个输出端口,所述第一电阻的另一端和第二电阻的另一端相连并输出三电平信号。

10、在一个优选例中,所述第一电阻和第二电阻的阻值相同,均为220个单位电阻值。

11、在一个优选例中,所述两个输出端口的输出值均为低电平时,所述第一电阻的另一端和第二电阻的另一端输出0电平,所述两个输出端口的输出值均为高电平时,所述第一电阻的另一端和第二电阻的另一端输出高电平,所述两个输出端口的输出值中一个为高电平另一个为低电平时,所述第一电阻的另一端和第二电阻的另一端输出中间电平。

12、在一个优选例中,还包括:同步时钟选择器,所述同步时钟选择器接收微控制器的内部时钟或外部模块输入的时钟并选择性输出到所述两个触发器的时钟端口。

13、在一个优选例中,所述微控制器包括至少三个可配置逻辑模块。

14、在一个优选例中,所述微控制器包括至少四个输入复用器。

15、本申请实施方式中,在mcu内部嵌入可配置逻辑模块,完美的整合低速信号和准高速信号,提高mcu灵活性,节省光通信模块本身苛刻的pcb面积难题和高成本难题。

16、本发明将准高速信号处理电路集成于mcu内部,减少外围器件,节约pcb面积,同时提高mcu适用范围。

17、本申请的说明书中记载了大量的技术特征,分布在各个技术方案中,如果要罗列出本申请所有可能的技术特征的组合(即技术方案)的话,会使得说明书过于冗长。为了避免这个问题,本申请上述

技术实现要素:

中公开的各个技术特征、在下文各个实施方式和例子中公开的各技术特征、以及附图中公开的各个技术特征,都可以自由地互相组合,从而构成各种新的技术方案(这些技术方案均应该视为在本说明书中已经记载),除非这种技术特征的组合在技术上是不可行的。例如,在一个例子中公开了特征a+b+c,在另一个例子中公开了特征a+b+d+e,而特征c和d是起到相同作用的等同技术手段,技术上只要择一使用即可,不可能同时采用,特征e技术上可以与特征c相组合,则,a+b+c+d的方案因技术不可行而应当不被视为已经记载,而a+b+c+e的方案应当视为已经被记载。

技术特征:

1.一种具有灵活可配置逻辑模块的微控制器,其特征在于,包括:

2.根据权利要求1所述的微控制器,其特征在于,所述可配置逻辑模块根据一个寄存器位、两个来自mcu输入引脚的输入端口和两个来自其他可配置逻辑模块的值分别在所述两个查找表中获得两个输出值并输出到相应寄存器或mcu输出引脚。

3.根据权利要求1所述的微控制器,其特征在于,还包括:同步时钟选择器,所述同步时钟选择器接收微控制器的内部时钟或外部模块输入的时钟并选择性输出到所述两个触发器的时钟端口。

4.根据权利要求1所述的微控制器,其特征在于,所述微控制器包括至少三个可配置逻辑模块。

技术总结

本申请公开了一种具有灵活可配置逻辑模块的微控制器,包括:多个可配置逻辑模块,每个具有两个查找表、一个来自寄存器输出、两个来自MCU输入引脚、两个来自其他可配置逻辑模块的输出,根据输入端口的值在查找表中获得输出端口对应的值;多个输入复用器,两个分别选择来自MCU输入引脚的信号,并输入到查找表,两个分别选择来自其他可配置逻辑模块的输出,并输入到查找表;两个触发器,其数据端口各自接收查找表的两个输出端口,时钟端口各自接收微控制器的内部时钟或外部模块输入的时钟;两个输出复用器,选择查找表直接输出或触发器输出;两个解复用器,选择查找表输出到哪个MCU输出引脚。本申请可以满足微控制器高速通讯应用场景。

技术研发人员:请求不公布姓名

受保护的技术使用者:灵动集成电路南京有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!