带隙基准电路、芯片模组及电子设备的制作方法

本申请涉及集成电路,尤其涉及一种带隙基准电路、芯片模组及电子设备。

背景技术:

1、在模拟电路和混合模拟电路中,带隙基准电路作为一个基础单元,发挥着极其重要的作用。带隙基准电路的作用是产生一个不随温度、电源电压、工艺等参数变化而变化的参考电压。而带隙基准电路的精度直接影响带隙基准电路所在芯片的许多参数。因此,带隙基准电路的设计对于芯片来说十分重要。

2、然而,现有技术中多数采用单独的运算放大器实现带隙基准电路这一环路的控制,这会导致带隙基准电路的电路结构复杂。同时,运算放大器的失调电压会降低带隙基准电路输出的参考电压的精度。

技术实现思路

1、本申请提供一种带隙基准电路、芯片模组及电子设备,能够简化电路结构,以及提高参考电压的精度。

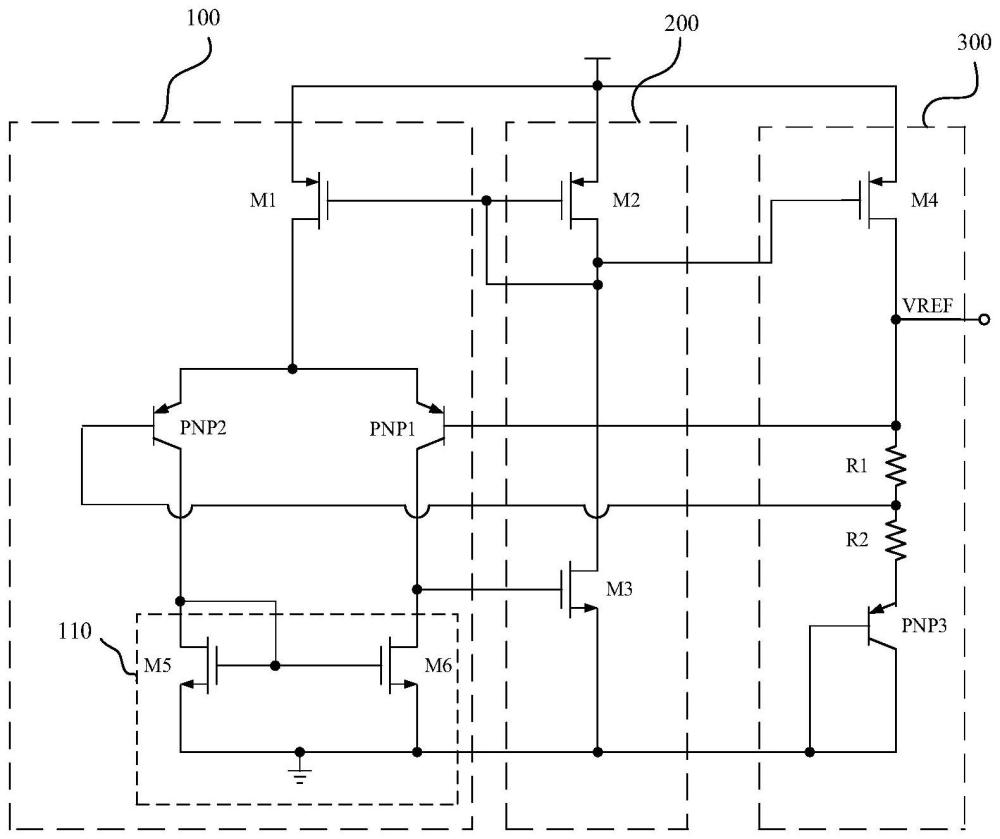

2、第一方面,本申请提供一种带隙基准电路,该带隙基准电路包括:第一级放大单元、第二级放大单元和第三级放大单元;第一级放大单元包括:第一晶体管、第一三极管、第二三极管以及负载组件;第二级放大单元包括:第二晶体管和第三晶体管;第三级放大单元包括:第四晶体管、第一电阻和p型三极管;

3、第一晶体管的源极、第二晶体管的源极和第四晶体管的源极均用于接入电源电压,第一晶体管的栅极分别与第二晶体管的栅极、第二晶体管的漏极、第三晶体管的第一端和第四晶体管的栅极电连接,第一三极管的第一端和第二三极管的第一端电连接,第一晶体管的漏极电连接于第一三极管的第一端和第二三极管的第一端之间,第一三极管的第二端电连接于第四晶体管的漏极与第一电阻的第一端之间,第一三极管的第三端与负载组件的第一端电连接,第二三极管的第二端电连接于第一电阻的第二端和p型三极管的发射极之间,第二三极管的第三端与负载组件的第二端电连接,第三晶体管的控制端电连接于第一三极管的第三端与负载组件的第一端之间,第四晶体管的漏极与第一电阻的第一端电连接,第一电阻的第二端和p型三极管的发射极电连接,负载组件的第三端、第三晶体管的第二端、p型三极管的基极和p型三极管的集电极均接地;

4、第四晶体管的漏极与第一电阻的第一端之间的节点输出参考电压,第二三极管的导通电流与第三三极管的导通电流被设置为相等。

5、通过第一方面提供的带隙基准电路,通过第一级放大单元、第二级放大单元和第三级放大单元可以构成完整的负反馈环路。采用第一三极管和第二三极管作为第一级放大单元的差分输入对,使带隙基准电路不用单独设置运算放大器,简化带隙基准电路的电路结构,以及能够避免因设置运算放大器而引入运算放大器的失调电压对参考电压精度的影响。如此,能够提高参考电压的精度。此外,在第三级放大单元中,通过第一电阻与p型三极管电连接,使负温度系数电压和正温度系数电压能够结合。这样,能够得到零温度系数的参考电压,使参考电压不随温度的变化而变化。

6、在一种可能的设计中,第一三极管和第二三极管均为p型三极管。

7、在一种可能的设计中,第一三极管的尺寸与第二三极管的尺寸之间的比值为m:1,m大于或等于1。

8、在一种可能的设计中,第三级放大单元还包括:第二电阻;第二电阻的第一端与第一电阻的第二端电连接,第二电阻的第二端与p型三极管的发射极电连接。

9、在一种可能的设计中,第二电阻的阻值大于或等于第一电阻的阻值。

10、在一种可能的设计中,第一晶体管的宽长比与第四晶体管的宽长比之间的比值为2:1。

11、在一种可能的设计中,负载组件包括:第五晶体管和第六晶体管;第五晶体管的第一端分别与第二三极管的第三端、第五晶体管的控制端和第六晶体管的控制端电连接,第六晶体管的第一端与第一三极管的第三端电连接,第五晶体管的第二端和第六晶体管的第二端均接地。

12、在一种可能的设计中,第三晶体管为n型晶体管。

13、第二方面,本申请提供一种芯片模组,包括:上述第一方面及第一方面任一种可能的设计中的带隙基准电路。

14、上述第二方面以及上述第二方面的各可能的设计中所提供的,其有益效果可以参见上述第一方面和第一方面的各可能的实施方式所带来的有益效果,在此不再赘述。

15、第三方面,本申请提供一种电子设备,包括:上述第二方面中的芯片模组。

16、上述第三方面以及上述第三方面的各可能的设计中所提供的,其有益效果可以参见上述第一方面和第一方面的各可能的实施方式所带来的有益效果,在此不再赘述。

技术特征:

1.一种带隙基准电路,其特征在于,所述带隙基准电路包括:第一级放大单元、第二级放大单元和第三级放大单元;所述第一级放大单元包括:第一晶体管、第一三极管、第二三极管以及负载组件;所述第二级放大单元包括:第二晶体管和第三晶体管;所述第三级放大单元包括:第四晶体管、第一电阻和p型三极管;

2.根据权利要求1所述的电路,其特征在于,所述第一三极管和所述第二三极管均为p型三极管。

3.根据权利要求2所述的电路,其特征在于,所述第一三极管的尺寸与所述第二三极管的尺寸之间的比值为m:1,m大于或等于1。

4.根据权利要求1-3任一项所述的电路,其特征在于,所述第三级放大单元还包括:第二电阻;所述第二电阻的第一端与所述第一电阻的第二端电连接,所述第二电阻的第二端与所述p型三极管的发射极电连接。

5.根据权利要求4所述的电路,其特征在于,所述第二电阻的阻值大于或等于所述第一电阻的阻值。

6.根据权利要求1-3任一项所述的电路,其特征在于,所述第一晶体管的宽长比与所述第四晶体管的宽长比之间的比值为2:1。

7.根据权利要求1-3任一项所述的电路,其特征在于,所述负载组件包括:第五晶体管和第六晶体管;所述第五晶体管的第一端分别与所述第二三极管的第三端、所述第五晶体管的控制端和所述第六晶体管的控制端电连接,所述第六晶体管的第一端与所述第一三极管的第三端电连接,所述第五晶体管的第二端和所述第六晶体管的第二端均接地。

8.根据权利要求1所述的电路,其特征在于,所述第三晶体管为n型晶体管。

9.一种芯片,其特征在于,包括:如权利要求1-8任一项所述的带隙基准电路。

10.一种电子设备,其特征在于,包括:如权利要求9所述的芯片。

技术总结

本申请提供一种带隙基准电路、芯片模组及电子设备。该带隙基准电路包括:第一级放大单元、第二级放大单元和第三级放大单元。通过第一级放大单元、第二级放大单元和第三级放大单元可以构成完整的负反馈环路。采用第一三极管和第二三极管作为第一级放大单元的差分输入对,使带隙基准电路不用单独设置运算放大器,简化带隙基准电路的电路结构,以及能够避免因设置运算放大器而引入运算放大器的失调电压对参考电压精度的影响。如此,能够提高参考电压的精度。此外,在第三级放大单元中,通过第一电阻与P型三极管电连接,使负温度系数电压和正温度系数电压能够结合。这样,能够得到零温度系数的参考电压,使参考电压不随温度的变化而变化。

技术研发人员:雷新宇,王佳煜

受保护的技术使用者:上海南芯半导体科技股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!