偏置电流生成电路及芯片的制作方法

本公开的实施例涉及集成电路,具体地涉及一种偏置电流生成电路及芯片。

背景技术:

1、在模拟集成电路中,偏置电流是电路正常工作的重要参考源,因此偏置电流生成电路是模拟芯片不可缺少的模块。

2、图1是一种偏置电流生成电路100的示例性电路图。nmos晶体管mn1、mn2和电阻r1构成负反馈环路,使a点电位为va=vgs_mn1,b点电位为vb=vgs_mn1+vgs_mn2,其中,vgs_mn1为nmos晶体管mn1的栅源电压,vgs_mn2为nmos晶体管mn2的栅源电压。因此流过nmos晶体管mn1的电流为电阻r0上的电流ir0=[vcc–(vgs_mn1+vgs_mn2)]/r0,流过nmos晶体管mn2和pmos晶体管mp1的电流均为电阻r1上的电流ir1=vgs_mn1/r1。pmos晶体管mp2与pmos晶体管mp1构成电流镜电路,且pmos晶体管mp2的宽长比与pmos晶体管mp1的宽长比成比例,假设该比例为k,则pmos晶体管mp2的漏源电流为ip=k*vgs_mn1/r1,即为电路100产生的偏置电流,该偏置电流为pmos偏置电流信号。

3、但是,通常的模拟集成电路中,pmos偏置电流信号和nmos偏置电流信号都是必须的,而上述偏置电流生成电路100仅能提供pmos偏置电流,无法生成nmos偏置电流信号。

技术实现思路

1、本公开的实施例的目的是提供一种偏置电流生成电路及芯片,在可同时产生pmos偏置电流信号和nmos偏置电流信号的情况下,不产生多余的电流支路,减少电流的浪费,且保证电路结构简单。

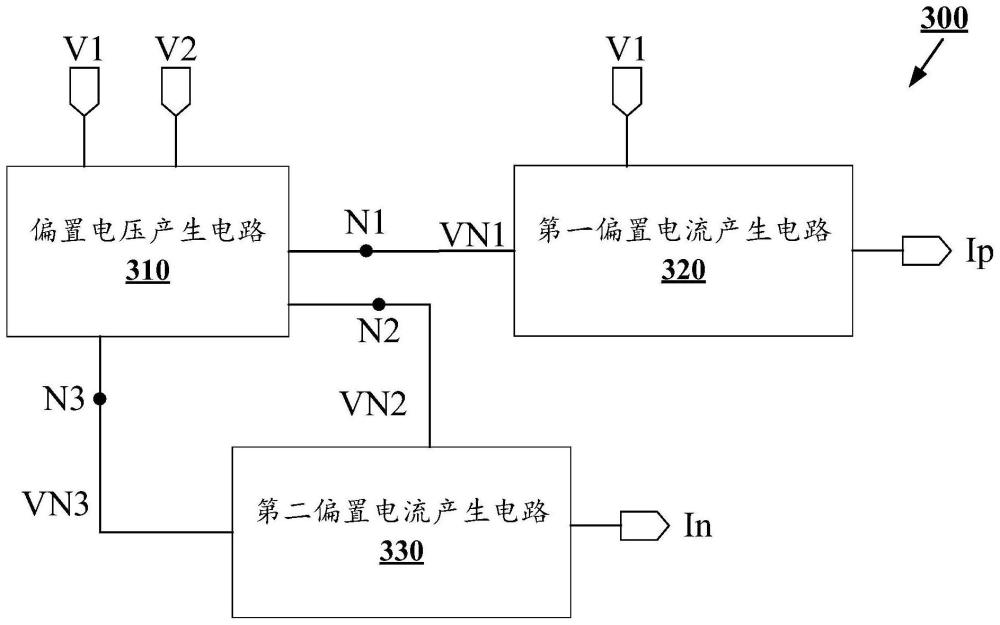

2、为了实现上述目的,本公开实施例的第一方面,提供了一种偏置电流生成电路,包括:偏置电压产生电路、第一偏置电流产生电路与第二偏置电流产生电路。其中,所述偏置电压产生电路被配置为生成第一偏置电压信号、第二偏置电压信号与第三偏置电压信号,并经由第一节点将所述第一偏置电压信号提供至所述第一偏置电流产生电路、经由第二节点将所述第二偏置电压信号提供至所述第二偏置电流产生电路以及经由第三节点将所述第三偏置电压信号提供至所述第二偏置电流产生电路;所述第一偏置电流产生电路被配置为根据所述第一偏置电压信号,产生pmos偏置电流信号;所述第二偏置电流产生电路被配置为根据所述第二偏置电压信号与所述第三偏置电压信号,产生nmos偏置电流信号。

3、在本公开的一些实施例中,所述偏置电压产生电路包括:第一电阻器、第一晶体管、第二晶体管、第三晶体管与第二电阻器。其中,所述第一电阻器的第一端耦接第一电压端,所述第一电阻器的第二端耦接所述第二晶体管的第二极、所述第三晶体管的控制极以及所述第二节点;所述第一晶体管的控制极耦接所述第一晶体管的第二极与所述第一节点,所述第一晶体管的第一极耦接所述第一电压端;所述第二晶体管的控制极耦接所述第三晶体管的第一极、所述第二电阻器的第一端以及所述第三节点,所述第二晶体管的第一极耦接第二电压端;所述第三晶体管的第二极耦接所述第一节点;所述第二电阻器的第二端耦接所述第二电压端。

4、在本公开的一些实施例中,所述第一偏置电流产生电路包括:第四晶体管。其中,所述第四晶体管的控制极耦接所述第一节点,所述第四晶体管的第一极耦接第一电压端,所述第四晶体管的第二极耦接所述pmos偏置电流信号的输出端。

5、在本公开的一些实施例中,所述第二偏置电流产生电路包括:第五晶体管。其中,所述第五晶体管的控制极耦接所述第二节点,所述第五晶体管的第一极耦接所述第三节点,所述第五晶体管的第二极耦接所述nmos偏置电流信号的输出端。

6、在本公开的一些实施例中,所述第一晶体管为pmos晶体管,所述第二晶体管与所述第三晶体管均为nmos晶体管。

7、在本公开的一些实施例中,所述第四晶体管为pmos晶体管,且所述第四晶体管的宽长比与所述第一晶体管的宽长比成比例。

8、在本公开的一些实施例中,所述第五晶体管为nmos晶体管,且所述第五晶体管的宽长比与所述第三晶体管的宽长比成比例。

9、在本公开的一些实施例中,所述第三晶体管与所述第五晶体管构成差分对管,所述nmos偏置电流信号为将所述差分对管的尾电流源信号按照所述第五晶体管与所述第三晶体管之间的宽长比的比例分配得到。

10、在本公开的一些实施例中,所述nmos偏置电流信号与所述第三偏置电压信号正相关。

11、根据本公开的第二方面,提供了一种芯片。该芯片包括根据本公开的第一方面所述的偏置电流生成电路。

12、本公开的实施例的其它特征和优点将在随后的具体实施方式部分予以详细说明。

技术特征:

1.一种偏置电流生成电路,其特征在于,包括:偏置电压产生电路、第一偏置电流产生电路与第二偏置电流产生电路,

2.根据权利要求1所述的偏置电流生成电路,其特征在于,所述偏置电压产生电路包括:第一电阻器、第一晶体管、第二晶体管、第三晶体管与第二电阻器,

3.根据权利要求2所述的偏置电流生成电路,其特征在于,所述第一偏置电流产生电路包括:第四晶体管,

4.根据权利要求2所述的偏置电流生成电路,其特征在于,所述第二偏置电流产生电路包括:第五晶体管,

5.根据权利要求2所述的偏置电流生成电路,其特征在于,所述第一晶体管为pmos晶体管,所述第二晶体管与所述第三晶体管均为nmos晶体管。

6.根据权利要求3所述的偏置电流生成电路,其特征在于,所述第四晶体管为pmos晶体管,且所述第四晶体管的宽长比与所述第一晶体管的宽长比成比例。

7.根据权利要求4所述的偏置电流生成电路,其特征在于,所述第五晶体管为nmos晶体管,且所述第五晶体管的宽长比与所述第三晶体管的宽长比成比例。

8.根据权利要求7所述的偏置电流生成电路,其特征在于,所述第三晶体管与所述第五晶体管构成差分对管,所述nmos偏置电流信号为将所述差分对管的尾电流源信号按照所述第五晶体管与所述第三晶体管之间的宽长比的比例分配得到。

9.根据权利要求8所述的偏置电流生成电路,其特征在于,所述nmos偏置电流信号与所述第三偏置电压信号正相关。

10.一种芯片,其特征在于,包括:根据权利要求1-9中任一项所述的偏置电流生成电路。

技术总结

本公开的实施例提供一种偏置电流生成电路及芯片。偏置电流生成电路包括:偏置电压产生电路、第一偏置电流产生电路与第二偏置电流产生电路。偏置电压产生电路被配置为生成第一偏置电压信号、第二偏置电压信号与第三偏置电压信号,并经由第一节点将所述第一偏置电压信号提供至所述第一偏置电流产生电路、经由第二节点将所述第二偏置电压信号提供至所述第二偏置电流产生电路以及经由第三节点将所述第三偏置电压信号提供至所述第二偏置电流产生电路;第一偏置电流产生电路被配置为根据所述第一偏置电压信号,产生PMOS偏置电流信号;第二偏置电流产生电路被配置为根据所述第二偏置电压信号与所述第三偏置电压信号,产生NMOS偏置电流信号。

技术研发人员:张利地

受保护的技术使用者:圣邦微电子(北京)股份有限公司

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!