一种LDO过流保护电路的制作方法

本发明及ldo电路,具体为一种ldo过流保护电路。

背景技术:

1、低压差稳压器(英语:low-dropout regulator,ldo),又称低压差线性稳压器、低压降稳压器,是线性直流稳压器的一种,用途同是提供稳定的直流电压电源。相比于一般线性直流稳压器,低压差稳压器能于更小输出输入电压差的情况下工作。

2、在高温环境下,ldo(low dropout voltage regulator,低压差线性稳压器)的功率管过流检测变大的现象,这通常与多个因素相关。功率晶体管(如mosfet或bjt)的性能在高温下会发生变化。mosfet的阈值电压会随温度升高而降低,这可能导致在相同栅压下,流过晶体管的电流增大。其作用机制如下:

3、(1)基准电压漂移:

4、ldo内部用于比较的基准电压可能会随温度变化而发生漂移。如果基准电压在高温下升高,那么为了维持输出电压的稳定,误差放大器可能会增加对功率晶体管的控制信号,导致流过晶体管的电流增大。

5、(2)误差放大器增益变化:

6、误差放大器的增益也可能受温度影响。在高温下,如果误差放大器的增益降低,那么它对输出电压变化的响应速度会变慢,可能导致在检测到过流之前,电流已经超过了设定的阈值。

技术实现思路

1、本发明要解决的技术问题是提供一种ldo过流保护电路,以解决背景技术所述现有技术的不足。

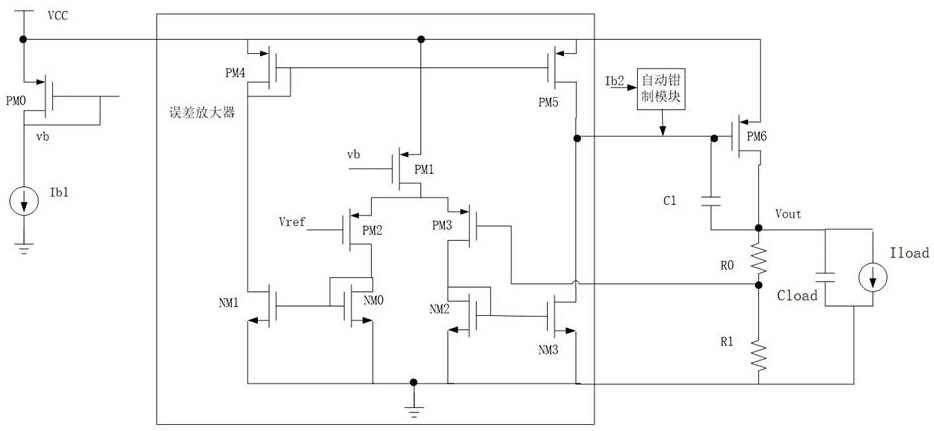

2、为解决上述技术问题,本发明的实施例提供如下技术方案:一种ldo过流保护电路,包括误差放大器、功率管和反馈电阻模块,所述误差放大器输出端连接功率管和反馈电阻模块,所述功率管和反馈电阻模块反馈信号输出端连接误差放大器;所述功率管和反馈电阻模块包括pmos管pm6、补偿电容c1以及反馈电阻r0、r1,所述pmos管pm6栅极连接误差放大器控制信号输出端,所述pmos管pm6漏极连接电阻r0一端,所述电阻r0另一端连接电阻r1一端,所述电阻r1另一端接地,所述pmos管pm6漏极与接地端之间连接负载,所述pmos管pm6栅极与漏极之间连接补偿电容c1,所述pmos管pm6源极连接电源vcc;所述误差放大器控制信号输出端设置自动钳制电路,所述自动钳制电路输出端与误差放大器控制信号输出端同时连接pmos管pm6栅极。

3、进一步的,所述自动钳制电路包括pmos管pm7、pm8、pm9,电阻r1、r2,以及nmos管nm8a、nm8b、nm9a、nm9b;所述pmos管pm7、pm8、pm9源极连接电源vdd;所述pmos管pm7漏极连接nmos管nm8a漏极,所述pmos管pm8漏极连接nmos管nm8b、nm9a漏极,所述nm8a栅极连接nm8b栅极,所述nm9a栅极连接nm9b栅极,所述nm8a、nm8b、nm9a、nm9b源极接地,所述nm9b漏极通过电阻r2连接电源vdd,所述pmos管pm7漏极和源极连接电阻r1。

4、进一步的,所述nm9b漏极连接pmos管pm9的衬底电压端vsub,所述pm9漏极连接所述pmos管pm6栅极为功率管和反馈电阻模块提供钳位电压。

5、进一步的,所述pmos管pm7栅极与源极连接。

6、进一步的,所述nmos管nm8a、nm9a栅极与漏极相连。

7、进一步的,所述pmos管pm9栅极与漏极连接。

8、进一步的,所述电源vcc连接pmos管pm0源极,所述pm0栅极与漏极连接,所述pm0漏极接地。

9、进一步的,所述误差放大器为运算放大器芯片。

10、进一步的,所述pm0栅极与漏极连接。

11、进一步的,所述pmos管pm8栅极输入外部控制信号。

12、本发明的上述技术方案的有益效果如下:

13、本发明通过在传统ldo电路的误差放大器输出端设置自动钳制模块,可以在ldo电路工作在高温状态下时,通过自动钳制模块输出钳位电压,抑制误差放大器在高温下增加对功率晶体管的控制信号增加的趋势,最终避免因温度升高造成ldo电路功率晶体管电流增大的问题。

技术特征:

1.一种ldo过流保护电路,包括误差放大器、功率管和反馈电阻模块,所述误差放大器输出端连接功率管和反馈电阻模块,所述功率管和反馈电阻模块反馈信号输出端连接误差放大器;所述功率管和反馈电阻模块包括pmos管pm6、补偿电容c1以及反馈电阻r0、r1,所述pmos管pm6栅极连接误差放大器控制信号输出端,所述pmos管pm6漏极连接电阻r0一端,所述电阻r0另一端连接电阻r1一端,所述电阻r1另一端接地,所述pmos管pm6漏极与接地端之间连接负载,所述pmos管pm6栅极与漏极之间连接补偿电容c1,所述pmos管pm6源极连接电源vcc;其特征在于,所述误差放大器控制信号输出端设置自动钳制电路,所述自动钳制电路输出端与误差放大器控制信号输出端同时连接pmos管pm6栅极。

2.根据权利要求1所述的ldo过流保护电路,其特征在于,所述自动钳制电路包括pmos管pm7、pm8、pm9,电阻r1、r2,以及nmos管nm8a、nm8b、nm9a、nm9b;所述pmos管pm7、pm8、pm9源极连接电源vdd;所述pmos管pm7漏极连接nmos管nm8a漏极,所述pmos管pm8漏极连接nmos管nm8b、nm9a漏极,所述nm8a栅极连接nm8b栅极,所述nm9a栅极连接nm9b栅极,所述nm8a、nm8b、nm9a、nm9b源极接地,所述nm9b漏极通过电阻r2连接电源vdd,所述pmos管pm7漏极和源极连接电阻r1。

3.根据权利要求2所述的ldo过流保护电路,其特征在于,所述nm9b漏极连接pmos管pm9的衬底电压端vsub,所述pm9漏极连接所述pmos管pm6栅极为功率管和反馈电阻模块提供钳位电压。

4.根据权利要求2所述的ldo过流保护电路,其特征在于,所述pmos管pm7栅极与源极连接。

5.根据权利要求2所述的ldo过流保护电路,其特征在于,所述nmos管nm8a、nm9a栅极与漏极相连。

6.根据权利要求2所述的ldo过流保护电路,其特征在于,所述pmos管pm9栅极与漏极连接。

7.根据权利要求1所述的ldo过流保护电路,其特征在于,所述电源vcc连接pmos管pm0源极,所述pm0漏极接电流源ib1,所述pm0栅极与pm1栅极相连。

8.根据权利要求1所述的ldo过流保护电路,其特征在于,所述误差放大器为运算放大器芯片。

9.根据权利要求7所述的ldo过流保护电路,其特征在于,所述pm0栅极与漏极连接。

10.根据权利要求2所述的ldo过流保护电路,其特征在于,所述pmos管pm8栅极输入外部控制信号。

技术总结

本发明涉及LDO电路技术领域,具体提供一种LDO过流保护电路,包括误差放大器、功率管和反馈电阻模块,误差放大器输出端连接功率管和反馈电阻模块,功率管和反馈电阻模块反馈信号输出端连接误差放大器;误差放大器控制信号输出端设置自动钳制电路,自动钳制电路输出端与误差放大器控制信号输出端同时连接功率管和反馈电阻模块的功率晶体管栅极。本发明通过在传统LDO电路的误差放大器输出端设置自动钳制模块,可以在LDO电路工作在高温状态下时,通过自动钳制模块输出钳位电压,抑制误差放大器在高温下增加对功率晶体管的控制信号增加的趋势,最终避免因温度升高造成LDO电路功率晶体管电流增大的问题。

技术研发人员:请求不公布姓名,请求不公布姓名,请求不公布姓名

受保护的技术使用者:成都瓴科微电子有限责任公司

技术研发日:

技术公布日:2024/9/5

- 还没有人留言评论。精彩留言会获得点赞!