一种带隙基准电路、片上系统、芯片以及电子设备的制作方法

本申请涉及集成电路,尤其是一种带隙基准电路、片上系统、芯片以及电子设备。

背景技术:

1、相关技术中,带隙基准电路一般采用电路内部的运算放大器的直接输出作为基准电压输出。这种带隙基准电路因为电路抗噪声性能较差,容易出现电路的基准电压由于噪声的干扰而出现偏差。因此,相关技术中仍存在需要解决的技术问题。

技术实现思路

1、本申请的目的在于至少一定程度上解决现有技术中存在的技术问题之一。

2、为此,本申请实施例的一个目的在于提供一种带隙基准电路、片上系统以及芯片,本方案可以减少电路输出基准电压的噪声。

3、为了达到上述技术目的,本申请实施例所采取的技术方案包括:一种带隙基准电路,包括基准采集单元、隔离缓冲单元以及运算输出单元;所述运算输出单元与所述隔离缓冲单元连接;所述隔离缓冲单元与所述基准采集单元连接;所述运算输出单元与所述基准采集单元。

4、另外,根据本实用新型中上述实施例的一种带隙基准电路,还可以有以下附加的技术特征:

5、进一步地,本申请实施例中,所述运算输出单元包括运算放大器以及晶体管子电路;所述运算放大器的输入端与所述晶体管子电路连接;所述运算放大器的输出端作为所述运算输出单元的输出端。

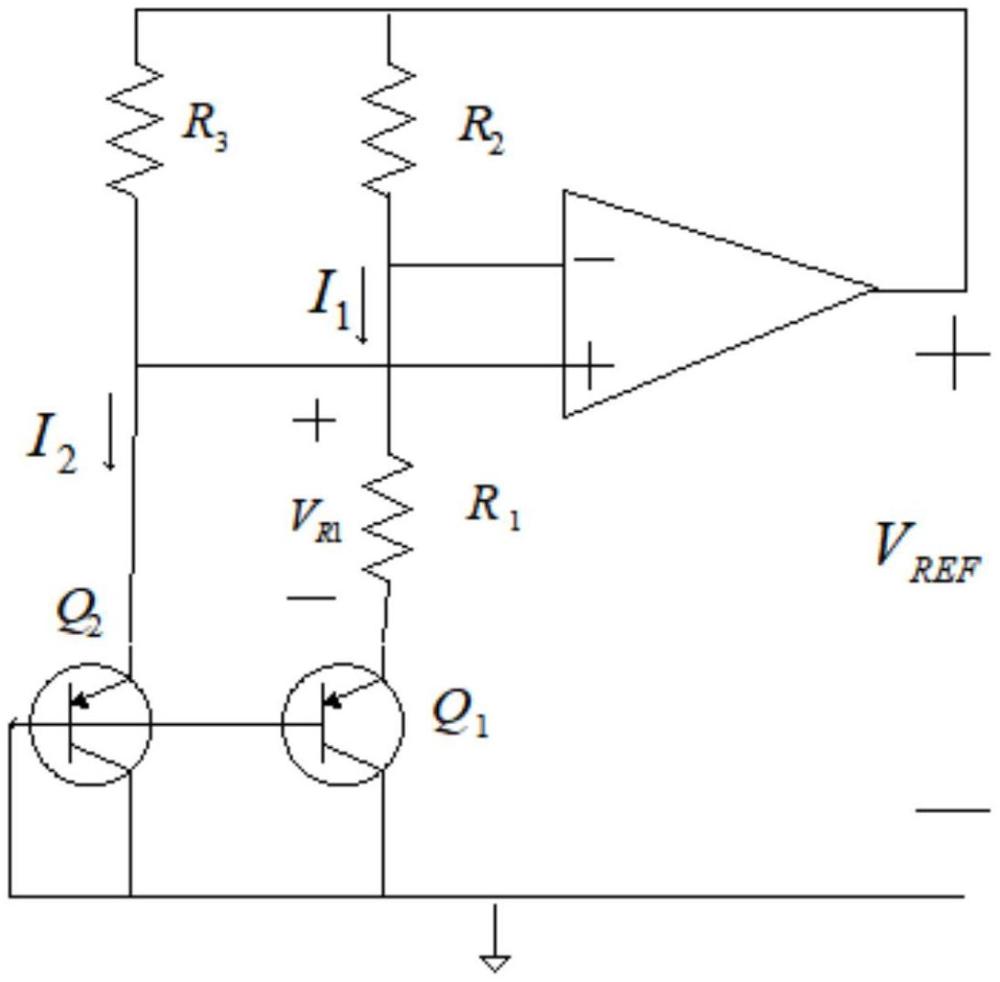

6、进一步地,本申请实施例中,所述晶体管子电路包括第一三极管、第二三极管、第一电阻、第二电阻以及第三电阻;所述第二三极管的集电极以及所述第三电阻的一端与所述运算放大器的反相输入端连接,所述第二三极管的发射极以及所述第二三极管的基极接地;所述第一三极管的集电极与所述第一电阻的一端连接,所述第一三极管的发射极以及所述第一三极管的基极接地;所述第一电阻的另一端以及所述第二电阻的一端与所述运算放大器的同相输入端连接;所述第二电阻的另一端以及所述第三电阻的另一端与所述第一电源连接。

7、进一步地,本申请实施例中,所述隔离缓冲单元包括第一mos管、第二mos管以及电源模块;所述第一mos管的栅极连接,第一mos管的源极与所述第二mos管的漏极连接;所述第一mos管的源极与所述电源模块连接;所述第二mos管的栅极作为所述隔离缓冲单元的输入端,并与所述运算输出单元连接;所述第二mos管的源极与所述第一电源连接;所述第一mos管的漏极作为所述隔离缓冲单元的输出端,并与所述基准采集单元连接。

8、进一步地,本申请实施例中,所述电源模块包括电压源或者电源子电路。

9、进一步地,本申请实施例中,所述电源子电路包括电流源、第一电容、第三mos管以及第四mos管;所述第三mos管的漏极、所述第三mos管的栅极、所述电流源的一端与所述第一电容的一端连接;所述第四mos管的栅极以及所述第四mos管的漏极与所述第三mos管的源极连接;所述第四mos管的源极与所述第一电源连接。

10、进一步地,本申请实施例中,所述第一mos管、所述第二mos管、所述第三mos管以及所述第四mos管均为p沟道mos管。

11、另一方面,本申请实施例还提供一种片上系统,包括如前面任一项所述的一种带隙基准电路以及外围电路。

12、另一方面,本申请实施例还提供一种芯片,包括前面所述的片上系统。

13、另一方面,本申请实施例还提供一种电子设备,包括前面所述的芯片。

14、本申请的优点和有益效果将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本申请的实践了解到:

15、本申请可以在运算输出单元与基准采集单元之间设置隔离缓冲单元,使运算输出单元的输出不作为直接输出的基准电压,而是使算输出单元的输出经过隔离缓冲单元以及基准采集单元后转换为基准电压。本申请可以通过隔离缓冲单元减少电路中的噪声对于输出的基准电压的影响,从而提高电路输出基准电压的准确度。

技术特征:

1.一种带隙基准电路,其特征在于,包括:

2.根据权利要求1所述的带隙基准电路,其特征在于,所述运算输出单元包括运算放大器以及晶体管子电路;所述运算放大器的输入端与所述晶体管子电路连接;所述运算放大器的输出端作为所述运算输出单元的输出端;所述晶体管子电路包括第一三极管、第二三极管、第一电阻、第二电阻以及第三电阻;所述第二三极管的集电极以及所述第三电阻的一端与所述运算放大器的反相输入端连接,所述第二三极管的发射极以及所述第二三极管的基极接地;所述第一三极管的集电极与所述第一电阻的一端连接,所述第一三极管的发射极以及所述第一三极管的基极接地;所述第一电阻的另一端以及所述第二电阻的一端与所述运算放大器的同相输入端连接;所述第二电阻的另一端以及所述第三电阻的另一端与第一电源连接。

3.根据权利要求1所述的带隙基准电路,其特征在于,所述隔离缓冲单元包括第一mos管、第二mos管以及电源模块;所述第一mos管的栅极连接,第一mos管的源极与所述第二mos管的漏极连接;所述第一mos管的源极与所述电源模块连接;所述第二mos管的栅极作为所述隔离缓冲单元的输入端,并与所述运算输出单元连接;所述第二mos管的源极与第一电源连接;所述第一mos管的漏极作为所述隔离缓冲单元的输出端,并与所述基准采集单元连接。

4.根据权利要求3所述的带隙基准电路,其特征在于,所述电源模块包括电压源或者电源子电路。

5.根据权利要求4所述的带隙基准电路,其特征在于,所述电源子电路包括电流源、第一电容、第三mos管以及第四mos管;所述第三mos管的漏极、所述第三mos管的栅极、所述电流源的一端与所述第一电容的一端连接;所述第四mos管的栅极以及所述第四mos管的漏极与所述第三mos管的源极连接;所述第四mos管的源极与所述第一电源连接。

6.根据权利要求5所述的带隙基准电路,其特征在于,所述第一mos管、所述第二mos管、所述第三mos管以及所述第四mos管均为p沟道mos管。

7.根据权利要求1所述的带隙基准电路,其特征在于,所述基准采集单元包括第四电阻,所述第四电阻的一端与所述隔离缓冲单元连接;所述第四电阻的另一端与所述运算输出单元连接;所述第四电阻的一端的电压作为所述基准采集单元的输出电压。

8.一种片上系统,其特征在于,包括如权利要求1-7任一项所述带隙基准电路以及外围电路。

9.一种芯片,其特征在于,包括如权利要求8所述片上系统。

10.一种电子设备,其特征在于,包括如权利要求9所述的芯片。

技术总结

本申请公开了一种带隙基准电路、片上系统以及芯片。其中,带隙基准电路包括基准采集单元、隔离缓冲单元以及运算输出单元;所述运算输出单元与所述隔离缓冲单元连接;所述隔离缓冲单元与所述基准采集单元连接;所述运算输出单元与所述基准采集单元。本申请可以在运算输出单元与基准采集单元之间设置隔离缓冲单元,隔离缓冲单元可以减少基准采集单元受到电路噪声,从而提高电路输出基准电压的准确度。本申请可广泛应用于集成电路技术领域。

技术研发人员:伍星,陈剑锋,苏奎任

受保护的技术使用者:广州众诺微电子有限公司

技术研发日:20240705

技术公布日:2025/4/7

- 还没有人留言评论。精彩留言会获得点赞!