一种DSP处理器与FPGA周期性通信的防帧错方法与流程

一种dsp处理器与fpga周期性通信的防帧错方法

技术领域

1.本发明属于数字信号处理领域,具体涉及一种dsp处理器与fpga周期性通信的防帧错方法。

背景技术:

2.在dsp+fpga系统中的指令状态通信中,通常dsp周期性给fpga发送数据帧,而fpga则是按照另一周期或者非周期,向下一级转发指令状态数据。即使协议上规定dsp和fpga的周期相同,但是实际上,两个芯片的周期也不是绝对的相同,存在些微差别。经过差别累计,若fpga接收到指令状态数据后,不采取保护措施,直接转发至下一级,容易产生数据帧错乱的现象。为了解决此问题,本发明在fpga内通过2级缓存fifo+ram的方式,实现数据完整帧的保护,确保fpga转发的数据是完整的数据帧,不会出现拼帧现象。

技术实现要素:

3.本发明提供了一种dsp处理器与fpga周期性通信的防帧错方法,确保fpga转发的是完整的数据帧,不会出现拼帧现象,

4.一种dsp处理器与fpga周期性通信的防帧错方法,所述方法包括:

5.步骤1、在fpga内产生2级缓存,第一级缓存是fifo,第二级缓存是ram;

6.步骤2、dsp写入fpga的数据,以dsp emif接口时钟作为fifo的写时钟,直接将数据写入fifo,写完之后,dsp发送完成标志;

7.步骤3:fpga接收到完成标志,并且确认ram不处于读状态时,从fifo中读出数据,写入ram中;

8.步骤4:fpga按照某一固定周期或者非周期,直接从ram中读取数据,发送至下一级应用。

9.进一步地,所述步骤1中,fifo是异步fifo,其深度由dsp写入fpga的最大数据个数决定,fifo的写时钟为dsp emif接口时钟,fifo的读时钟与ram的读写时钟为同一个时钟信号;ram的深度与fifo的读端口深度一致,读写数据位宽与fifo的读数据位宽一致。

10.进一步地,所述步骤2中,若每次通信的数据长度是固定的,那么当fifo中的数据个数等于固定数据长度时,fpga即判断dsp已完成写操作;若数据长度不固定,由dsp发送完成标志。

11.本发明有益效果如下:

12.本发明适用于dsp+fpga系统中的指令状态数据通信。在通常情况下,dsp按照某一周期给fpga发送数据,而fpga则是按照另一周期或者非周期,向下一级转发指令状态数据。即使协议上规定dsp和fpga的周期相同,但是实际上,两个芯片的周期也不是绝对的相同,存在些微差别。经过周期差别累计,若fpga接收到指令状态数据后,不采取保护措施,直接转发至下一级,容易产生数据帧错乱的现象。为了解决此问题,本发明在fpga内通过2级缓存fifo+ram的方式,实现数据完整帧的保护,确保fpga转发的数据是完整的数据帧,不会出

现拼帧现象。

附图说明

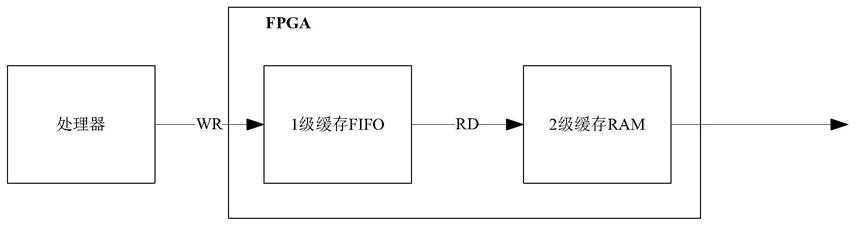

13.图1为本发明2级缓存连接图;

14.图2为1级缓存fifo与2级缓存ram之间的读时序关系;

具体实施方式

15.本发明具体实施方式中提供了一种dsp处理器与fpga周期性通信的防帧错方法,所述方法包括:步骤1、在fpga内,产生2级缓存,第一级缓存是fifo,第二级缓存是ram;步骤2、dsp写入fpga的数据,以dsp emif接口时钟作为fifo的写时钟,直接写入fifo。写完之后,dsp发送完成标志;步骤3:fpga接收到完成标志,并且确认ram不处于读状态时,从fifo中读出数据,写入ram中。步骤4:fpga按照某一固定周期或者非周期,直接从ram中读取数据,发送至下一级应用;

16.下面就结合图1到图2对上述方法中的各步骤进行具体介绍。

17.步骤1:在fpga内产生2级缓存,第一级缓存是fifo,第二级缓存是ram,如图1所示。其中fifo是异步fifo,其深度由dsp写入fpga的最大数据个数决定,fifo的读写数据位宽可以不同,读写时钟也可以不同,但是fifo的写时钟必须是dsp emif接口时钟,fifo的读时钟与ram的读写时钟必须是同一个时钟信号。ram的深度与fifo的读端口深度一致,读写数据位宽与fifo的读数据位宽一致。

18.步骤2:dsp写入fpga的数据,以dsp emif接口时钟作为fifo的写时钟,直接写入fifo。若每次通信的数据长度是固定的,那么当fifo中的数据个数等于固定数据长度时,fpga即判断dsp已完成写操作;若数据长度不固定,可以由dsp发送完成标志。

19.步骤3:fpga判断dsp完成写数据操作,并且确认ram不处于读状态时,从fifo中读出数据,直接写入ram中。结合图2详细说明fifo读操作与ram之间的时序关系。由于fifo自身特性,有效数据使能(对应从fifo中读取的有效数据)fifo_valid比读使能fifo_rden延迟2个时钟周期,ram的写使能ram_wren(对应写地址)比fifo_valid延迟1个时钟周期,为了避免ram读写冲突,再预留1个时钟周期,因此至少预留4个时钟周期。也就是说,若fpga需要从ram中读取n个数据,那么ram处于读状态的时间就是(n+4)个时钟周期。即在这(n+4)个时钟周期内,即使fpga判断dsp完成写数据操作,也不允许从fifo中读取数据。等待(n+4)个时钟后,再从fifo中读取数据,写入ram。需要说明的是,dsp的周期一般是ms级的,而(n+4)时钟周期是us级,因此在等待(n+4)个时钟周期的这段时间内,dsp不会发送下一帧数据。这种操作机制,即保证了ram中存储数据帧的完整性,同时也避免了出现ram读写地址冲突情况的发生。

20.步骤4:fpga按照自身周期需求,直接从ram中读取数据,发送至下一级应用;ram的读操作仅受fpga自身周期时序的限制,无需考虑ram是否会出现读写地址冲突的情况。

21.上述具体实施方式仅用于解释和说明本发明的技术方案,但并不能构成对权利要求的保护范围的限定。本领域技术人员应当清楚,在本发明的技术方案的基础上做任何简单的变形或替换而得到的新的技术方案,均将落入本发明的保护范围之内。

技术特征:

1.一种dsp处理器与fpga周期性通信的防帧错方法,其特征在于,所述方法包括:步骤1、在fpga内产生2级缓存,第一级缓存是fifo,第二级缓存是ram;步骤2、dsp写入fpga的数据,以dsp emif接口时钟作为fifo的写时钟,直接将数据写入fifo,写完之后,dsp发送完成标志;步骤3:fpga接收到完成标志,并且确认ram不处于读状态时,从fifo中读出数据,写入ram中;步骤4:fpga按照某一固定周期或者非周期,直接从ram中读取数据,发送至下一级应用。2.根据权利要求1所述的一种dsp处理器与fpga周期性通信的防帧错方法,其特征在于,所述步骤1中,fifo是异步fifo,其深度由dsp写入fpga的最大数据个数决定,fifo的写时钟为dsp emif接口时钟,fifo的读时钟与ram的读写时钟为同一个时钟信号;ram的深度与fifo的读端口深度一致,读写数据位宽与fifo的读数据位宽一致。3.根据权利要求1所述的一种dsp处理器与fpga周期性通信的防帧错设计方法,其特征在于,所述步骤2中,若每次通信的数据长度是固定的,那么当fifo中的数据个数等于固定数据长度时,fpga即判断dsp已完成写操作;若数据长度不固定,由dsp发送完成标志。

技术总结

本发明公开一种DSP处理器与FPGA周期性通信的防帧错方法,在DSP+FPGA系统中的指令状态通信中,通常DSP按照某一周期给FPGA发送数据帧,而FPGA则是按照另一周期或者非周期,向下一级转发指令状态数据。即使协议上规定DSP和FPGA的周期相同,但是实际上,两个芯片的周期也不是绝对的相同,存在些微差别。经过差别累计,若FPGA接收到指令状态数据后,不采取保护措施,直接转发至下一级,容易产生数据帧错乱的现象。为了解决此问题,本发明在FPGA内通过2级缓存FIFO+RAM的方式,实现数据完整帧的保护,确保FPGA转发的数据是完整的数据帧,不会出现拼帧现象。出现拼帧现象。出现拼帧现象。

技术研发人员:王茂义 王洋

受保护的技术使用者:北京华航无线电测量研究所

技术研发日:2020.11.05

技术公布日:2022/5/6

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1